Fターム[4M104EE05]の内容

半導体の電極 (138,591) | 絶縁膜(特徴のあるもの) (8,323) | 絶縁膜の適用位置 (3,412) | 電極上 (625)

Fターム[4M104EE05]の下位に属するFターム

パシベーション膜 (200)

Fターム[4M104EE05]に分類される特許

121 - 140 / 425

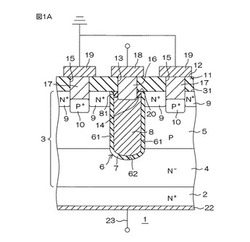

半導体装置

【課題】ゲート電極とのコンタクトのためのコンタクトホールの形成時に、ゲート電極が深く掘り下げられることを防止できる半導体装置を提供すること。

【解決手段】ゲートトレンチ6を有するエピタキシャル層3に、ボディ領域5、ドレイン領域4、ソース領域9およびボディコンタクト領域10を形成する。ゲートトレンチ6には、ゲート電極8を埋設する。エピタキシャル層3には、層間絶縁膜11を積層する。ゲート電極8と層間絶縁膜11との間には、エピタキシャル層3とはエッチングレートの異なる材料からなるエッチングストッパ層14を介在させる。そして、エッチングにより、ゲート電極8およびボディコンタクト領域10それぞれとのコンタクトのための、ゲートコンタクトホール13およびソースコンタクトホール15を同時に形成する。ゲートコンタクトホール13は、平面視でエッチングストッパ層14と重なるように形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の小型化が進んでも半導体装置の信頼性向上を図ることができる技術を提供する。

【解決手段】本発明の技術的思想は、積層形成される窒化シリコン膜SN1〜SN3のそれぞれの膜厚を一定値ではなく、トータルの総膜厚を一定に保ちながら、上層の窒化シリコン膜SN3から下層の窒化シリコン膜SN1にしたがって膜厚を薄くするように構成している点にある。これにより、歪シリコン技術を実効あらしめる窒化シリコン膜SN1〜SN3の引張応力を確保しながら、特に、最上層の窒化シリコン膜SN3の埋め込み特性を改善できる。

(もっと読む)

電気的固体装置、電気光学装置、および電気的固体装置の製造方法

【課題】アルミニウム系の配線材料として用いた場合でも、十分な耐ヒロック性に備えるとともに、ドライエッチングを適用でき、さらに、レジストマスクを剥離する際に用いる剥離液によって、配線がエッチングされることのない電気的固体装置、電気光学装置、および電気的固体装置の製造方法を提供すること。

【解決手段】電気光学装置100において、素子基板10上に走査線3aなどの配線を形成するにあたって、ネオジウムを2atm%未満含有するアルミニウム合金膜を用いるとともに、走査線3aの上面および側面を酸化して表面保護膜31aを形成する。このため、走査線3aは、耐ヒロック性が高いとともに、表面保護膜31a、31eによってアルカリ性の剥離液から保護される。

(もっと読む)

半導体装置

【課題】薄膜トランジスタにおいて、ソース/ドレイン領域に高抵抗不純物領域(HRD

または低濃度不純物領域)を自己整合的に形成する方法を提供する。

【解決手段】ゲイト電極105上面にマスク106を残し、比較的低い電圧でポーラスな

第1の陽極酸化膜107をゲイト電極の側面に成長させる。この陽極酸化膜をマスクとし

てゲイト絶縁膜104’をエッチングする。必要に応じては比較的高い電圧でバリア型の

第2の陽極酸化膜108をゲイト電極の側面および上面に形成する。第1の陽極酸化膜を

選択的にエッチングする。不純物ドーピングをおこなうと、ゲイト電極の下部にはドーピ

ングされず、ゲイト電極に近い領域では、不純物濃度の低い高抵抗領域111,112と

なる。ゲイト電極から遠い領域では、不純物濃度の高い低抵抗領域110,113となる

。

(もっと読む)

半導体装置の製造方法

【課題】銅を主成分とするコンタクトプラグを有する半導体装置において、コンタクトプラグに隆起が発生することを防止する。

【解決手段】第1の層間絶縁膜102に、金属シリサイド層101に到達するコンタクトホール103を形成する工程(c)と、コンタクトホールの底面及び側壁に、高融点金属膜104を形成する工程(d)と、高融点金属膜上に、銅を主成分とする金属膜106Aを形成し、コンタクトホール内に、高融点金属膜を介して、金属膜が埋め込まれてなるコンタクトプラグ107を形成する工程(e)と、第1の層間絶縁膜及びコンタクトプラグの上に、第2の層間絶縁膜108を形成する工程(f)とを備え、工程(f)は、コンタクトプラグの表面に存在する酸素ガスを除去する工程(f1)と、工程(f1)の後に、コンタクトプラグの表面に存在する酸素ガスが除去された状態で、第2の層間絶縁膜を形成する工程(f2)とを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】電流が、縦方向、横方向、そして縦方向と連続的に流れる半導体装置において

縦方向並びに横方向の電流経路に係る電気抵抗を低減し、高効率、高性能な半導体装置を実現する。

【解決手段】本発明の半導体装置は、半導体基板の表面側にドレインを共有するMOS構造が2つ形成され、かつ、半導体基板の裏面側のN+型ドレイン層7の内部に、一方のMOS構造のドレイン領域から他方のMOS構造のドレイン領域まで、延在して形成された複数の堀状の開口部4を有する。堀状の開口部4はN+型ドレイン層7の内部の、N+型ドレイン層7とN−型エピ層8の境界近傍まで、深く形成されている。そして、堀状の開口部4の中には裏面電極5と電気的に接続された、N+型ドレイン層7に比べて抵抗の低い、金属電極6が形成されている。

(もっと読む)

表示装置

【課題】表示装置を駆動させるためのトランジスタとして量子細線を用いた場合に、小型

化および薄型化をより図ることが可能な表示装置を提供する。

【解決手段】この表示装置100は、ガラス基板6の表面から上方(矢印Z1方向側)に

向かって延びるように形成された凸部71(72)を含むゲート電極7と、ゲート電極7

の凸部71(72)と平面的に見て重なるとともに、ゲート電極7上にゲート絶縁膜8を

介して形成される量子細線9と、量子細線9にそれぞれ接続されるソース電極11および

ドレイン電極12とを含む量子細線トランジスタ5を備える。また、ゲート電極7の凸部

71(72)と量子細線9との間の距離t1は、ゲート電極7の凸部71(72)以外の

部分と量子細線9との間の距離t2よりも小さい。

(もっと読む)

半導体装置

【課題】 構造を複雑化させることなく、サージ電流によるスイッチング素子の破壊を抑制することのできる半導体装置を提供すること。

【解決手段】 半導体装置1において、活性層5に第1ディープトレンチ6を形成する。アクティブ領域9には、ボディ領域11とドリフト領域12とを形成する。ボディ領域11の表層部には、ソース領域13を形成する。ドリフト領域12の表層部には、ドレイン領域15を形成する。また、フィールド領域10には、第2ディープトレンチ20を形成する。第2ディープトレンチ20の内側面を1対のシリコン酸化膜21で被覆し、その内部をポリシリコン22で埋め尽くす。そして、第1、第2ディープトレンチ6,20間の第1半導体領域23をソース領域13に電気的に接続する。また、第2ディープトレンチ20外の第2半導体領域28をドレイン領域15に電気的に接続する。

(もっと読む)

半導体装置の作製方法

【課題】絶縁膜中にコンタクトホールを形成せずに、絶縁膜の表面と裏面の間に導電領域を形成することを課題とする。

【解決手段】基板上の半導体素子及び第1の電極上に絶縁膜を形成し、絶縁膜中に第1の加速電圧で第1のイオンを添加して、絶縁膜中の第1の深さに第1の欠陥の多い領域を形成し、第1の加速電圧とは異なる第2の加速電圧で、第2のイオンを添加して、絶縁膜中の第1の深さとは異なる第2の深さに第2の欠陥の多い領域を形成し、第1及び第2の欠陥の多い領域上に、金属元素を含む導電材料を形成し、第1及び第2の欠陥の多い領域のうちの上方の領域から下方の領域に、金属元素を拡散させることにより、絶縁膜中に、第1の電極と、金属元素を含む導電材料とを電気的に接続する導電領域を形成する半導体装置の作製方法に関する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ゲート絶縁膜破壊が抑制された半導体装置を提供する。

【解決手段】ゲート電極給電用シリコンピラー5の表面を覆うゲート電極8と重なる位置に設けられたコンタクトホール13を備え、コンタクトホール13には、コンタクトホール13の底部から少なくともゲート電極8の上面よりも上方まで充填されたゲートリフトポリシリコン14と、ゲートリフトポリシリコン14上に配置されたゲートコンタクト15とが設けられていることを特徴とする半導体装置を採用する。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、弊害なく半導体装置の高耐圧化、耐圧安定化、電極の電位安定化、耐圧保持領域のシュリンクなどに活用される半絶縁性膜を形成することができる半導体装置の製造方法を提供することを目的とする。

【解決手段】

半導体基板表面にP型領域を形成する工程と、該P型領域上にAl電極を形成する工程と、該Al電極と接し、Alと比較してSiと反応しづらい物質からなる層間膜を形成する工程と、該層間膜上にSiを含有する半絶縁性膜を形成する工程とを備えることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】急峻な不純物濃度のプロファイルを有するソース領域およびドレイン領域を形成することのできる半導体装置の製造方法を提供する。

【解決手段】この半導体装置の製造方法は、半導体基板の表面近傍に不純物を注入して不純物注入領域を形成する工程と、前記半導体基板にエッチングを施すことにより前記不純物注入領域の底部よりも深い溝を形成し、前記不純物注入領域を分断してソース領域およびドレイン領域を形成する工程と、前記溝の内部にSi系単結晶をエピタキシャル成長させてエピタキシャル結晶層を形成する工程と、前記エピタキシャル結晶層の上部にゲート絶縁膜およびゲート電極を形成する工程と、を含む。

(もっと読む)

パターン形成方法

【課題】無駄を省いた状態で、所望とする微細なパターンに電着による膜が形成できるようにする。

【解決手段】まず、容器151内に電着液152を収容し、電着液152の中で、白金からなる対向電極153に基板101の金属パターン104形成面を対向させて配置する。この状態で、定電圧源154により、対向電極153に正電圧を印加し、シード層102に負電圧を印加する。ここで、金属パターン105に必要な配線を接続することで、シード層102に対する負電圧の印加を行う。このようなカチオン電着により、金属パターン104および金属パターン105の露出している面(上面)に、電着液152中の電着成分が付着(析出)し、電着絶縁膜106が形成される。

(もっと読む)

半導体装置の製造方法

【課題】下地となるサイドウォールにダメージを与えることなく外側のサイドウォールを除去可能で、これにより狭スペース化したゲート電極間に自己整合的にソース/ドレインに達する接続孔を形成できる半導体装置の製造方法を提供する。

【解決手段】半導体基板1上にゲート構造体Aを形成し、さらにノンドープシリコン系絶縁膜11と、不純物ドープ窒化シリコン膜13と順に成膜する。これらの膜11,13を異方性エッチングし、ゲート構造体Aの側壁に第1サイドウォール11aと第2サイドウォール13aとを形成する。半導体基板1の表面側にソース/ドレイン拡散層15を形成し、アルカリエッチング溶液を用いたウェットエッチングにより、第2サイドウォール13aを選択的に除去する。半導体基板1上に層間絶縁膜を形成し、第1サイドウォール11aをストッパとしたエッチングにより層間絶縁膜にソース/ドレイン拡散層15に達する接続孔を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】活性化のための光照射による急速加熱を行っても、ゲート電極と層間絶縁膜の界面剥離や、被照射物に損傷を与えることのない半導体装置の製造方法及び半導体装置を提供すること。

【解決手段】基板2上に半導体層5を形成する工程、半導体層5上にゲート絶縁膜6を形成する工程、ゲート絶縁膜6上に高融点金属膜を成膜する工程、高融点金属膜上にチタン膜を成膜する工程、高融点金属膜及びチタン膜をパターン状に加工し、ゲート電極8を形成する工程、ゲート電極8をマスクとして半導体層5に不純物を注入する工程、ゲート電極8を覆うように層間絶縁膜9を形成する工程、層間絶縁膜9上に半導体層5より高い融点を有する金属からなる光吸収膜10を形成する工程、光吸収膜10に光を照射し、光吸収膜10が光を吸収することで生じた熱により半導体層5中の不純物を活性化する工程とを具備することを特徴とする。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】SiCウェハの表面状態の悪化を抑制しつつ、十分な熱処理を実施することが可能な半導体装置の製造方法、および当該製造方法により製造されることにより、優れた特性を有する半導体装置を提供する。

【解決手段】半導体装置としてのMOSFETの製造方法は、炭化珪素からなるウェハ3を準備する工程と、ウェハ3を加熱することにより、活性化アニールを実施する活性化アニール工程とを備えている。そして、活性化アニール工程では、ウェハ3の主面に沿って、SiC基板61が配置された状態で、ウェハ3が加熱される。

(もっと読む)

金属相含有酸化インジウム焼結体及びその製造方法

【課題】スパッタ時のノジュールの発生を抑制できる酸化インジウムスパッタリングターゲット並びに酸化インジウム焼結体及びその製造方法を提供する。

【解決手段】酸化インジウムスパッタリングターゲットを酸化インジウム相と金属相を有する酸化インジウム焼結体により構成する。また、インジウム化合物と金属微粒子を混合した粉末又はインジウム化合物と金属酸化物微粒子を混合した粉末を放電プラズマ焼結することにより、酸化インジウム相と金属相を有する酸化インジウム焼結体を製造する。

(もっと読む)

半導体装置およびその製造方法

【課題】金属ゲートを形成した後に形成される絶縁膜中の水素の影響を抑制して、しきい値電圧Vthを所望の値(例えば0.3V)以下にすることを可能にする。

【解決手段】半導体基板11上に第1絶縁膜41が形成され、第1絶縁膜41に溝部42が形成され、溝部42の第1絶縁膜41側の半導体基板11上にサイドウォールスペーサ31が形成され、溝部42内にゲート絶縁膜21を介してゲート電極22が形成され、ゲート電極22の両側の半導体基板11にエクステンション領域23,24を介してソース・ドレイン領域25,26が形成され、第1絶縁膜41上にゲート電極22上を被覆する第2絶縁膜43を有し、サイドウォールスペーサ31は水素の通過を阻止する絶縁膜からなり、ゲート電極22上に水素の通過を阻止する水素バリア膜33が形成され、水素バリア膜33はゲート電極22上の周囲でサイドウォールスペーサ31と接続されている。

(もっと読む)

半導体加工方法

【課題】high−k膜/メタルゲート構造を有する半導体素子のドライエッチングにおいて、メタルゲート部分を垂直にエッチングする。

【解決手段】減圧処理室204と、該減圧処理室に処理ガスを供給するガス供給手段と、前記減圧処理室内に、半導体基板を載置して保持する試料台205と、前記減圧処理室に供給された処理ガスに高周波エネルギを供給してプラズマを生成するプラズマ生成手段を備え、生成したプラズマにより前記半導体基板にプラズマエッチング処理を施す半導体加工方法において、前記試料台上に、HfあるいはZrを含む高誘電率絶縁膜、TiあるいはTaを含む仕事関数制御金属導体膜、およびレジストを順次形成した半導体基板206を載置し、前記レジストを用いて前記導体膜をエッチング加工するに際して、前記試料台にオンオフ変調された基板バイアス電圧を印加する。

(もっと読む)

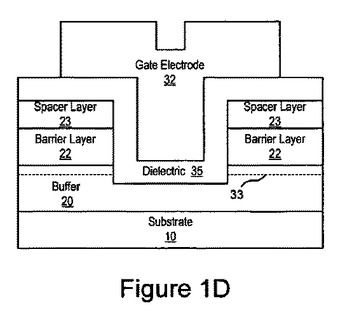

常時オフ半導体デバイスおよびその作製方法

常時オフ半導体デバイスが提供される。III族窒化物バッファ層が提供される。III族窒化物バリア層がIII族窒化物バッファ層上に設けられる。非伝導性スペーサ層がIII族窒化物バリア層上に設けられる。III族窒化物バリア層およびスペーサ層がエッチングされてトレンチを形成する。トレンチはバリア層を貫いて延びてバッファ層の一部を露出させる。誘電体層がスペーサ層上およびトレンチ内に形成され、ゲート電極が誘電体層上に形成される。半導体デバイスの形成に関連する方法も提供される。  (もっと読む)

(もっと読む)

121 - 140 / 425

[ Back to top ]