Fターム[4M104EE05]の内容

半導体の電極 (138,591) | 絶縁膜(特徴のあるもの) (8,323) | 絶縁膜の適用位置 (3,412) | 電極上 (625)

Fターム[4M104EE05]の下位に属するFターム

パシベーション膜 (200)

Fターム[4M104EE05]に分類される特許

41 - 60 / 425

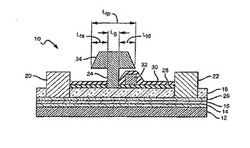

トランジスタデバイスおよび高電子移動度トランジスタ(HEMT)

【課題】デバイス利得、帯域幅、および動作周波数が増加するトランジスタを提供する。

【解決手段】第1のスペーサ層28が、ゲート電極24とドレイン電極22との間、およびゲート電極24とソース電極20との間の活性領域の表面の少なくとも一部の上にある。ゲート電極24は、ソース電極20とドレイン電極22に向かって延在する一般的にT字型の頂部34を備える。フィールドプレート32は、スペーサ層28の上であって、ゲート頂部34の少なくとも1つの区域のオーバーハングの下にある。第2のスペーサ層30は、ゲート電極24とドレイン電極22との間、およびゲート電極24とソース電極20との間にある第1のスペーサ層28の少なくとも一部の上と、フィールドプレート32の少なくとも一部の上に形成される。少なくとも1つの導電性経路が、フィールドプレート32をソース電極20またはゲート電極24に電気的に接続する。

(もっと読む)

半導体発光素子及びその製造方法

【課題】高輝度化を図ることができる半導体発光素子及びその製造方法を提供する。

【解決手段】実施形態に係る半導体発光素子は、構造体と、第1電極層と、電極層と、無機膜と、を備える。構造体は、第1導電形の第1半導体層と、第2導電形の第2半導体層と、第1半導体層と第2半導体層との間に設けられた発光層と、を有する。電極層は、構造体の第2半導体層の側に設けられる。電極層は、金属部と、複数の開口部と、を有する。金属部は、第1半導体層から第2半導体層に向かう方向に沿った厚さが10nm以上、100nm以下である。開口部は、前記方向に沿って金属部を貫通し、円相当直径が10nm以上、5μm以下である。無機膜は、前記方向に沿った厚さが20nm以上、200nm以下で、金属部の表面及び開口部の内面を覆うように設けられ、発光層から放出される光に対して透過性を有する。

(もっと読む)

半導体装置の作製方法

【課題】本発明は、薄膜トランジスタのソース領域やドレイン領域へのコンタクトを確実

にした半導体装置を提供するものである。

【解決手段】本発明における半導体装置において、半導体層上の絶縁膜およびゲイト電極

上に形成された第1の層間絶縁膜と、前記第1の層間絶縁膜の上に形成された第2の層間

絶縁膜と、前記第2の層間絶縁膜、前記第1の層間絶縁膜、および前記絶縁膜に設けられ

たコンタクトホールとを有する。前記第1の絶縁層の膜厚は、前記積層の絶縁膜の合計膜

厚の1/3以下に形成する。

(もっと読む)

表示装置及び電子機器

【課題】可撓性を有する基板上に有機化合物を含む層を有する素子が設けられた半導体装置を歩留まり高く作製することを課題とする。

【解決手段】基板上に剥離層を形成し、剥離層上に、無機化合物層、第1の導電層、及び有機化合物を含む層を形成し、有機化合物を含む層及び無機化合物層に接する第2の導電層を形成して素子形成層を形成し、第2の導電層上に第1の可撓性を有する基板を貼りあわせた後、剥離層と素子形成層とを剥す半導体装置の作製方法である。

(もっと読む)

半導体装置

【課題】nチャネル型電界効果トランジスタとpチャネル型電界効果トランジスタを有する半導体装置において、nチャネル型電界効果トランジスタ、pチャネル型電界効果トランジスタ共にドレイン電流特性に優れた半導体装置を実現する。

【解決手段】nチャネル型電界効果トランジスタ10と、pチャネル型電界効果トランジスタ30とを有する半導体装置において、nチャネル型電界効果トランジスタ10のゲート電極15を覆う応力制御膜19には、膜応力が引張応力側の膜を用いる。pチャネル型電界効果トランジスタ30のゲート電極35を覆う応力制御膜39には、膜応力が、nチャネル型トランジスタ10の応力制御膜19より、圧縮応力側の膜を用いることにより、nチャネル型、pチャネル型トランジスタの両方のドレイン電流の向上が期待できる。このため、全体としての特性を向上させることができる。

(もっと読む)

化合物半導体装置

【課題】高耐圧特性と低オン抵抗特性とを両立した化合物半導体装置を実現する。

【解決手段】化合物半導体装置を、キャリア走行層2及びキャリア供給層3を含む窒化物半導体積層構造4と、窒化物半導体積層構造の上方に設けられたソース電極5及びドレイン電極6と、窒化物半導体積層構造の上方のソース電極とドレイン電極との間に設けられたゲート電極7と、ゲート電極とドレイン電極との間に少なくとも一部が設けられたフィールドプレート8と、窒化物半導体積層構造の上方に形成された複数の絶縁膜9、10とを備えるものとし、フィールドプレートとドレイン電極との間でゲート電極の近傍よりも複数の絶縁膜の界面の数を少なくする。

(もっと読む)

半導体装置

【課題】動作特性に対する信頼性を向上させることができる半導体装置を提供する。

【解決手段】シリコンを含む基板7と、前記基板7上に設けられた積層体6と、を有する半導体装置1であって、前記積層体6は、少なくとも前記積層体6の側壁の前記基板側にフッ素を含む抑制領域13を有している。前記抑制領域13は、基板7上に設けられた絶縁膜2の前記側壁側に設けられ、フッ素濃度は、チャネル領域11のフッ素濃度よりも高い。

(もっと読む)

半導体装置の製造方法

【課題】複数の金属層が積層された電極構造を有する半導体装置を容易に製造することができる半導体装置の製造方法を提供する。

【解決手段】 半導体層と、その半導体層の表面に形成されている第1金属層と、第1金属層の少なくとも一部が露出するように第1金属層に隣接する位置に形成されている絶縁層とを有する半導体基板を用いて、半導体装置を製造する方法であって、露出部分の第1金属層の表面及び絶縁層の表面に、絶縁層に対するよりも第1金属層に対する接着性が高い第2金属層を形成する工程と、第1金属層の表面に形成された第2金属層を残存させながら、絶縁層の表面に形成された第2金属層を絶縁層から剥離する工程を有する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において、異なる膜特性を有する絶縁膜に形成されるコンタクト形状の制御性を向上させる。

【解決手段】半導体基板に素子領域を形成し、半導体基板の第1の領域上に、第1の絶縁膜を形成し、半導体基板の第2の領域上に、膜応力及びコンタクトの形成の際のエッチング加工時のエッチングレートが、第1の絶縁膜と異なる第2の絶縁膜を形成し、少なくとも第2の絶縁膜において、コンタクトが形成されるコンタクト領域に選択的にUV光を照射し、UV光を照射した後、第1の絶縁膜及び前記第2の絶縁膜をエッチングして前記コンタクトを形成する。

(もっと読む)

シングルゲートまたはマルチゲートフィールドプレート製造

【課題】誘電性材料に与えるダメージの少ない乾式または湿式エッチングプロセスを用いることなく、フィールドプレートされたデバイスを実現できるシングルゲートまたはマルチゲートフィールドプレートの製造方法を提供する。

【解決手段】電界効果トランジスタ10は、ソースオーミックコンタクト12と、ドレインオーミックコンタクト14、ゲートコンタクト16、および活性領域18を含む。(1)デバイスの真性および外因性領域に誘電性材料を堆積または成長させ、(2)乾式または湿式エッチングプロセス、あるいはリフトオフプロセスで誘電性材料をパターニングし、(3)パターニングされた誘電性材料上にフィールドプレートを蒸着させるステップを包含する方法。

(もっと読む)

半導体装置の製造方法

【課題】タングステン膜を使用した部分の抵抗を低減した半導体装置を提供する。

【解決手段】半導体装置の製造方法では、基板内に設けた開口部内、又は基板上にタングステン膜を形成する。タングステン膜の形成後、エッチバック又はエッチングを行う前にタングステン膜に対してアニール処理を行う。これにより、タングステン膜の結晶状態を変化させる。

(もっと読む)

半導体装置

【課題】本発明は、高電界での耐圧を確保でき、かつ絶縁破壊を抑制できる終端構造を有する半導体装置の提供を目的とする。

【解決手段】本発明にかかる半導体装置は、ドリフト領域2表面において、平面視でSBD電極5を囲むように形成された、リセス構造3と、リセス構造3底面内に形成され、SBD電極5と接続された、ガードリング注入層4と、リセス構造3に沿って、少なくともリセス構造3を覆って形成された、保護膜7と、保護膜7に沿って、保護膜7上に形成された、半絶縁膜20とを備え、半絶縁膜20は、リセス構造3が囲む領域の内側においてSBD電極5と接続される接続部21と、リセス構造3が囲む領域の外側においてドリフト領域2と接続される接続部22とを備える。

(もっと読む)

半導体装置の製造方法

【課題】n型FET及びp型FET(電界効果トランジスター)のうち、一方のFETの電流駆動能力の低下を抑制し、他方のFETの電流駆動能力の向上を図る。

【解決手段】n型FET及びp型FETを覆うように、第1の膜を形成する工程と、その後、p型(n型)FET上の前記第1の膜に対して、イオン注入法によって選択的に不純物を打ち込む工程とを有し、n型(p型)FETのチャネル形成領域には、n型(p型)FET上の前記第1の膜によって、主として、n型(p型)FETのゲート電極のゲート長方向に引張(圧縮)応力が発生しており、不純物を打ち込む工程によって、前記p型(n型)FETのチャネル形成領域に発生する引張(圧縮)応力は、n型(p型)FETのチャネル形成領域に発生する引張(圧縮)応力よりも小さくなっている。

(もっと読む)

半導体装置

【課題】本発明は、薄膜トランジスタのソース領域やドレイン領域へのコンタクトを確実

にした半導体装置を提供するものである。

【解決手段】本発明における半導体装置において、半導体層上の絶縁膜およびゲイト電極

上に形成された第1の層間絶縁膜と、前記第1の層間絶縁膜の上に形成された第2の層間

絶縁膜と、前記第2の層間絶縁膜、前記第1の層間絶縁膜、および前記絶縁膜に設けられ

たコンタクトホールとを有する。前記第1の絶縁層の膜厚は、前記積層の絶縁膜の合計膜

厚の1/3以下に形成する。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、製造工程の煩雑化および製造プロセスの長時間化を抑制できると共に、量産性に優れた半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法では、ゲート電極7上に、積層膜19を形成する。そして、層間絶縁膜8形成後、層間絶縁膜8等に対してエッチング処理を施す。これにより、ソース領域3およびp+ベースコンタクト領域5が底面から露出した第1のコンタクトホール12を形成すると同時に、積層膜19が底面から露出した第2のコンタクトホール13を形成する。ここで、当該エッチング処理は、積層膜19のエッチングレートが層間絶縁膜8のエッチングレートよりも遅くなるエッチング条件により、実施する。

(もっと読む)

半導体装置の製造方法及び基板処理装置

【課題】 半導体装置の製造工程を簡略化させ、金属元素含有膜の酸化を抑制させる。

【解決手段】 金属元素含有膜及び金属元素含有膜上に形成された絶縁膜を備える基板を処理室内に搬入し、処理室内に設けられた基板支持部により支持する工程と、励起状態の水素と励起状態の窒素のいずれか又は両方と、励起状態の酸素と、を含む反応ガスを処理室内で基板上に供給して基板を処理する工程と、基板を処理室内から搬出する工程と、を有する。

(もっと読む)

化合物半導体装置

【課題】窒化物化合物半導体装置において、ゲートリーク電流を抑制する。

【解決手段】化合物半導体装置20は、基板21と、前記基板上方に形成された窒化物半導体よりなるキャリア走行層22を含む半導体積層構造と、前記半導体積層構造上方に形成されたゲート電極26、ソース電極27A、ドレイン電極27Bと、前記半導体積層構造上方であって、ゲート電極とソース電極の間、及び、ゲート電極とドレイン電極との間に形成された絶縁膜28と、前記絶縁膜のうち、ゲート電極とソース電極の間、及びゲート電極とドレイン電極の間に形成された開口と、前記開口に埋め込まれたアルミナ膜29と、を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】コンタクトホールの形状制御が容易な半導体装置の製造方法を得る。

【解決手段】実施形態の半導体装置の製造方法は、基板1上にゲート絶縁膜2、ゲート電極3,4、第1ハードマスク5を形成し、第1ハードマスクをパターンニングして第1マスクを形成し、これをマスクにゲート電極及びゲート絶縁膜を基板が露出するまでエッチングしラインパターンを形成し、露出した基板及び第1マスクを覆うようにライナー膜7を形成する。更にライナー膜に覆われたラインパターンの間隙を有機系絶縁膜で埋め込み、少なくともライナー膜が露出するまで有機系絶縁膜を平坦化してその上に第2ハードマスク9を形成し、第2ハードマスクを第1マスクと交差するようにパターンニングして第2マスクを形成し、第1及び第2マスクをマスクに有機系絶縁膜をライナー膜が露出するまでエッチングしてコンタクトホールを形成する。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成する半導体装置の作製方法を提供することを目的の一とする。

【解決手段】絶縁表面上に、酸化物半導体層と、酸化物半導体層と接するソース電極およびドレイン電極と、を形成し、ソース電極上およびドレイン電極上にそれぞれ絶縁層を形成し、酸化物半導体層、ソース電極、ドレイン電極および絶縁層上にゲート絶縁層を形成し、ゲート絶縁層上に導電層を形成し、導電層を覆うように絶縁膜を形成し、導電層におけるソース電極またはドレイン電極と重畳する領域の少なくとも一部が露出するように絶縁膜を加工し、導電層の露出した領域をエッチングして、ソース電極とドレイン電極に挟まれた領域の少なくとも一部と重畳するゲート電極を自己整合的に形成する半導体装置の作製方法である。

(もっと読む)

窒化物半導体装置

【課題】歩留まり良く形成することができ、高い信頼性を保つことができる、高周波特性が優れた窒化物半導体装置を提供する。

【解決手段】ソース電極5とドレイン電極6との間の電子供給層4上に、電子供給層とショットキー接触する浮遊電極8を配置し、この浮遊電極上に絶縁膜9を介してゲート電極7を配置する。特に絶縁膜を強誘電体材料とすると好ましい。

(もっと読む)

41 - 60 / 425

[ Back to top ]