Fターム[4M104EE05]の内容

半導体の電極 (138,591) | 絶縁膜(特徴のあるもの) (8,323) | 絶縁膜の適用位置 (3,412) | 電極上 (625)

Fターム[4M104EE05]の下位に属するFターム

パシベーション膜 (200)

Fターム[4M104EE05]に分類される特許

141 - 160 / 425

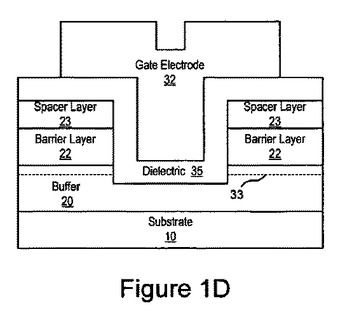

常時オフ半導体デバイスおよびその作製方法

常時オフ半導体デバイスが提供される。III族窒化物バッファ層が提供される。III族窒化物バリア層がIII族窒化物バッファ層上に設けられる。非伝導性スペーサ層がIII族窒化物バリア層上に設けられる。III族窒化物バリア層およびスペーサ層がエッチングされてトレンチを形成する。トレンチはバリア層を貫いて延びてバッファ層の一部を露出させる。誘電体層がスペーサ層上およびトレンチ内に形成され、ゲート電極が誘電体層上に形成される。半導体デバイスの形成に関連する方法も提供される。  (もっと読む)

(もっと読む)

半導体装置、及びその製造方法

【課題】トランジスタ特性を劣化させずに形成される小型の半導体装置、及びその製造方法を提供する。

【解決手段】半導体基板と、前記半導体基板上に形成されるゲート絶縁膜と、前記半導体基板上に前記ゲート絶縁膜を介して形成されるゲート電極と、前記ゲート電極の上面に形成される第1窒化シリコン膜と、前記ゲート電極の側面に形成される保護絶縁膜と、前記保護絶縁膜の側面に形成される第2窒化シリコン膜と、前記保護絶縁膜の上面に形成され、その底面が前記第1窒化シリコン膜の底面よりも上部に形成される第3窒化シリコン膜とを備える。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】CMP(Chemical Mechanical Polishing)ストッパ膜を終点検出膜として利用しつつ、CMPによる平坦化精度を向上させる半導体装置及びその製造方法の提供。

【解決手段】ゲート電極3a上にはシリサイド層7aを形成するとともに、ゲート電極3b上にはシリサイド防止膜4bを形成し、半導体基板1上の第1の領域においては、シリサイド防止膜4bが露出するように、犠牲膜10、CMPストッパ膜9および層間絶縁膜8のCMPを行い、第2の領域においては、CMPストッパ膜9が露出するように、犠牲膜10のCMPを行うことで、第1の領域R1および第2の領域R2を平坦化する。

(もっと読む)

半導体装置、及びその製造方法

【課題】 金属層と半導体層との接続抵抗の上昇を抑えた積層ゲート電極を有する半導体装置、及びその製造方法を提供する。

【解決手段】 半導体装置10は、半導体基板11に形成された第1導電型のソース領域及びドレイン領域14と、ソース領域とドレイン領域との間に形成されたチャネル領域16と、チャネル領域上に形成されたゲート絶縁膜21とを有する。半導体装置10は更に、ゲート絶縁膜上に形成された金属ゲート電極層22と、金属ゲート電極層上に形成された、第1導電型とは逆の導電型である第2導電型の半導体ゲート電極層23とを有する。

(もっと読む)

半導体装置とその製造方法

【課題】SRAMを備えた半導体装置とその製造方法において、当該SRAMの占有面積を低減すること。

【解決手段】SRAMが形成された第1の領域Iとそれ以外の第2の領域IIとを有するシリコン基板10と、第1の領域Iに形成され、第1のゲート電極19aを備えたSRAMの第1のトランジスタTRn1と、第2の領域IIに形成され、第2のゲート電極19bを備えた第2のトランジスタTRn0とを有し、第1のゲート電極19aの高さが、第2のゲート電極19bの高さよりも低い半導体装置による。

(もっと読む)

金属製のソースとドレインを有するトランジスタを製造するための方法

【課題】ソース・ドレイン領域のシリサイド化後に選択的エッチングを不要とする電界効果トランジスタ製造方法を提供する。

【解決手段】a)チャネル、ゲート及びハード・マスク118を含んでなる構造物を基板,誘電体層108の上に作るステップと、b)前記構造物とトランジスタの周囲領域を完全に覆う誘電体を形成するステップと、c)上記誘電体部分に、チャネルの側壁を露出させる二つの穴を形成するステップと、d)上記各穴の各壁部の上に第1の金属層132を蒸着するステップと、e)前記側壁をシリサイド化するステップと、f)前もってシリサイド化した部分に接してトランジスタのソース電極136とドレイン電極138を形成するように、第1の金属層の上に第2の金属層を蒸着するステップと、g)ハード・マスクに対しては阻止される、第2の金属層の化学機械研磨を行なうステップと、を有する製造方法。

(もっと読む)

半導体装置の製造方法

【目的】膜切れの無い均一なシード膜を形成する半導体装置の製造方法を提供することを目的とする。

【構成】本発明の一態様の半導体装置の製造方法は、基体上に絶縁膜を形成する工程(S102)と、絶縁膜に開口部を形成する工程(S104)と、開口部内に光触媒膜を形成する工程(S110)と、Cuを含有する溶液に光触媒膜を浸漬させた状態で光触媒膜に紫外線を照射する工程(S112)と、開口部内に電解めっき法によりCuを埋め込む工程(S114)と、を備えたことを特徴とする。

(もっと読む)

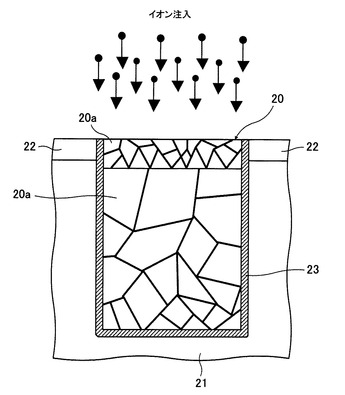

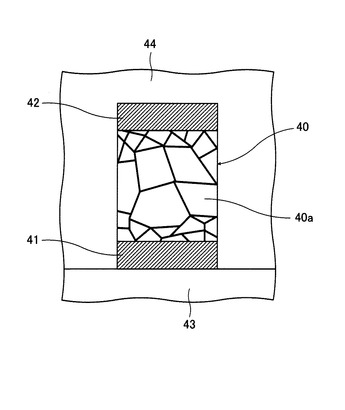

凹状のドレイン及びソース区域並びに非共形的な金属シリサイド領域を有するMOSトランジスタを備えたCMOSデバイス

【解決手段】

凹状のドレイン及びソース構造のトランジスタ(150)における非共形的金属シリサイド層(156)は、歪誘起メカニズム、ドレイン/ソース抵抗等に関して高い性能を提供することができる。このために場合によっては、シリサイド化プロセスに先立ちアモルファス化注入プロセスが実行されてよい一方で、他の場合には高融点金属(156)の異方的な堆積が用いられてよい。

(もっと読む)

誘電体エッチストップ層の選択的形成

【解決手段】 パターニングされた金属フィーチャの上方に誘電体エッチストップ層を選択的に形成する方法を開示する。実施形態には、当該方法に従って形成されたエッチストップ層をゲート電極の上方に設けているトランジスタが含まれる。本発明の特定の実施形態によると、ゲート電極の表面上に金属を選択的に形成して、当該金属をケイ化物またはゲルマニウム化物に変換する。他の実施形態によると、ゲート電極の表面上に選択的に形成された金属によって、ゲート電極の上方にシリコンまたはゲルマニウムのメサを触媒成長させる。ケイ化物、ゲルマニウム化物、シリコンメサ、またはゲルマニウムメサの少なくとも一部を酸化、窒化、または炭化して、ゲート電極の上方にのみ誘電体エッチストップ層を形成する。 (もっと読む)

半導体装置の製造方法

【課題】配線のエレクトロマイグレーション耐性を向上させる。

【解決手段】めっき法を用いてCu配線20を形成する際、まず第1の電流密度の条件で第1の平均粒径を有する第1の金属膜を形成し、次いで、第1の電流密度よりも高い第2の電流密度の条件で第1の平均粒径よりも大きい第2の平均粒径を有する第2の金属膜を形成する。その後、第1,第2の金属膜の上部に所定元素を導入し、導入後、第1,第2の金属膜上にキャップ膜を形成する。

【選択図】図5  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】配線のエレクトロマイグレーション耐性を向上させる。

【解決手段】Al配線40を形成する際、バリアメタル41上に、Al粒子40aが第1の平均粒径となるように第1の条件で第1のAl膜を形成し、次いで、第1の平均粒径より小さい第2の平均粒径となるように第2の条件で第2のAl膜を形成する。その後、第2のAl膜上にバリアメタル42を形成し、形成後、バリアメタル41,42および第1,第2のAl膜を配線パターンに加工する。

【選択図】図9  (もっと読む)

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】トランジスタのチャネルに応力を与えるストレスライナーとして機能するシリコン窒化膜を形成した場合に、クラックの発生を抑えることができる半導体装置の製造方法及び半導体装置を提供する。

【解決手段】半導体基板1に形成されたnチャネル型トランジスタ20を覆い、nチャネル型トランジスタ20のチャネルに対してチャネル長方向の引張応力を作用させるシリコン窒化膜11、12を形成する半導体装置の製造方法であって、nチャネル型トランジスタ20の上に一層目のシリコン窒化膜11を形成する工程と、一層目のシリコン窒化膜11に紫外線を照射する工程と、紫外線照射の後、一層目のシリコン窒化膜11の上に一層目のシリコン窒化膜11よりも薄いシリコン窒化膜12を少なくとも一層以上形成する工程とを備え、引張応力を作用させるシリコン窒化膜を複数段階に分けて形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極の周囲に形成される空洞と保護膜に形成されるホールとの境界部分の開口を封止しやすい構造を実現する。

【解決手段】半導体装置を、ゲート電極3と、高さが低い部分6Aと高さが高い部分6Bとを有する階段状の空間6をゲート電極3の周囲に有する保護膜4と、高さが低い部分6Aに接するように保護膜4に形成されたホール5とを備えるものとする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】良好なオン特性と耐圧特性とを奏することが可能な半導体装置および半導体装置の製造方法を提供する。

【解決手段】シリコン基板11上に形成されたキャリア走行層としてのGaN層13と、GaN層13に形成されたキャリア供給層としてのAlGaN層14と、少なくともAlGaN層14の上層の一部に形成され、GaN層13におけるキャリアと反対の導電性を有するp−AlGaN層15と、少なくともp−AlGaN層15上に形成された第2アノード電極AN2と、を備えることで、例えばオフ状態においてp−AlGaN層15下に空乏層を広げることが可能となるため、p−AlGaN層15下に位置するヘテロ接合界面付近に2次元電子ガスが発生することを抑制して、リーク電流の低減を図ることが可能となる。

(もっと読む)

薄膜半導体装置およびその製造方法

【課題】 優れたコンタクト特性及び優れた素子特性を持った薄膜半導体装置及びその製造方法を提供すること。

【解決手段】 透明絶縁性基板上に形成され、所定の間隔を隔てて不純物を含むソース領域ドレイン領域を有する島状半導体層、前記ソース領域及びドレイン領域の間の島状半導体層上に形成されたゲート絶縁膜、前記ゲート絶縁膜上に形成されたゲート電極、前記島状半導体層及びゲート電極を覆う層間絶縁膜、前記ソース領域及びドレイン領域にそれぞれ接続する、前記層間絶縁膜に形成されたコンタクト孔内にそれぞれ埋め込まれた不純物を含む多結晶半導体層、及び前記多結晶半導体層に接続する高融点金属層を含む配線層を具備し、前記多結晶半導体層と配線層の高融点金属層との間には、高融点金属と半導体との化合物からなる薄層が形成されていることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】 イオン注入時のチャネリングを防止することが可能な半導体装置の製造方法を提供する。

【解決手段】 キャパシタを有する半導体装置の製造工程において、キャパシタの誘電膜となる絶縁膜とゲート電極上のチャネリング防止膜を同時に形成する。製造工程の簡略化および熱工程の削減が可能となる。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート酸化膜の信頼性を阻害せずに、ゲート電極の低抵抗化を実現可能な半導体装置およびその製造方法を提供することを目的とする。

【解決手段】本発明に係る半導体装置は、炭化珪素からなり、表面にエピタキシャル結晶成長層2が形成された半導体基板1と、エピタキシャル結晶成長層2上部に選択的に形成されたウェル領域3とを備える。そして、ウェル領域3上部に選択的に形成されたソース領域4と、ソース領域4とエピタキシャル結晶成長層2とに挟まれたウェル領域3の表面を覆うゲート絶縁膜6上に形成されたゲート電極7とを備える。ゲート電極7は、珪素層7aと、炭化珪素層7bとの積層構造からなり、ゲート電極7上部に形成されたシリサイド層7cをさらに備える。

(もっと読む)

高ストレス薄膜の成膜方法及び半導体集積回路装置の製造方法

【課題】プロセス条件で与えられるストレス以上に大きなストレスを薄膜に与えることが可能な高ストレス薄膜の成膜方法を提供すること。

【解決手段】水素を含む成膜原料ガスをチャンバー内に供給し、水素が取り込まれた薄膜を半導体基板上に成膜する工程(ステップ1)と、薄膜から水素を離脱させる物質を含む水素離脱ガスを前記チャンバーにパルス的に供給しながら薄膜から水素を離脱させる工程(ステップ2、ステップ11及び12)と、を具備する。

(もっと読む)

半導体装置とその製造方法

【課題】半導体装置とその製造方法において、半導体基板に欠陥が入るのを防止することを目的とする。

【解決手段】素子分離溝20aにより活性領域ARが画定されたシリコン基板20と、素子分離溝20a内に形成された素子分離絶縁膜23とを有し、素子分離絶縁膜23の上面が、活性領域ARにおけるシリコン基板20の上面よりも低い半導体装置による。

(もっと読む)

プラズマCVD窒化珪素膜の成膜方法及び半導体集積回路装置の製造方法

【課題】N−H結合を減少させることができ、N−H結合の量とSi−H結合の量とを合計した総膜中水素量を減らすことが可能なプラズマCVD窒化珪素膜の成膜方法を提供すること。

【解決手段】処理容器1内に、珪素含有ガスと、窒素及び水素含有ガスとを導入する工程と、マイクロ波を処理容器1内に放射し、処理容器1内に導入された珪素含有ガス及び窒素及び水素含有ガスをプラズマ化する工程と、プラズマ化された珪素含有ガス及び窒素及び水素含有ガスを、被処理基板Wの表面上に供給し、被処理基板Wの表面上に窒化珪素膜を成膜する工程と、を備え、窒化珪素膜の成膜条件を、処理温度を300℃以上600℃以下、珪素含有ガスと窒素及び水素含有ガスとの流量比を0.005以上0.015以下、マイクロ波パワーを0.5W/cm2以上2.045W/cm2以下、処理圧力を133.3Pa以上13333Pa以下とする。

(もっと読む)

141 - 160 / 425

[ Back to top ]