Fターム[4M104EE05]の内容

半導体の電極 (138,591) | 絶縁膜(特徴のあるもの) (8,323) | 絶縁膜の適用位置 (3,412) | 電極上 (625)

Fターム[4M104EE05]の下位に属するFターム

パシベーション膜 (200)

Fターム[4M104EE05]に分類される特許

101 - 120 / 425

半導体装置およびその製造方法

【課題】写真製版プロセスのマージンを大幅に拡大でき、かつマイクロローディング効果を低減することによって「開口不良」を抑制できるとともに「ショート」のプロセス裕度を確保しやすくし、かつコンタクト抵抗を低減できる半導体装置の製造方法を提供する。

【解決手段】活性領域に対して傾斜して延びるようにゲート電極層50と窒素を含む絶縁膜2とが積層される。シリコン酸化膜5が形成される。活性領域の幅より大きくかつ互いに隣り合う活性領域のピッチより小さい帯状の開口パターンが絶縁膜2に形成され、開口パターンから1対の不純物拡散領域の各々が露出させられる。開口パターンが導電層23で埋め込まれる。導電層23から1対の不純物拡散領域の各々に電気的に接続されたプラグ導電層23a、23bが形成されるとともに、プラグ導電層23a、23bの各上面と絶縁膜2の上面とが同一平面とされる。

(もっと読む)

表示装置および表示装置の製造方法

【課題】有機半導体層を用いた薄膜トランジスタと画素電極とを含む層間に発生する応力を緩和することが可能で、これによりトランジスタ特性の劣化を防止して、表示特性および信頼性の向上が図られた表示装置を提供する。

【解決手段】有機半導体層を用いた薄膜トランジスタが配列形成された基板と、薄膜トランジスタを覆う状態で基板上に設けられた層間絶縁膜と、層間絶縁膜上に設けられた画素電極とを備えたものである。特に、層間絶縁膜は、薄膜トランジスタよりも平面視的なサイズが小さい凹凸パターンからなる凹凸表面を有しており、この凹凸表面上に画素電極が設けられていることを特徴としている。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート配線に達するコンタクトホールを確実に形成し得る半導体装置及びその製造方法を提供する。

【解決手段】第1応力膜38を形成する工程と、第1応力膜とエッチング特性が異なる絶縁膜40を形成する工程と、第1領域2を覆う第1マスク60を用いて、第2領域内の絶縁膜をエッチングするとともに、第1領域のうちの第2領域に近接する部分の絶縁膜をサイドエッチングする工程と、第1マスクを用いて第2領域内の第1応力膜をエッチングする工程と、絶縁膜とエッチング特性が異なる第2応力膜を形成する工程と、第2領域を覆い、第1領域側の端面が絶縁膜上に位置する第2マスクを用いて、第2応力膜の一部が第1応力膜の一部及び絶縁膜の一部と重なり合うように第2応力膜をエッチングする工程と、第1領域と第2領域との境界部におけるゲート配線20に達するコンタクトホールを形成する工程とを有している。

(もっと読む)

半導体装置及びその作製方法

【課題】接続する素子の駆動電圧によってトランジスタのドレイン電圧が決定される。トランジスタの小型化にともないドレイン領域に集中する電界強度が高まり、ホットキャリアが生成し易くなる。ドレイン領域に電界が集中し難いトランジスタを提供することを課題の一とする。また、トランジスタを有する表示装置を提供することを課題の一とする。

【解決手段】高い導電率を有する第1配線層および第2配線層の端部とゲート電極層の重なりをなくすことにより、第1電極層及び第2電極層近傍に電界が集中する現象を緩和してホットキャリアの発生を抑制し、加えて第1配線層および第2配線層より高抵抗の第1電極層および第2電極層をドレイン電極層として用いてトランジスタを構成する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】ゲート電極部と容量コンタクトプラグとのショートを防止する。

【解決手段】複数のゲート電極部10と該ゲート電極部10間を接続する配線部との上に、耐エッチング膜17を備えたゲートハードマスク20を形成後、前記配線部上の前記耐エッチング膜17を除去する。これにより、CMP処理を経てコンタクトプラグ22を形成し、さらに、エッチングにより容量コンタクトホール24を開口して容量コンタクトプラグ25を形成した場合に、ゲート電極部10と容量コンタクトプラグ25とのショートを防止することができる。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層とソース電極層又はドレイン電極層との間のコンタクト抵抗を低減し、電気特性を安定させた薄膜トランジスタを提供する。また、該薄膜トランジスタの作製方法を提供する。

【解決手段】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層より導電率の高いバッファ層を形成し、酸化物半導体層とソース電極層又はドレイン電極層とがバッファ層を介して電気的に接続されるように薄膜トランジスタを形成する。また、バッファ層に逆スパッタ処理及び窒素雰囲気下での熱処理を行うことにより、酸化物半導体層より導電率の高いバッファ層を形成する。

(もっと読む)

半導体装置

【課題】チャネル領域に高い引張応力を加えることのできる、半導体装置を提供すること。

【解決手段】半導体層2上には、Si−N結合を3以上有するSiを含むSiN膜からなる引張応力窒化膜15が形成されている。この引張応力窒化膜15は、FTIR(フーリエ変換型赤外分光)法により、Si-Hピーク面積およびN-Hピーク面積を求めたときに、Si-Hピーク面積に対するN-Hピーク面積の比が2.5〜2.7の範囲内となる構造を有している。

(もっと読む)

電子素子及びその製造方法、並びに表示装置

【課題】低温プロセスで製造でき、リーク電流が抑制された電子素子を提供する。

【解決手段】基板10上に、端部断面のテーパー角度が60°以下である下部電極22と、前記下部電極22上に配置され、水素原子の含有率が3原子%以下であり、波長650nmにおける屈折率nが1.475以下であるSiO2膜24と、前記SiO2膜24上に配置され、前記下部電極22と重なり部を有する上部電極26と、を有する電子素子である。

(もっと読む)

ダイヤモンド電極構造

【課題】 高温あるいは強反応性化学物質中においても金属、ダイヤモンド接合の品質を保持したまま、機能を発揮するダイヤモンド電極構造を提供する。

【解決手段】

ダイヤモンド表面にルテニウム(Ru)もしくは酸化ルテニウム(RuO2)からなる電極を設けることにより、電気的接合を行うことを特徴とするダイヤモンド電極構造。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】半導体基板1に形成したnチャネル型MISFETQnのソース・ドレイン用のn+型半導体領域7bおよびゲート電極GE1上と、pチャネル型MISFETQpのソース・ドレイン用のp+型半導体領域8bおよびゲート電極GE2上とに、ニッケル白金シリサイドからなる金属シリサイド層13bをサリサイドプロセスで形成する。その後、半導体基板1全面上に引張応力膜TSL1を形成してから、pチャネル型MISFETQp上の引張応力膜TSL1をドライエッチングで除去し、半導体基板1全面上に圧縮応力膜CSL1を形成してからnチャネル型MISFETQn上の圧縮応力膜CSL1をドライエッチングで除去する。金属シリサイド層13bにおけるPt濃度は、表面が最も高く、表面から深い位置になるほど低くなっている。

(もっと読む)

電界効果型トランジスタ及びその製造方法

【課題】ゲート容量の増大を抑制しつつ、耐湿性を大幅に向上させることを可能にした電界効果型トランジスタおよびその製造方法を得る。

【解決手段】半導体層1上にT型ゲート電極2が形成された電界効果型トランジスタであって、T型ゲート電極2が形成されている領域をトランジスタ能動領域としたとき、当該トランジスタ能動領域全体において、T型ゲート電極2上に設けられた、耐湿性・耐エッチング性の高い絶縁膜若しくは有機膜を含む第1の高耐湿性保護膜5を備え、T型ゲート電極2の傘下を含むT型ゲート電極2の近傍において、半導体層1と第1の高耐湿性保護膜5との間に空隙6が形成されており、空隙6が外界に接している端面6aを第2の高耐湿性保護膜7により塞いだ構成となっている。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極との短絡を抑えたセルフアラインコンタクトを有する、製造コストの低い半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置100は、それぞれ半導体基板2上に形成され、それぞれゲート電極4a、4bを有し、互いの間のソース・ドレイン領域8aを共有する隣接したトランジスタ1a、1bと、ゲート電極4a上に形成された絶縁膜11aと、ゲート電極4b上に形成された絶縁膜11aよりも厚さの厚い領域を有する絶縁膜11bと、ソース・ドレイン領域8aに接続され、その中心位置がゲート電極4a、4bの間の中心位置よりもゲート電極4b側に位置するSAC14と、を有する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】n型MOSトランジスタ、p型MOSトランジスタにおいて共通のゲート絶縁膜構造及びゲート電極材料を用いながら、各々のトランジスタのしきい値電圧を適正な値へ設定し、且つゲート絶縁膜における酸素欠損に伴う移動度の低下を抑制する。

【解決手段】メタルゲート電極及び高誘電率ゲート絶縁膜を用いた半導体装置の製造方法であって、n型半導体領域200及びp型半導体領域300上にそれぞれ、シリコン酸化物からなる第1のゲート絶縁膜、La,Al,Oを含む第2のゲート絶縁膜、Hfを含む第3のゲート絶縁膜を積層し、その上に金属膜からなるゲート電極を形成し、次いでp型半導体領域300上の、第1のゲート絶縁膜,第2のゲート絶縁膜,第3のゲート絶縁膜,及びゲート電極の積層構造を、水素拡散防止膜350で被覆した後、水素雰囲気で熱処理を施す。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極をシリサイド化する際にゲート長方向の体積膨張が生じにくく、ゲート電極とコンタクトプラグ等との短絡不良が生じにくい半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板10の上にゲート絶縁膜15を介在させて形成され、上部がシリサイド化されたゲート電極17と、ゲート電極17の側面上に形成されたオフセットスペーサ20と、オフセットスペーサ20の側面上を覆う断面L字状のサイドウォール22Aとを備えている。オフセットスペーサ20は、ゲート電極17側に形成された内側オフセットスペーサ20Aと、内側オフセットスペーサ20Aの側面上に形成された外側オフセットスペーサ20Bとを有している。内側オフセットスペーサ20Aと、外側オフセットスペーサ20B及び内側サイドウォール22Aとは、エッチング選択性が異なる材料からなる。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極とコンタクト配線のショート不良を防止できる半導体装置の製造方法を提供する。

【解決手段】半導体基板32上にゲートハードマスク、ゲート電極34及びゲート絶縁膜33を形成する。ゲートハードマスクの線幅をゲート電極よりも狭くした後、S/Dエクステンション36を形成する。全面にシリコン酸化膜を堆積形成し、エッチバックしてゲート電極の側壁から上面の一部上に渡って連続的に残存させた絶縁部材37を形成する。ゲートハードマスクを除去した後、ゲート電極と絶縁部材をマスクにしてコンタクトジャンクション38を形成する。金属シリサイド膜を形成後、シリコン窒化膜40と層間絶縁膜41を順次堆積形成する。層間絶縁膜にコンタクトホールを形成し、続いてシリコン酸化膜との選択比が高い異方性エッチングによってシリコン窒化膜を除去することでコンタクトホールを開孔し、コンタクト配線43を形成する。

(もっと読む)

半導体装置

【課題】温度が上昇するほどキャリアの移動度を向上できる半導体装置を提供する。

【解決手段】半導体装置は、素子形成面が(110)面方位の半導体基板上にチャネル長方向が<−110>方向に沿って配置される第1絶縁ゲート型電界効果トランジスタpMOS1と、前記半導体基板上にチャネル長方向が<−110>方向に沿って配置され、前記第1絶縁ゲート型電界効果トランジスタと前記チャネル長方向に隣接する第2絶縁ゲート型電界効果トランジスタnMOS1と、前記第1,第2絶縁ゲート型電界効果トランジスタ上を覆うように設けられ、正の膨張係数を有し、前記第1,第2絶縁ゲート型電界効果トランジスタに、動作熱によりチャネル長方向に沿って圧縮応力を加えピエゾ材料を含む第1ライナー絶縁膜11−1とを具備する。

(もっと読む)

半導体装置

【課題】ゲートパルスストレスによる耐圧劣化およびしきい値電圧の変動を抑制できる半導体装置を提供する。

【解決手段】ゲート電極GEは、ソース領域およびドリフト領域DRに挟まれる領域上に絶縁層FOを介在して形成されている。フィールドプレートFPは、ゲート電極GEおよびドリフト領域DR上を延在し、かつゲート電極GEに電気的に接続されている。ダミー導電層DCは、フィールドプレートFPとドリフト領域DRとの間において絶縁層FO上に形成され、かつソース領域に電気的に接続されている。

(もっと読む)

ウエット処理装置

【課題】 被処理物を回転させながら処理液を供給する枚葉式ウエット処理において、被処理物表面に形成された導電性部材のガルバニックコロージョンを抑制可能であり、更には、ナノレベルのパーティクルをも除去することが可能なウエット処理装置及びウエット処理方法を提案する。

【解決手段】被処理物Wの被処理面Waの少なくとも一部を被覆する被覆手段13を備え、保持手段11に保持された被処理物Wの被処理面Waと被覆手段13との間に間隙gを形成した状態にて、処理液供給手段14により脱酸素状態の処理液を供給する。更に、被処理物Wの被処理面Waと対向する位置に配される対向電極31aと、被処理物Wに接続可能な被処理物用電極32との間に、電圧を印加する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】層間絶縁膜を表面研磨する工程を経て形成される半導体装置の信頼性を向上させる。

【解決手段】シリコン基板1の主面s1上に、高耐圧ゲート絶縁膜IG1および高耐圧ゲート電極EG1からなる高耐圧ゲートG1を形成した後、サリサイドブロック膜SAB、層間絶縁膜ILを順に形成し、その層間絶縁膜ILをCMPにより研磨する。サリサイドブロック膜SABは、下層から順に酸化シリコンを主体とする絶縁膜である保護酸化膜t1と、窒化シリコンを主体とする絶縁膜である保護窒化膜t2とによって形成する。また、層間絶縁膜ILの研磨は、高耐圧ゲートG1上面のサリサイドブロック膜SABに達するまで研磨する。

(もっと読む)

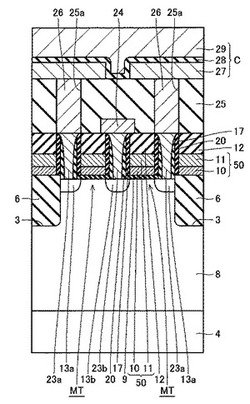

半導体装置

【課題】ゲート電極とのコンタクトのためのコンタクトホールの形成時に、ゲート電極が深く掘り下げられることを防止できる半導体装置を提供すること。

【解決手段】ゲートトレンチ6を有するエピタキシャル層3に、ボディ領域5、ドレイン領域4、ソース領域9およびボディコンタクト領域10を形成する。ゲートトレンチ6には、ゲート電極8を埋設する。エピタキシャル層3には、層間絶縁膜11を積層する。ゲート電極8と層間絶縁膜11との間には、エピタキシャル層3とはエッチングレートの異なる材料からなるエッチングストッパ層14を介在させる。そして、エッチングにより、ゲート電極8およびボディコンタクト領域10それぞれとのコンタクトのための、ゲートコンタクトホール13およびソースコンタクトホール15を同時に形成する。ゲートコンタクトホール13は、平面視でエッチングストッパ層14と重なるように形成する。

(もっと読む)

101 - 120 / 425

[ Back to top ]