Fターム[4M104EE05]の内容

半導体の電極 (138,591) | 絶縁膜(特徴のあるもの) (8,323) | 絶縁膜の適用位置 (3,412) | 電極上 (625)

Fターム[4M104EE05]の下位に属するFターム

パシベーション膜 (200)

Fターム[4M104EE05]に分類される特許

81 - 100 / 425

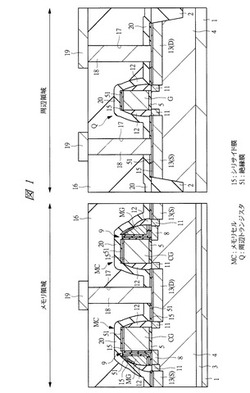

半導体装置

【課題】半導体装置の信頼性を向上する。

【解決手段】メモリセルMCは、半導体基板1の主面上のゲート絶縁膜5を介して設けられたコントロールゲート電極CGと、コントロールゲート電極CGの側面および半導体基板1の主面に沿って設けられたONO膜9と、ONO膜9を介してコントロールゲート電極CGの側面および半導体基板1の主面上に設けられたメモリゲート電極MGとを有する。コントロールゲート電極CGおよびメモリゲート電極MGの上部には、シリサイド膜15およびシリサイド膜15の表面の酸化によって形成された絶縁膜51が設けられている。

(もっと読む)

トランジスタ及びその製造方法

【課題】Siチヤネルを有するNMOSとSiGeチャネルを有するPMOSで、NMOSには引張り歪みを与える、PMOSには、表面のダングリングボンドを減少させることができる半導体装置を提供する。

【解決手段】単結晶シリコン基板50の一部領域にシリコンゲルマニウムチャネル膜54aを形成し、PMOSトランジスタを、シリコン膜60aを形成し、NMOSトランジスタを形成する。単結晶シリコン基板、シリコンゲルマニウムチャネル膜、PMOSトランジスタ、NMOSトランジスタの表面上に、反応ガス、雰囲気ガス及び水素ガスを含む蒸着ガスを用いて、シリコン窒化膜82を形成し、PMOSトランジスタは、シリコンゲルマニウムチャネル膜表面のダングリングボンドの除去により、ホールスキャタリングが抑制され、NMOSトランジスタには引張り歪みを与えることにより動作特性の改善ができる。

(もっと読む)

内側にへこんだ形状を含んだトランジスタを製造する方法

トランジスタを製造する方法は、導電材料層と電気絶縁材料層とを順に含んだ基板を準備する工程と、前記電気絶縁材料層上にレジスト材料層を堆積する工程と、前記レジスト材料層をパターニングして、前記電気絶縁材料層の一部を露出させる工程と、露出された前記電気絶縁材料層を除去して、前記導電材料層の一部を露出させる工程と、露出された前記導電材料層を除去し、前記導電材料層及び前記電気絶縁材料層内に凹部形状を作り出す工程と、前記基板と露出された前記電気絶縁材料層及び前記導電材料層とを第2の電気絶縁材料層で共形に被覆する工程と、前記第2の電気絶縁材料層を半導体材料層で共形に被覆する工程と、前記半導体材料層上に導電材料層を指向性堆積する工程とを含む。

(もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】第1のMISトランジスタの閾値電圧が高くなることを防止する。

【解決手段】半導体装置は、第1,第2のMISトランジスタTr1,Tr2を備えている。第1,第2のMISトランジスタは、第1,第2の活性領域10a,10b上に形成され、第1,第2の高誘電率膜13a,13bを有する第1,第2のゲート絶縁膜13A,14Bと、第1,第2のゲート絶縁膜上に形成された第1,第2のゲート電極18A,18Bとを備えている。第1のゲート絶縁膜13Aと第2のゲート絶縁膜14Bとは、第1の素子分離領域11L上において分離されている。第1の素子分離領域11Lを挟んで対向する第1の活性領域10aの一端と第2の活性領域10bの一端との距離をsとし、第1の活性領域10aの一端から第1の素子分離領域11L上に位置する第1のゲート絶縁膜13Aの一端までの突き出し量をd1としたとき、d1<0.5sの関係式が成り立っている。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極抵抗の増大や工程数の増加を招くことなく、シリコン混晶層を用いた歪技術により、半導体装置の高性能化を実現する。

【解決手段】半導体基板100における第1のゲート電極106Aから見て第1の絶縁性サイドウォールスペーサ111Aの外側に第1のソースドレイン領域114Aを形成する。その後、半導体基板100における第2のゲート電極106Bから見て第2の絶縁性サイドウォールスペーサ111Bの外側にリセス部119を形成すると共に、第2のゲート電極106Bを部分的に除去する。その後、リセス部109内に、第2のソースドレイン領域114Bとなるシリコン混晶層120を形成する。

(もっと読む)

自己整合コンタクト

トランジスタは、基板と、基板上の一対のスペーサと、基板上且つスペーサ対間のゲート誘電体層と、ゲート誘電体層上且つスペーサ対間のゲート電極層と、ゲート電極層上且つスペーサ対間の絶縁キャップ層と、スペーサ対に隣接する一対の拡散領域とを有する。絶縁キャップ層は、ゲートにセルフアラインされるエッチング停止構造を形成し、コンタクトエッチングがゲート電極を露出させることを防止し、それにより、ゲートとコンタクトとの間の短絡を防止する。絶縁キャップ層は、セルフアラインコンタクトを実現し、パターニング限界に対して一層ロバストな、より幅広なコンタクトを最初にパターニングすることを可能にする。  (もっと読む)

(もっと読む)

窒化物半導体装置

【課題】パワートランジスタに適用可能なノーマリオフ型の窒化物半導体装置に生じる電流コラプスを抑制できるようにする。

【解決手段】窒化物半導体装置は、サファイアからなる基板11と、該基板11の上に形成されたGaNからなるチャネル層13と、該チャネル層13の上に形成され、該チャネル層13よりもバンドギャップエネルギーが大きいAlGaNからなるバリア層14と、該バリア層14の上に形成され、p型AlGaN層15及びp型GaN層16を含むp型窒化物半導体層と、該p型窒化物半導体層の上に形成されたゲート電極19と、該ゲート電極19の両側方の領域にそれぞれ形成されたソース電極17及びドレイン電極18とを有している。p型窒化物半導体層は、ゲート電極19の下側部分の厚さが該ゲート電極19の側方部分の厚さよりも大きい。

(もっと読む)

半導体装置の製造方法

【課題】トレンチ構造のゲート絶縁膜がエミッタ層等を形成するときの砒素イオンよる損傷を受けることがなく、その絶縁耐圧が向上する半導体装置を低コストで製造できる方法を確立する。

【解決手段】トレンチ3内に埋め込まれて形成されたポリシリコンからなるゲート電極5を高温炉中等で熱酸化してゲート電極5上に厚いポリシリコン熱酸化膜6を形成する。その後に不純物イオンをイオン注入してエミッタ層等となるN型半導体層8を形成する。この場合、ポリシリコン熱酸化膜6の膜厚を、イオン注入によりエミッタ層等となるN型半導体層8を形成するための不純物イオンのシリコン酸化膜中の平均飛程より厚く形成する。これにより、不純物イオンがゲート電極5とN型半導体層8に挟まれたゲート絶縁膜4に損傷を与えるのを防止する。

(もっと読む)

半導体装置およびその製造方法

【課題】DモードとEモードの素子を組み合わせた半導体装置およびその製造方法を提供する。

【解決手段】DモードとEモードのJFETにおけるチャネル領域を設定する場所にそれぞれ凹部2aと凸部2bを備えることで、同一基板上に厚みが異なるn型チャネル層3を形成する。そして、このような厚みが異なるn型チャネル層3によってDモードとEモードで作動するJFETを同一基板上に備えることができるため、SiCでもDモードとEモードのJFETを組み合わせたSiC半導体装置を実現することが可能となる。

(もっと読む)

シリコン層の形成方法、半導体装置の製造方法

【課題】シリコン層表面の溶解を防止しつつ、エピタキシャル成長により形成された凝集性異物を除去する。清浄な表面を有し、膜厚が均一なシリコン層を形成する。

【解決手段】シリコン基板上にエピタキシャル成長によりシリコン層を形成した後に、シリコン層の表面を酸化する。このシリコン層の表面を洗浄して、エピタキシャル成長時にシリコン層の表面に発生した異物を除去する。

(もっと読む)

自己整列グラフェン・トランジスタ

【課題】自己整列グラフェン・トランジスタを作製するスキームを提供する。

【解決手段】グラフェン電界効果トランジスタは、ゲート・スタックであってシード層とシード層の上に形成されたゲート酸化物とゲート酸化物の上に形成されたゲート金属とを含む該ゲート・スタック、絶縁層、およびシード層と絶縁層との間に転写されたグラフェン・シート、を含む。

(もっと読む)

半導体素子

LDMOS(横方向拡散金属酸化物半導体)構造は、ソースを基板及びゲートシールドへと接続させ、この際、このような接点のためにより小さな面積が用いられる。前記構造は、導電性基板層と、ソースと、ドレイン接点とを含む。少なくとも1つの介在層により、前記ドレイン接点が前記基板層から分離される。導電性のトレンチ状のフィードスルー要素が前記介在層を通過し、前記基板及び前記ソースと接触することで、前記ドレイン接点及び前記基板層を電気的に接続する。 (もっと読む)

耐酸化性酸化ホウ素層を含む電極およびその製造方法

ここで開示されているのは、銅、ニッケル、鉄、コバルト、チタン、鉛、アルミニウム、スズおよびこれらの金属の1つを主成分として含む合金からなる群から選択される導電性構成成分を含む導電層と、酸化ホウ素を含む酸化保護層とを含む電極であって、前記酸化保護層が導電層の上面を被覆するかまたは導電層の上面および側面の両方を被覆するかまたは導電層が形成されている全ての場所を被覆する電極であって;導電層および酸化保護層を同時に空気焼成することによって形成される電極である。 (もっと読む)

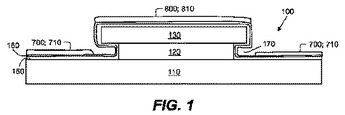

薄膜トランジスタ、薄膜トランジスタを用いた表示装置及び薄膜トランジスタの製造方法

【課題】工程数の増大を引き起こさずに、遮光層で囲まれた薄膜トランジスタと同等以上の遮光能力を有する薄膜トランジスタおよびそれを用いた表示装置を提供する。

【解決手段】第1のゲート電極2と、第1のゲート電極2を覆う第1のゲート絶縁層3と、第1のゲート絶縁層3の上の半導体層6と、半導体層6の上の第2のゲート絶縁層7と、第2のゲート絶縁層7の上の第2のゲート電極8と、半導体層6に電気的に接続されたドレイン電極5及びソース電極4を有する薄膜トランジスタにおいて、半導体層6がZn、Ga、In、Snのうち少なくとも1種以上を含む非晶質酸化物半導体であり、第1のゲート電極2が下方から半導体層6への光の入射を遮り、第2のゲート電極8が上方から半導体層6への光の入射を遮り、第2のゲート電極8は第1のゲート絶縁層3及び第2のゲート絶縁層7を貫通して第1のゲート電極2と電気的に接続され、少なくとも一方の側方から半導体層6に入射する光を遮る。

(もっと読む)

窒化物半導体発光素子

【課題】光取り出し効率が高く、かつ発光効率が高い窒化物半導体発光素子を提供する。

【解決手段】本発明の窒化物半導体発光素子は、窒化物半導体層と、導電性の第1酸化物層と、絶縁性の第2酸化物層とを含み、第1酸化物層および第2酸化物層は、同一種類の酸化物材料からなることを特徴とする。第1酸化物層を構成する二酸化チタン中のチタンに対し、ニオブ、タンタル、モリブデン、ヒ素、アンチモン、アルミニウムまたはタングステンのいずれかがモル比で1%以上10%以下ドープされ、第2酸化物層を構成する二酸化チタン中のチタンに対し、ニオブ、タンタル、モリブデン、ヒ素、アンチモン、アルミニウムまたはタングステンのいずれかがモル比で1%未満ドープされることが好ましい。

(もっと読む)

半導体装置の製造方法

【課題】

太幅配線の添加元素を細幅配線の添加元素とは独立に制御する。

【解決手段】

層間絶縁膜に、第1の幅を有する第1の配線溝および第1の幅より広い第2の幅を有する第2の配線溝を形成し、第1の配線溝および第2の配線溝内に、第1の添加元素を含む第1のシード層を形成し、第1のシード層上に第1の銅層を形成し、第1の配線溝内の第1の銅層および第1のシード層を残存させつつ、第2の配線溝内の第1の銅層および第1のシード層を除去し、その後、第2の配線溝内に、第2の添加元素を含む又は添加元素を含まない第2のシード層を形成し、第2のシード層の上に第2の銅層を形成する。

(もっと読む)

薄膜トランジスタパネルの製造方法

【課題】 液晶表示装置の薄膜トランジスタパネルにおいて、Al系金属からなるゲート電極等がレジスト現像液およびレジスト剥離液によるダメージを受けにくいようにする。

【解決手段】 Al系金属からなるゲート電極2およびゲート配線3の上面にAl酸化膜2a、3aを形成すると、ゲート電極2およびゲート配線3の上面がレジスト膜43a、43b、43c用の現像液および剥離液にさらされることがなく、ゲート電極2およびゲート配線3がレジスト膜43a、43b、43c用の現像液および剥離液によるダメージを受けにくいようにすることができる。

(もっと読む)

半導体ウエハを処理するための方法

【課題】

【解決手段】半導体ウエハを処理するための方法であって:酸化ランタンまたは酸化ランタニド(例えば、Dy2O3、Pr2O3、Ce2O3)を含む層を準備する工程と;炭酸水である水溶液を供給することにより、酸化ランタンまたは酸化ランタニドを含む層を特定の領域で除去して、酸化ランタンまたは酸化ランタニドを含む層が上に蒸着された表面を露出させる工程とを備える方法が開示されている。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】長期絶縁破壊耐性を改善することが可能で、高信頼の炭化珪素半導体装置の製造方法を提供する。

【解決手段】 炭化珪素からなる基板1を不活性ガス雰囲気中で酸化温度まで昇温する段階、酸化温度において基板1上に酸化ガスを導入して基板1の表面を熱酸化する段階、酸化温度において基板1上を不活性ガス雰囲気として熱酸化を停止する段階により、ゲート酸化膜9を成長する工程と、ゲート酸化膜9上に多結晶シリコン膜を成膜し、多結晶シリコン膜を選択的に除去してゲート電極7を形成する工程と、ゲート電極7の少なくとも側面を酸化して、多結晶シリコン熱酸化膜8を形成する工程とを備える。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】本発明は、薄膜トランジスタのソース領域やドレイン領域へのコンタクトを確実

にした半導体装置を提供するものである。

【解決手段】本発明における半導体装置において、半導体層上の絶縁膜およびゲイト電極

上に形成された第1の層間絶縁膜と、前記第1の層間絶縁膜の上に形成された第2の層間

絶縁膜と、前記第2の層間絶縁膜、前記第1の層間絶縁膜、および前記絶縁膜に設けられ

たコンタクトホールとを有する。前記第1の絶縁層の膜厚は、前記積層の絶縁膜の合計膜

厚の1/3以下に形成する。

(もっと読む)

81 - 100 / 425

[ Back to top ]