Fターム[4M104FF40]の内容

Fターム[4M104FF40]に分類される特許

1 - 20 / 36

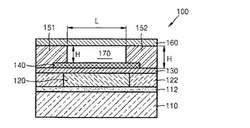

エアギャップを備えるグラフェントランジスタ、それを備えるハイブリッドトランジスタ及びその製造方法

【課題】エアギャップを備えるグラフェントランジスタ、それを備えるハイブリッドトランジスタ及びその製造方法を提供する。

【解決手段】基板上のゲート電極と、ゲート電極上のゲート絶縁層と、ゲート絶縁層上のグラフェンチャネルと、グラフェンチャネル上で互いに離隔しているソース電極及びドレイン電極と、ソース電極及びドレイン電極の上面を覆い、グラフェンチャネル上でソース電極とドレイン電極との間にエアギャップを形成するカバーと、を備えるグラフェントランジスタ。前記ソース電極と前記ドレイン電極との間の前記グラフェンチャネルの長さが、10nm〜100nmである。

(もっと読む)

半導体装置

【課題】窒化ガリウム系半導体で形成された半導体層を有する半導体素子において、消費電力を増大させず、かつ、大型化することなく、半導体素子の電極に電圧をかけたときに発生する電流コラプス現象を抑制する。

【解決手段】窒化ガリウム系半導体が積層されて形成された半導体素子と、半導体素子に対して積層方向に形成され、外部からのエネルギーの入力なしで半導体素子に光を照射する自己発光体とを備える半導体装置を提供する。

(もっと読む)

窒化物半導体装置

【課題】リードフレーム上に搭載された窒化物FETを備えスイッチング特性に優れた窒化物半導体装置を提供する。

【解決手段】窒化物FETと、複数のリードを含むリードフレームと、を備え、前記窒化物FETは少なくとも第1の主電極と第2の主電極と制御電極とを有し、前記リードフレームは、前記第1の主電極に接続される第1のリードと、前記第2の主電極に接続される第2のリード及び第3のリードと、前記制御電極に接続される第4のリードと、を有し、前記窒化物FETは、前記第3のリードと前記第4のリードとの間に印加される電圧に応じて前記第1のリードと前記第2のリードとの間に電流を流すことを特徴とする窒化物半導体装置。

(もっと読む)

半導体装置

【課題】エアブリッジの強度を向上させる。

【解決手段】半導体層上に設けられ、互いに並列に配置された複数のソースフィンガー10と、半導体層上に設けられ、複数のソースフィンガー10と交互に配置された複数のドレインフィンガー12と、半導体層上に設けられ、ソースフィンガー10とドレインフィンガー12との間にそれぞれ配置された複数のゲートフィンガー14と、複数のゲートフィンガー14同士、複数のソースフィンガー10同士、および複数のドレインフィンガー12同士のいずれかを共通に接続するバスラインと、複数のソースフィンガー10、複数のドレインフィンガー12、および複数のゲートフィンガー14のいずれかに設けられ、バスライン上を跨ぐ複数の第1エアブリッジ24と、複数の第1エアブリッジ24同士の間を接続し、半導体層との間に空隙を有する第2エアブリッジ26と、を備える半導体装置。

(もっと読む)

電力用半導体装置

【課題】JBSであってもサージ電流による温度上昇とその正帰還により素子破壊に至る場合があった。

【解決手段】n型のSiC基板と、SiC基板の第一主面に形成され、SiC基板よりも不純物濃度の低いn型SiCドリフト層と、ドリフト層に形成されたp型SiCの第一の半導体領域と、第一の半導体領域の表層側に形成され、第一の半導体領域よりも不純物濃度が高濃度であるp型SiCの第二の半導体領域と、ドリフト層の表面に形成され第一の半導体領域とショットキー接続し、第二の半導体領域とオーミック接続するショットキー電極と、ショットキー電極の表面に形成されたアノード電極と、アノード電極の表面で、第一の半導体領域の直上に形成され、上面から見て第一の半導体領域の領域を含むように第一の半導体領域よりも広い面積に形成されたファーストボンドと、SiC基板の第二主面に形成されたカソード電極とを備えている。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】所望の抵抗値を有する制御ゲートを備えた半導体装置の製造方法を提供すること。

【解決手段】シリコン基板13の表面上に第1の絶縁膜15、電荷蓄積層16、第2の絶縁膜17、およびポリシリコン膜21をこの順で形成する工程と、ポリシリコン膜21上および両側壁全面に金属膜25を形成する工程と、金属膜25が形成されたポリシリコン膜21を加熱してシリサイド化する工程と、金属膜25を除去する工程と、を具備する半導体装置の製造方法。

(もっと読む)

半導体装置

【課題】 パワートランジスタ及びSBD素子を有する半導体装置において、SBD素子の耐圧を高める。

【解決手段】 半導体装置は、半導体基板の主面に第1および第2領域を有し、前記第1および第2領域内にはそれぞれ複数の第1および第2導電体が形成され、前記第1領域内の隣接する第1導電体間には、第1半導体領域と、前記第1半導体領域内にあって第1半導体領域と逆の導電型を持つ第2半導体領域とが形成され、前記第2領域内の隣接する第2導電体間には、前記第2半導体領域と同導電型でかつ第2半導体領域より低濃度の第3半導体領域が形成され、前記第3半導体領域の下には第3半導体領域と同導電型で、かつ第3半導体領域より高濃度の第4半導体領域が形成され、前記第2領域の半導体基板上には金属が形成され、前記金属は前記第2半導体領域と電気的に接続され、前記第3半導体領域は、前記金属と接触しショットキー接合を形成している。

(もっと読む)

半導体装置、設計装置、及びプログラム

【課題】リングゲート型MOSトランジスタ間の領域だけでなく、リング内の領域においてもディッシング現象の発生を抑止する。

【解決手段】半導体装置1は、基板10と、基板10上に形成されたリング形状のゲート電極21を有するトランジスタ20bと、ゲート電極21の外側に配置され、ゲート電極21と同層に設けられる複数の外部ダミーパターン40と、ゲート電極21の内側に配置され、ゲート電極21と同層に設けられる少なくとも1つの内部ダミーパターン41とを備える。

(もっと読む)

高電子移動度トランジスタ

【課題】 HEMTにおいて、2次元電子ガス層の電気抵抗の増加が抑制された正孔排出用電極を提供すること。

【解決手段】 HEMT10は、ゲート電極34とドレイン電極32の間のヘテロ接合層27に接触する正孔選択通過膜43と、その正孔選択通過膜43に接触する正孔排出用電極46を備えている。正孔選択通過膜43は、へテロ接合層27に接触する第1部分領域42と正孔排出用電極46に接触する第2部分領域44を有している。第2部分領域42のp型不純物の濃度は、第1部分領域44のp型不純物濃度よりも濃い。

(もっと読む)

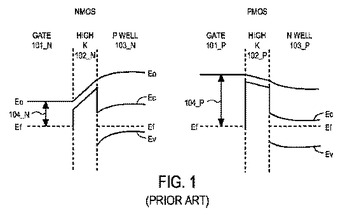

デュアル仕事関数ゲート構造

トランジスタを有する半導体チップが記載されている。前記トランジスタは、ゲート誘電体にわたって設けられたゲート電極を有する。前記ゲート電極は、前記ゲート誘電体上に設けられた第1ゲート材料、及び前記ゲート誘電体上に設けられた第2ゲート材料を有する。前記第1ゲート材料は前記第2ゲート材料とは異なる。前記第2ゲート材料はまた、前記ゲート電極のソース領域又はドレイン領域にも設けられている。  (もっと読む)

(もっと読む)

化合物半導体装置及びその製造方法

【課題】本発明は、化合物半導体素子の動作に関係なく、リーク電流を防止することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置1は、2DEG310を有する第1の化合物半導体層31と、第1の化合物半導体層31上に配設され、キャリア供給層として機能する第2の化合物半導体層32と、2DEG310上に配設された第1の電極61と、2DEG310上において第1の電極61から離間して配設された第2の電極42と、を備えた化合物半導体素子10と、化合物半導体素子10の周囲を取り囲む領域の一部において2DEG310上に配設され、この2DEG310のキャリア濃度を低減させる外周電極62を有する外周領域11とを備える。

(もっと読む)

薄膜トランジスタ、薄膜トランジスタを用いた表示装置及び薄膜トランジスタの製造方法

【課題】工程数の増大を引き起こさずに、遮光層で囲まれた薄膜トランジスタと同等以上の遮光能力を有する薄膜トランジスタおよびそれを用いた表示装置を提供する。

【解決手段】第1のゲート電極2と、第1のゲート電極2を覆う第1のゲート絶縁層3と、第1のゲート絶縁層3の上の半導体層6と、半導体層6の上の第2のゲート絶縁層7と、第2のゲート絶縁層7の上の第2のゲート電極8と、半導体層6に電気的に接続されたドレイン電極5及びソース電極4を有する薄膜トランジスタにおいて、半導体層6がZn、Ga、In、Snのうち少なくとも1種以上を含む非晶質酸化物半導体であり、第1のゲート電極2が下方から半導体層6への光の入射を遮り、第2のゲート電極8が上方から半導体層6への光の入射を遮り、第2のゲート電極8は第1のゲート絶縁層3及び第2のゲート絶縁層7を貫通して第1のゲート電極2と電気的に接続され、少なくとも一方の側方から半導体層6に入射する光を遮る。

(もっと読む)

半導体装置及びその製造方法

【課題】消費電流及び抗折強度に優れる半導体装置の製造方法を実現する。

【解決手段】

半導体装置の製造方法は、第1面の表面部に設けられた拡散領域12を備える半導体基板11を準備する工程(a)と、半導体基板11の第1面上に第1金属配線14a及び14bを形成する工程(b)と、半導体基板11を厚さ方向に貫通する貫通孔15を形成する工程(c)と、貫通孔15内に、第1金属配線14bの裏面から半導体基板11の第2面にまで延びる貫通電極16を形成する工程(d)と、半導体基板11の第2面に凹部17を形成する工程(e)と、凹部17内に、貫通電極16と電気的に接続された第2金属配線18を形成する工程(f)とを備える。

(もっと読む)

半導体装置

【課題】デジタル回路と高周波回路とを混載した半導体装置において、デジタル回路の微細化を進めつつ、高周波回路の配線間容量を小さくする。

【解決手段】高周波回路100の第1トランジスタ120,140の第1ゲート電極124,144から第1コンタクト162,166までの距離aは、デジタル回路200の第2トランジスタ220,240の第2ゲート電極224,244から第2コンタクト262,266までの距離bより大きい。第1コンタクト162,166は第1トランジスタ120,140のドレイン126,146に接続しており、第2コンタクト262,266は第2トランジスタ220,240のドレイン226,246に接続している。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】電極材料のエッチバックが不均一であっても、縦型MOSトランジスタのゲート長のばらつきを小さくして、トランジスタ特性のばらつきを小さくした半導体装置および半導体装置の製造方法を得るという課題があった。

【解決手段】半導体基板10と、半導体基板10から突出され、先端側に大径部31が設けられ、大径部31の基端側に小径部33が設けられ、かつ、大径部31の周端面31cよりも小径部33の周端面1cが後退されて段部1dが設けられたピラー部1と、ピラー部1の周端面1cに備えられた第1の絶縁膜2と、第1の絶縁膜2を介して少なくとも一部が段部1dに埋められた電極部3と、ピラー部1の基端側および先端側に設けられた不純物拡散領域15、16と、を具備し、電極部3の段部1dに埋められた部分の高さが、ピラー部1の全周に渡って均一の高さとされている半導体装置を用いることにより、上記課題を解決できる。

(もっと読む)

トレンチ金属酸化膜半導体素子及び終端構造の製造方法

【課題】トレンチ金属酸化膜半導体素子及び終端構造を同時に製造するトレンチ金属酸化膜半導体素子及び終端構造の製造方法を提供する。

【解決手段】活性領域にトレンチ金属酸化膜半導体素子を形成するための複数の第1のトレンチ及び終端構造を形成するための第2のトレンチを形成する。次に、半導体基板の全領域にゲート酸化層を形成し、第1のトレンチ及び第2のトレンチに第1の導電材料を埋め込む。エッチバックプロセスを行い、余分な第1の導電材料を除去し、第2のトレンチにスペーサ122を形成するとともに、第1のトレンチのみに導電材料140を残す。次に、第1のトレンチ及び第2のトレンチに導電層間酸化層を形成する。次に、メサ表面115A上のゲート酸化層を除去する。蒸着、リソグラフィック及びエッチングプロセスにより、終端構造酸化層150を形成する。第1の電極160Aを所定の位置に形成する。

(もっと読む)

トランジスタアクティブ基板およびその製造方法並びに電気泳動ディスプレイ

【課題】活性層を保護するとともにドレイン電極と画素電極との電気的導通を十分確保できるような保護層を設けたトランジスタアクティブ基板を提供する。

【解決手段】トランジスタアクティブ基板は、基板301、ゲート電極302、ゲート絶縁膜303、ソース電極304、ドレイン電極305および活性層306から構成される薄膜トランジスタ上に、保護膜307および画素電極308が配置されており、ドレイン電極305の表面粗さをRa(M)、保護膜307の膜厚をD(I)としたときに、D(I)≦Ra(M)×15の関係にある。

(もっと読む)

縦型のショットキーダイオード

【課題】 縦型のショットキーダイオードの局所的な過熱を抑制する技術を提供する。

【解決方法】 半導体基板8の表裏両面にカソード電極10とアノード電極60が分かれて形成されている縦型のショットキーダイオード1であり、アノード・カソード間抵抗が低い構造とアノード・カソード間抵抗が高い構造の両者が形成されている。半導体基板8を平面視して2区画80,82に分割したときに、区画によって低抵抗構造と高抵抗構造が形成されている範囲の比率が相違し、区画によって平均抵抗値が変えられている。過熱しやすい区画における平均電流密度が下がり、局所的過熱が防止され、熱暴走の発生が防止される。

(もっと読む)

集積低漏洩ショットキーダイオード

MOSゲートの一方の側部に近接しているショットキーバリアを有し、当該ゲートの他方の側部にドリフト領域の一端を有する集積低漏洩ショットキーダイオードである。ショットキー金属及びゲート酸化膜の下は、P層とそれを覆うN層のリサーフ構造であり、当該リサーフ構造がドリフト領域を形成し、当該ドリフト領域は本発明の1つの実施例においてダイオードのカソードで終端する。当該N層及びP層は、当該ゲートの下に上向きに凸の凹形状を有する。ゲート電極及びショットキー金属は、ダイオードのアノードに接続されている。P層が当該リサーフ構造とNISO領域との間にあり、NISO領域が当該アノードとの電気的接続を有している。ショットキー金属の下のP+層は、Pウェルを通してP−層と接続されている。  (もっと読む)

(もっと読む)

ALD技術を用いたドーピング

【課題】阻害反応物を用いてドーパント前駆体が利用可能な結合部位の一部を阻害することによって、堆積したドーパントの濃度および均一性を制御することができる。ALDプロセスにおいて、阻害反応物をドーパント前駆体の導入前に導入することができる、または阻害反応物およびドーパント前駆体を同時に導入することができる。

【解決手段】原子層堆積プロセス(ALD)によって、基板表面または2つの薄膜間の界面をドープする方法が提供される。

(もっと読む)

1 - 20 / 36

[ Back to top ]