Fターム[4M104HH11]の内容

Fターム[4M104HH11]に分類される特許

1 - 20 / 27

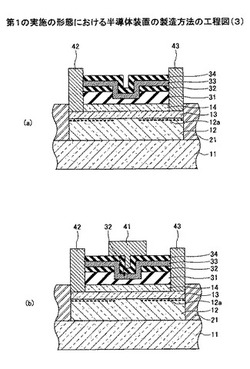

半導体装置及び半導体装置の製造方法

【課題】ゲートリーク電流が低減され、かつ、ノーマリーオフ動作する半導体装置を提供する。

【解決手段】基板11の上に形成された第1の半導体層12と、第1の半導体層12の上に形成された第2の半導体層13と、第2の半導体層13の上に形成された下部絶縁膜31と、下部絶縁膜31の上に、p型の導電性を有する酸化物により形成された酸化物膜33と、酸化物膜33の上に形成された上部絶縁膜34と、上部絶縁膜34の上に形成されたゲート電極41と、を有し、ゲート電極41の直下において、下部絶縁膜31の表面には凹部が形成されている半導体装置。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】微細化及び高集積化を達成した酸化物半導体を用いた半導体装置、及び半導体装置の作製工程において、安定した電気的特性を付与し、高信頼性化する。また、上記半導体装置の作製工程において、不良を抑制し、歩留まりよく作製する技術を提供する。

【解決手段】酸化物半導体層を含むトランジスタを有する半導体装置において、酸化物半導体膜を、絶縁層に設けられたトレンチに設ける。トレンチは下端コーナ部及び曲率半径が20nm以上60nm以下の曲面状の上端コーナ部を含み、酸化物半導体膜は、トレンチの底面、下端コーナ部、上端コーナ部、及び内壁面に接して設けられる。酸化物半導体膜は、少なくとも上端コーナ部において表面に概略垂直なc軸を有している結晶を含む酸化物半導体膜である。

(もっと読む)

半導体装置

【課題】微細化及び高集積化を達成した酸化物半導体を用いた半導体装置において、安定した電気的特性を付与し、高信頼性化する。

【解決手段】酸化物半導体膜を含むトランジスタ(半導体装置)において、酸化物半導体膜を、絶縁層に設けられたトレンチ(溝)に設ける。トレンチは曲率半径が20nm以上60nm以下の曲面状の下端コーナ部を含み、酸化物半導体膜は、トレンチの底面、下端コーナ部、及び内壁面に接して設けられる。酸化物半導体膜は、少なくとも下端コーナ部において表面に概略垂直なc軸を有している結晶を含む酸化物半導体膜である。

(もっと読む)

半導体装置の製造方法

【課題】微細化を達成するとともに、ゲート電極等の信頼性を確保する半導体装置の製造方法を提供する。

【解決手段】N型MISトランジスタ及びP型MISトランジスタのそれぞれのゲート形成領域において、N型MISトランジスタのゲート形成領域の凹部内に形成されたゲート絶縁膜F0上に第1の金属含有膜F1を、P型MISトランジスタのゲート形成領域の凹部内に形成されたゲート絶縁膜F0上に第3の金属含有膜F3を形成し、第1の金属含有膜F1上及び第3の金属含有膜F3上に第2の金属含有膜F2を形成し、N型MISトランジスタのゲート絶縁膜F0に接する第1の金属含有膜F1の仕事関数がP型MISトランジスタのゲート絶縁膜F0に接する第3の金属含有膜F3の仕事関数よりも小さい。

(もっと読む)

チャネルエッチ型薄膜トランジスタとその製造方法

【課題】半導体層の膜厚均一性を向上させたチャネルエッチ型TFTとその製造方法を提供する。

【解決手段】酸化物半導体からなるチャネル層4を形成した後、該チャネル層4の上にIn、Zn、Gaを含む酸化物からなり、上記酸化物半導体よりもエッチングレートが速く、抵抗率が3.38×107Ωcm以下である犠牲層5を形成し、その上にソース電極6及びドレイン電極7を形成して、該ソース電極6とドレイン電極7の間に露出した犠牲層5をウェットエッチング除去することにより、半導体層膜厚の均一性を向上させ、TFT特性とその均一性と、をより向上させることができる。

(もっと読む)

積層構造のソース・ドレイン電極を有する有機薄膜トランジスタ

【課題】柔軟性及び耐久性に優れ、素子特性が優れ、しかも大面積化が容易なボトムゲート・ボトムコンタクト構造の有機薄膜トランジスタを提供すること。

【解決手段】第1導電層及び第2導電層からなるソース・ドレイン電極を有するボトムゲート・ボトムコンタクト構造の有機薄膜トランジスタであって、第1導電層は、酸化タングステン、酸化銀、酸化銅、酸化亜鉛、銀塩、銀及び銅からなる群から選ばれる1種以上の材料を含み、該第2導電層は、Ag、Al、Au、Cd、Co、Cr、Cu、Fe、Mg、Mo、Ni、Pb、Pd、Pt、Sn、Ta、Ti、V、W、Zn、Zr、及びこれらの金属のいずれかを含む合金からなる群から選ばれる1種以上の材料を含む、有機薄膜トランジスタ。

(もっと読む)

半導体装置の作製方法

【課題】高性能、高信頼性のトランジスタを有する半導体装置を作製する技術を提供する。

【解決手段】配線層を導電層から形成する際に酸化物半導体層を保護するための保護導電膜を酸化物半導体層と導電層との間に形成して、2段階のエッチングを行う。第1のエッチング工程には、保護導電膜は導電層よりエッチングされにくく、導電層と保護導電膜とのエッチング選択比が高い条件で行うエッチング方法を採用し、第2のエッチング工程には、保護導電膜は酸化物半導体層よりエッチングされやすく、保護導電膜と酸化物半導体層とのエッチング選択比が高い条件で行うエッチング方法を採用する。

(もっと読む)

アッド‐オン層形成方法

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、堆積可能なアッド‐オン層形成方法を提供することを目的とする。

【解決手段】堆積可能なアッド‐オン層形成方法であって、第一半導体基板の取り外し層の形成、取り外し層の上の第一半導体基板に多くのドーピング領域の形成、ここで多くのドーピング層の形成は、第一電導型を有するように、ドーピングされ、取り外し層の上の第一半導体基板の第一ドーピング層の形成、第一電導型に対する第二電導型を有するようにドーピングされ、第一ドーピング層の上の第一半導体基板に最低中間ドーピング層の形成、及び中間ドーピング層上の第一半導体基板に最低第三ドーピング層の形成からなり、第三ドーピング層上に第一の電導性ブランケット層の形成、第一電導ブランケット層上に第二の電導性ブランケット層の形成、及び第二電導性ブランケット層が第二半導体基板の対応する電導性上部層と接触するように、第一半導体基板を第二半導体基板への取り付け、からなる。

(もっと読む)

半導体装置とその作製方法

【課題】特性が良好なトランジスタを提供する。

【解決手段】例えば、ボトムゲート・ボトムコンタクト構造のトランジスタを作製するに際して、ソースとドレインを構成する導電層を3層の積層構造とし、2段階のエッチングを行う。すなわち、第1のエッチング工程には、少なくとも第2の膜及び第3の膜に対するエッチングレートが高いエッチング方法を採用し、第1のエッチング工程は少なくとも第1の膜を露出するまで行う。第2のエッチング工程には、第1の膜に対するエッチングレートが第1のエッチング工程よりも高く、「第1の膜の下に接して設けられている層」に対するエッチングレートが第1のエッチング工程よりも低いエッチング方法を採用する。第2のエッチング工程後にレジストマスクをレジスト剥離液により剥離するに際し、第2の膜の側壁が少し削られる。

(もっと読む)

金属酸化膜の形成方法および金属酸化膜

【課題】所定パターンを有するとともに、表面抵抗率や光透過率等のばらつきが少ない金属酸化膜の形成方法およびそのような金属酸化膜を提供する。

【解決手段】基材上に、所定パターンを有する金属酸化膜の形成方法等であって、基材に対して、金属塩を含有する液状物を塗布して金属塩膜を形成する第1工程と、金属塩膜に対して、所定パターンを設ける第2工程と、金属塩膜に対して、熱酸化処理または所定のプラズマ酸化処理を行い、金属酸化膜とする第3工程と、を含む。

(もっと読む)

半導体装置の製造方法及びスパッタリング装置

【課題】半導体基板にシリサイド形成用の金属膜を形成する時に、ゲート絶縁膜にダメージが加わることを抑制する。

【解決手段】このスパッタリング装置は、チャンバ101、ウェハステージ102、リングチャック104、金属ターゲット105、防着シールド107、マグネット108、コリメータ109、並びに直流電源110,120を備えている。直流電源110は、コリメータ109に負電圧のみを印加するために設けられている。コリメータ109に印加される負電圧は、金属ターゲット105に印加される電圧より低電圧、例えば−70V以上−50V以下である。

(もっと読む)

半導体装置

【課題】高誘電体材料を含むゲート絶縁膜とメタルゲート電極とを有する半導体装置の製造中にポリシリコンからなる残渣が素子分離領域上に生じる虞があり、不良の原因であった。

【解決手段】半導体基板10の第1の活性領域10a上には、高誘電体材料と第1の金属とを含有する第1のゲート絶縁膜13aと、下層導電膜15aと第1の導電膜18aと第1のシリコン膜19aとを有する第1のゲート電極30aとを備えた第1導電型の第1のトランジスタが形成されている。半導体基板10の第2の活性領域10b上には、高誘電体材料と第2の金属とを含有する第2のゲート絶縁膜13bと、第1の導電膜18aと同一の材料からなる第2の導電膜18bと第2のシリコン膜19bとを有する第2のゲート電極30bとを備えた第2導電型の第2のトランジスタが形成されている。

(もっと読む)

半導体装置の製造方法、スパッタ装置及びコリメート板

【課題】ターゲットの利用率を十分に向上させ、且つ、プラズマダメージを十分に抑制する。

【解決手段】複数の貫通孔が形成されているコリメート板を介してスパッタを行うことにより、ゲート絶縁膜及びゲート電極を有する半導体素子上に金属膜を形成する金属膜形成工程(ステップS1)を備える。この金属膜形成工程では、貫通孔のアスペクト比(貫通孔の深さ/貫通孔の開口径)が1/6以上2/3以下であるコリメート板を用いる。金属膜形成工程を、半導体装置のシリサイド形成工程で行う。半導体素子のアンテナ比を45000以下とする。アスペクト比をコリメート板の中央部から外周部に向けて徐々に小さくし、コリメート板の最外周部ではアスペクト比を1/2以下とする。

(もっと読む)

導電材料の誘電体層上へのプラズマ増強原子層堆積

プラズマ増強原子層堆積(PEALD)を使用して誘電体層上に導電性の金属層を形成する方法を、関連する組成物および構造と共に提供する。PEALDによって導電層を堆積する前に、非プラズマ原子層堆積(ALD)プロセスによって誘電体層上にプラズマバリア層を堆積する。プラズマバリア層は、誘電体層上のPEALDプロセスにおけるプラズマ反応物質の有害作用を減少させるか、または防止し、接着を増強することができる。非プラズマALDプロセスおよびPEALDプロセスの双方において、同じ金属反応物質を使用することができる。 (もっと読む)

半導体装置

【課題】 LDD形成工程に於けるプラズマプロセスが原因となり生じる素子の

損傷を極力低減した半導体装置の作製方法を提供すること。

【解決手段】 基板全面を覆うように導電性膜を形成した状態で、ハードマスク

を利用した半導体装置の作製方法でLDD構造の素子を形成することにより、L

DD形成工程におけるプラズマプロセスによる素子への損傷を極力低減する。導

電性膜が全面に形成されていることにより、異方性エッチング等のプラズマによ

る処理(プラズマプロセス)においてゲート電極に蓄積される電荷密度を低減で

き、プラズマプロセスによる損傷を低減できる。

(もっと読む)

半導体装置の製造方法および基板処理装置

【課題】 プラズマダメージを与えることなく膜中の残留不純物を低減でき、膜の平坦性を向上でき、さらには、プリカーサの使用量を抑えつつ堆積速度を向上させることができる半導体装置の製造方法および基板処理装置を提供することを目的とする。

【解決手段】 基板上に絶縁膜を形成する工程と、絶縁膜上に高誘電率絶縁膜を形成す

る工程と、高誘電率絶縁膜上に窒化アルミニウムチタン膜を形成する工程と、を有し、窒化アルミニウムチタン膜を形成する工程では、窒化アルミニウム膜の形成と、窒化チタン膜の形成と、を交互に繰り返し行い、その際、最初および/または最後に前記窒化アルミニウム膜を形成する。

(もっと読む)

半導体装置の製造方法

【課題】ダミーパターンを配置することなく、導電体膜に対するプラズマエッチング時における導電体膜を残す領域への電荷の集中を防止する。

【解決手段】シリコン基板1上にノンドープトポリシリコン膜7を形成する(a)。ゲート領域11a及び周辺領域11bにN型ポリシリコン膜7aを形成する(b,c)。プラズマエッチングにより、ポリシリコン膜7,7aを除去してゲート17を形成する。ノンドープトポリシリコン膜7はN型ポリシリコン膜7aに比べてエッチングレートが小さいので、周辺領域11bのN型ポリシリコン膜7aの除去が完了した時点で低エッチングレート領域11cにノンドープトポリシリコン膜7が残存しており、プラズマエッチング処理によって発生した正電荷23はゲート17とノンドープトポリシリコン膜7に分散される(d)。エッチング処理を継続して領域11cのノンドープトポリシリコン膜7を除去する(e)。

(もっと読む)

半導体装置の製造方法

【課題】MIM容量構造を有する半導体装置における絶縁膜の静電破壊を抑制する。

【解決手段】半導体基板に設けられた絶縁膜に、下部電極用導電膜を形成し、前記下部電極用導電膜に、容量絶縁膜を形成し、前記半導体基板と導電膜形成ステージとを互いに無圧着状態で接触させて前記容量絶縁膜に、第1の上部電極用導電膜を形成し、前記半導体基板と導電膜形成ステージとを互いに圧着状態で接触させて前記第1の上部電極用導電膜に、第2の上部電極導電膜を形成する。

(もっと読む)

半導体装置の製造方法

【課題】プラズマ製造装置を用いた半導体装置の製造歩留まりを向上させる。

【解決手段】まず、半導体ウエハ1W上に絶縁膜を形成する。次に、プラズマ製造装置31のプラズマインピーダンスVppおよび反射波Prの波形を検出する。次に、検出したプラズマインピーダンスVppおよび反射波Prの波形を、プラズマ立ち上がり時、プラズマ安定時、プラズマ立ち下がり時についてそれぞれ細分割した時間分割単位で設定された異常放電のしきい値とチェックしながら、プラズマエッチングによって、半導体ウエハ1W上の絶縁膜に開口部を形成する。

(もっと読む)

半導体素子の形成方法

【目的】レジストパターンの寸法および形状の変動と、チャージアップダメージとを同時に解決する。

【解決手段】レジストパターン形成時に、コンタクトホール用のパターン37を画成する、矩形枠状のダミーコンタクトホール用のパターン35をチップ分離領域17の脇に沿って形成する。これにより、ウエハ単位でのパターン付き第1のレジスト層30の収縮が、チップ単位での収縮に低減される。また、このダミーコンタクトホール用のパターンから形成されるダミーコンタクトにより、導電体層を除去する際に発生する電荷を、チップ単位で基板へ逃がすことができる。

(もっと読む)

1 - 20 / 27

[ Back to top ]