Fターム[4M104HH17]の内容

Fターム[4M104HH17]に分類される特許

1 - 20 / 49

半導体装置の製造方法

【課題】Geをチャネル材料に用いても、素子特性の劣化を抑制することを可能にする。

【解決手段】Geを含むp型半導体領域上にゲート絶縁膜を形成する工程と、前記ゲート絶縁膜上にゲート電極を形成する工程と、前記半導体領域の、前記ゲート電極の両側に位置する第1および第2領域に、有機金属錯体および酸化剤を交互に供給して金属酸化物を堆積する工程と、前記金属酸化物の上に金属膜を堆積する工程と、熱処理を行うことにより、前記半導体領域および前記金属酸化物と、前記金属膜とを反応させて前記第1および第2領域に金属半導体化合物層を形成するとともに前記金属半導体化合物層と前記半導体領域との界面に金属偏析層を形成する工程と、を備えている。

(もっと読む)

不揮発性半導体記憶装置

【課題】電圧−電流特性を改善した整流素子を用いたメモリセルを有する不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、第1の配線と、前記第1の配線に交差する第2の配線と、前記第1及び第2の配線に設けられ、抵抗状態の変化に応じてデータを記憶するメモリ素子及び非オーミック素子を直列接続してなるメモリセルとを備え、前記非オーミック素子は、メタル層と、前記メタル層に接合された真性半導体層と、前記真性半導体層に接合された第1の不純物を含む不純物半導体層とを有することを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】素子面積の増大を抑制しつつ、信頼性に優れた構造を有する半導体装置およびその製造方法を提供する。

【解決手段】半導体装置100は、化合物半導体基板12と、化合物半導体基板12に埋め込まれた埋込電極と、を備え、化合物半導体基板12の主面に溝22、24が設けられており、少なくとも溝22、24の側壁上に設けられた第一の金属膜10a、10bと、少なくとも溝22、24の底面上に設けられており、第一の金属膜10a、10bと異種材料で構成される第二の金属膜9a、9bと、を含む積層体により溝22、24を埋め込むことで、上記埋込電極が構成されており、第一の金属膜10a、10bのフェルミエネルギーは化合物半導体基板12の真性フェルミエネルギーと異なり、第二の金属膜9a、9bのフェルミエネルギーは化合物半導体基板12の真性フェルミエネルギーと異なる。

(もっと読む)

結晶欠陥の除去方法

【課題】エピタキシャル成長法により堆積させたSiC層の表面から深い位置に形成された結晶欠陥でも、確実に除去することができる方法を提供する。

【解決手段】単結晶SiCからなる半導体基板1表面にエピタキシャル層2を積層させて形成したSiC基板の表面にレジスト膜12を形成し、基板裏面から紫外線を照射することで、表面のレジスト膜12を露光する。結晶欠陥11のある部分は、レジスト膜12は露光されないため、開口が形成される。その開口部内にイオン注入することで、エピタキシャル層2、半導体基板1を高抵抗化し、結晶欠陥を除去する。最後に、レジスト膜12を除去することで、半導体装置を形成することができるSiC基板が得られる。

(もっと読む)

半導体素子及び該半導体素子を備える半導体素子構造

【課題】本発明は、かかる事情に鑑み、トランジスタの遮断状態を自然に実現し、半導体領域に金属領域との界面近傍の空乏層の形成を抑制しつつ、ショットキー障壁を実質的に下げることができるようにソース領域のフェルミ準位を選択することにより、駆動電流を増加させる半導体素子及び該半導体素子を備える半導体素子構造を提供することを課題とする。

【解決手段】ソース領域6及びドレイン領域7は、フェルミ準位が異なる第1金属領域10及び第2金属領域11を有し、第1金属領域10は、半導体領域5の価電子帯の頂上のエネルギーレベル以上で且つ半導体領域5の真性フェルミ準位以下のフェルミ準位を有する金属であり、第2金属領域11は、第1金属領域10のフェルミ準位以上で且つ伝導帯の底のエネルギーレベル以下のフェルミ準位を有する金属であることを特徴とする。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】ショットキー接合部の面積の減少を防ぐことができるとともに、簡便なプロセスで低コストの半導体装置を得る。

【解決手段】炭化珪素基板2上に、n型不純物を比較的低濃度に含んだドリフト層である半導体層1を備え、当該半導体層1の主面には、複数の溝状の凹部TRが設けられ、当該溝状の凹部TRの側面内には、p型不純物を含んだ半導体領域3aが形成されている。また、溝状の凹部TRが配設された領域の周囲には、p型不純物を含んだ導体領域4が配設されている。

(もっと読む)

半導体装置の製造方法

【課題】炭化ケイ素を材料とする半導体ウェハから半導体装置を製造する方法において、表面電極と半導体基板とのショットキー接合、裏面電極と半導体基板とのオーミック接合を確保することと、製造工程を簡略化する。

【解決手段】半導体ウェハの表面に表面Mo電極を形成した後で、半導体ウェハの裏面に裏面Ni系電極を形成し、形成した表面Mo電極および裏面Ni系電極を同時にシンター処理する。表面Mo電極は、900℃以上のシンター処理を行っても、半導体基板とのショットキー接合を確保できる。裏面Ni系電極が半導体基板とオーミック接合するために必要な高温(例えば900℃以上)で、表面電極と裏面電極のシンター処理を同時に行うことができるため、製造工程が簡略化される。

(もっと読む)

半導体装置とその製造方法

【課題】 裏面電極に対してアニール処理を実施したときに、そのアニール処理に起因する熱ダメージを低減すること。

【解決手段】 半導体装置は、縦型のショットキーダイオードが形成されている炭化珪素基板10と、その炭化珪素基板10の表面側に設けられているアノード電極20と、その炭化珪素基板10の裏面側に設けられているカソード電極50と、炭化珪素基板10とカソード電極50の間に設けられている導電性の断熱領域40を備えている。断熱領域40は、炭化珪素基板10の半導体材料の熱伝導率よりも小さな熱伝導率である。

(もっと読む)

ショットキーバリアダイオード

【課題】耐圧を向上できるショットキーバリアダイオードを提供する。

【解決手段】ショットキーバリアダイオード10は、基板と、基板上に形成されたGaN層3と、GaN層3上に接して形成されたショットキー電極4とを備えている。ショットキー電極4は、卑金属で、かつ4×1019cm-3以上の酸素濃度を有する。ショットキーバリアダイオード10において好ましくは、GaN層3とショットキー電極4との界面の炭素のピーク濃度は、1×1019cm-3以上である。

(もっと読む)

半導体装置の製造方法及びそれを用いた半導体装置

【課題】MIPS構造を採るメタル膜とコンタクトプラグとの界面抵抗を低減できるようにする。

【解決手段】まず、半導体基板1の上に、ゲート絶縁膜3を形成し、形成したゲート絶縁膜3の上に、TiN膜4及びポリシリコン膜5を順次形成する。続いて、ポリシリコン膜5にTiN膜4を露出するコンタクトホール5aを形成する。続いて、ポリシリコン膜5における第1のコンタクトホール5aの少なくとも底面及び壁面上に金属膜7を形成する。

(もっと読む)

窒化物系半導体素子、及び窒化物系半導体素子を作製する方法

【課題】酸化ガリウム基板上の半導体層と酸化ガリウム基板の主面との界面におけるオフセット電圧を低減可能な窒化物系半導体素子を提供する。

【解決手段】III族窒化物結晶層15は、酸化ガリウム基板13の主面13aを覆う。III族窒化物結晶層15は、III族構成元素としてアルミニウムを含むと共にアルミニウム以外の少なくとも2種の構成元素を含むIII族窒化物からなる。半導体積層17は、窒化ガリウム半導体層25を含む。第1の電極19は、半導体積層17の主面17a上に設けられる。第2の電極21は、酸化ガリウム基板13の裏面13b上に設けられる。III族窒化物結晶層15のバンドギャップE(15)は窒化ガリウム半導体層のバンドギャップE(GaN)より大きい。III族窒化物結晶層15のバンドギャップE(15)は4.8エレクトロンボルトより小さい。

(もっと読む)

窒化物半導体素子

【課題】本発明は、過電圧印加時に電圧クランプ機能を有する窒化物半導体素子を提供することを目的とする。

【解決手段】第1の窒化物半導体からなる第1の層と、第1の層の上に設けられ、第1の窒化物半導体よりもバンドギャップが大なる第2の窒化物半導体からなる第2の層と、第2の層に電気的に接続された第1の電極と、第2の層の上に設けられ、第1の方向において第1の電極と並設された第2の電極と、第2の層の上に設けられたフローティング電極と、を備え、フローティング電極は、第1の方向に直交する第2の方向において第2の電極に挟まれた部分と、第1の電極に向けて第2の電極よりも突出した部分と、を有することを特徴とする窒化物半導体素子。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】酸化物半導体を用いた好適な構造のnチャネル型トランジスタおよびpチャネル型トランジスタを提供することを目的の一とする。

【解決手段】第1の酸化物半導体層と電気的に接続し、第1の材料を含む第1の導電層と第2の材料を含む第2の導電層の積層構造でなる第1のソース電極またはドレイン電極と、第2の酸化物半導体層と電気的に接続し、第1の材料を含む第3の導電層と第2の材料を含む第4の導電層の積層構造でなる第2のソース電極またはドレイン電極と、を有し、第1の酸化物半導体層には、第1のソース電極またはドレイン電極の第1の導電層が接触し、第2の酸化物半導体層には、第2のソース電極またはドレイン電極の第3の導電層および第4の導電層が接触する。

(もっと読む)

半導体素子およびその製造方法

【課題】 より高いレベルの、耐圧性能および低いオン抵抗(低いオン電圧)を実現し、大電流を流すことができる半導体素子およびその製造方法を提供する。

【解決手段】 導電性GaN基板1と、半導体層2と、半導体層上に位置するショットー電極11と、バック電極12と、ショットキー電極に接続して半導体層上に延在する2次元電子ガス形成層と、2次元電子ガス形成層と、導電性GaN基板またはバック電極とを電気的に接続する導電部5とを備え、電流パス形成部は、ショットキー電極とバック電極間への電圧印加によって、横方向に2次元電子ガスを形成することを特徴とする。

(もっと読む)

電極及びその形成方法、半導体シリコンウェーハ、並びに半導体デバイス

【課題】 電気特性評価等に用いるショットキー接合を簡便に形成することができ、かつ、良好なショットキー特性を有し、安定性が高い電極、及び、そのような電極を形成する方法等を提供する。

【解決手段】 半導体シリコンウェーハ上にショットキー接合された電極であって、前記電極は、仕事関数が4.0eV以下の物性を有する元素を一種又は複数種含有するAl基合金からなるものである電極、及び、そのような電極を真空蒸着により形成する電極の形成方法。

(もっと読む)

半導体装置

【課題】半導体または誘電体と、金属との界面において、接合する金属の実効仕事関数を最適化することを可能にするとともに、抵抗を可及的に低くすることを可能にする。

【解決手段】半導体膜4aと、半導体膜上に形成された酸化膜6bと、酸化膜上に形成された金属膜12aと、を備え、酸化膜がTi酸化膜であって、酸化膜に、V、Cr、Mn、Fe、Co、Ni、Nb、Mo、Tc、Ru、Rh、Pd、Ta、W、Re、Os、Ir、Ptから選ばれた少なくとも一つの元素が添加されている。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ゲートリーク電流の増加及び出力の低下を抑制しながら、コンタクト抵抗を低減することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】電子走行層3aと、電子走行層3a上方に形成された電子供給層4b、5bと、電子供給層4b、5b上方に形成されたゲート電極11gと、ゲート電極11gを間に挟んで形成され、電子走行層3aに電圧を印加するソース電極11s及びドレイン電極11dと、ソース電極11sと電子走行層3aとの間の電流経路に位置し、ソース電極11sと接する第1の化合物半導体層6bと、ドレイン電極11dと電子走行層3aとの間の電流経路に位置し、ドレイン電極11dと接する第2の化合物半導体層6bと、が設けられている。電子走行層3aの表面は(0001)面であり、第1の化合物半導体層6b及び第2の化合物半導体層6bの表面は(000−1)面である。

(もっと読む)

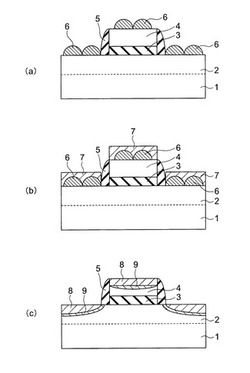

逆スタガ構造の薄膜トランジスタ及びその製造方法

【課題】生産性を向上させ、かつトランジスタ特性が良好な逆スタガ構造の薄膜トランジスタ及びその製造方法を提供すること。

【解決手段】本発明にかかる逆スタガ構造の薄膜トランジスタは、ソース領域41、ドレイン領域42、及びチャネル領域43を有する結晶性半導体膜40を備える。また、薄膜トランジスタは、チャネル領域43上に形成された絶縁膜5と、ソース領域41及びドレイン領域42上に形成されたシリサイド層61とを備える。そして、チャネル領域43は、ソース領域41及びドレイン領域42における結晶粒よりも小さい結晶粒により構成される。

(もっと読む)

コンタクト抵抗を低下させた半導体ストラクチャ

【課題】高品質のオーミックコンタクトをIII−V族半導体材料に形成して、消費電力が低くて長寿命の半導体デバイスを作製する。

【解決手段】半導体デバイス500は、第1のIII−V族半導体層510と、III−V族半導体中間層と、フェルミエネルギレベルを有する金属層530とを含む。金属層530のフェルミエネルギレベルは第1のIII−V族半導体層510およびIII−V族半導体中間層の有する価電子帯のエネルギレベルより高く、III−V族半導体中間層のエネルギレベルは金属層530のフェルミエネルギレベルと第1のIII−V族半導体層510の有する価電子帯のエネルギレベルとの間に存在し、III−V族半導体中間層は、第2のIII−V族半導体層520と、第3のIII−V族半導体層525とを含む。

(もっと読む)

半導体装置およびその作製方法

【課題】電気特性及び信頼性の高い薄膜トランジスタを有する半導体装置、及び該半導体装置を量産性高く作製する方法を提案することを課題とする。

【解決手段】ゲート電極層と、該ゲート電極層上にゲート絶縁層と、該ゲート絶縁層上に該ソース電極層及び該ドレイン電極層と、ソース電極層及びドレイン電極層上にバッファ層と、該バッファ層上に半導体層とを含む薄膜トランジスタを有し、ゲート電極層と重なる半導体層の一部は、ゲート絶縁層上に接し、且つ、ソース電極層とドレイン電極層の間に設けられ、半導体層はインジウム、ガリウム、及び亜鉛を含む酸化物半導体層であり、バッファ層はn型の導電型を有する金属酸化物を含み、半導体層とソース電極層及びドレイン電極層とはバッファ層を介して電気的に接続する。

(もっと読む)

1 - 20 / 49

[ Back to top ]