Fターム[4M106AA11]の内容

半導体等の試験・測定 (39,904) | 対象 (8,684) | 金属層 (88)

Fターム[4M106AA11]に分類される特許

1 - 20 / 88

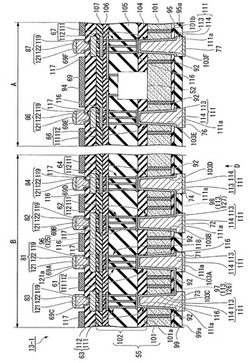

半導体チップ及びその抵抗測定方法、並びに半導体装置

【課題】本発明は、貫通電極のサイズ(直径)が縮小化された場合でも、4端子法により貫通電極の抵抗値を正確に測定することの可能な半導体チップ及びその抵抗測定方法、並びに半導体装置を提供することを課題とする。

【解決手段】半導体基板101及び回路素子層102を有する半導体チップ本体55と、半導体チップ本体55を貫通する第1乃至第4の貫通電極61〜64と、回路素子層102に設けられた回路素子を介することなく、第1の貫通電極61と第2の貫通電極62とを電気的に接続する第1の導電経路96と、回路素子を介することなく、第1の貫通電極61と第3の貫通電極63とを電気的に接続する第2の導電経路97と、回路素子を介することなく、第2の貫通電極62と第4の貫通電極64とを電気的に接続する第3の導電経路98と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】ブレード欠けやチップ端部のチッピングを防ぎ、かつウエハプロセスの評価を行うこともできる半導体装置及びその製造方法を得る。

【解決手段】半導体基板1の有効領域2と有効領域2の周囲の無効領域3にそれぞれ拡散層4,5を同時に形成する。拡散層4,5上にそれぞれエミッタ電極6及び小信号電極7を同時に形成する。小信号電極7にプローブ12を接触させて拡散層5の電気特性又は拡散層5と小信号電極7のコンタクト抵抗を測定するテストを行う。テストの後に、エミッタ電極6上に開口10を有し、小信号電極7を覆う絶縁膜9を形成する。開口10を介してエミッタ電極6上にメッキ11を形成する。

(もっと読む)

半導体装置の不良解析方法ならびに不良解析装置および不良解析プログラム

【課題】半導体装置の不良解析技術において、解析成功率の向上や解析時間の短縮を図ることができる技術を提供する。

【解決手段】ショートしていると推測される一方の特定配線を特定(S103)し、その相手と推測される隣接配線の抽出(S104)をおこない、両配線間において電圧状態(論理状態)が異なる異電圧時間帯の算出(S107)をし、その異電圧時間帯で発生する発光現象の頻度を調査することにより、上記一方の特定配線に対して、どの隣接する配線がショートしているのかを短時間で確実に推定する。

(もっと読む)

貫通配線の検査方法、貫通配線基板の製造方法

【課題】1つの貫通配線のみの抵抗を測定できる貫通配線の検査方法、及び該貫通配線の検査方法を行う工程を含む貫通配線基板の製造方法の提供。

【解決手段】基板1の一方の面1aに配された導電部2と、基板1を貫通し、導電部2と接続される第一貫通配線3、第二貫通配線4および第三貫通配線5とを少なくとも備えた貫通配線基板10を用い、基板1の他方の面1b側から第一貫通配線3及び第二貫通配線4に、定電流源6の一組の端子6a,6bを電気的に接続して、第一貫通配線3、導電部2、第二貫通配線4の経路に電流を流すと同時に、基板1の他方の面1b側から第一貫通配線3及び第三貫通配線5に、電圧計7の一組の端子7a,7bを電気的に接続して、第一貫通配線3における電圧降下を測定することを特徴とする貫通配線の検査方法。

(もっと読む)

配線検査方法

【課題】配線の微細化が進むと、実際の配線幅に比較して画像中の配線の幅方向のピクセル数が不十分になり、検査精度を向上させるために、撮影倍率を向上させると、処理能力が落ちて、生産性が落ちてしまうという課題を解消できる技術を提供する。

【解決手段】表面に配線が形成された検査対象物の表面を電子カメラで撮像し、その撮像した画像に含まれる配線パターンを検出し、検出した配線パターンのうち画素の配列に対して傾斜した配線像を抽出し、その抽出した配線像の欠陥の有無を判定する。

(もっと読む)

電子部品、電子部品の製造方法、基板

【課題】チッピング検出用配線が他の部材で覆われている状態であっても、ダイシングによって電子部品を形成した後に、チッピング検出用配線の導通状態を検出するための電圧を印加できる基板を提供する。

【解決手段】電子部品40は、互いに平行を成す一方の主面41aと他方の主面41bが矩形状の基体41を有する。基体41の一方の主面41aには、第一チッピング検出用配線42が配されている。また、基体41の他方の主面41bには、第二チッピング検出用配線44が配されている。第一チッピング検出用配線42は貫通配線43aを介して第二チッピング検出用配線44に電気的に接続される。

(もっと読む)

半導体装置の製造方法、半導体装置の製造装置および半導体装置

【課題】配線溝へのめっきの埋め込み性を安定させることができる半導体装置の製造方法等を提供すること。

【解決手段】実施形態によれば、半導体装置の製造方法が提供される。半導体装置の製造方法は、めっき処理によって金属膜を埋め込んで検査パターン10を形成する形成工程と、検査パターン10の特性を検出する検出工程と、検出工程によって検出された検査パターン10の特性に基づいて、前記めっき処理の条件を調整する調整工程とを含む。前記形成工程は、3層以上の配線層11〜13に亘って形成され、かつ中間層にスタックドビア22を有するパターンを、前記検査パターン10として形成する。

(もっと読む)

金属層の結晶粒径及び粒径分布評価方法並びにそれを用いた半導体集積回路装置の製造方法

【課題】非破壊かつオンラインで金属層の結晶粒径及び粒径分布を評価する方法を実現する。

【解決手段】結晶組織を有し特定の面方位においてX線に対して回折ピークを持つ金属層にX線を照射して得られる回折ピークを入手するステップA、回折ピークに基づいて面積平均コラム長及び体積平均コラム長を求めるステップB、面積平均コラム長及び体積平均コラム長から結晶粒径の対数正規分布を求めるステップCを具備する。

(もっと読む)

画像生成装置

【課題】設計データを制約条件として用い単調なパターンでも精度の良い連結画像を生成することを目的とする。設計データと画像データとのマッチングで大まかに基準位置を求めて、設計データとのズレ量を検索範囲として、隣接画像間でのマッチングを行い高速で精度の良い連結画像を生成する。

【解決手段】本発明の画像生成方法は、走査型電子顕微鏡を用いて電子デバイスパターンを検査する画像生成方法であって、電子デバイスパターンのレイアウト情報が記述された設計データを入力して記憶した設計データファイルと、撮像位置を変えて前記電子デバイスパターンを撮像して得た複数枚の分割画像データと、前記複数枚の分割画像データと前記設計データファイルの設計データとを用いて前記複数枚の分割画像データを1枚の画像に連結する画像連結手段とで構成される。

(もっと読む)

ワイドギャップ半導体のバンドギャップ電子物性の計測方法

【課題】 光励起を利用したワイドギャップ半導体のバンドギャップ電子物性の計測方法を実現する。

【解決手段】 ワイドギャップ半導体であるn−GaN膜13の表面に、当該ワイドギャップ半導体とショットキー接合が可能な透光性を有する有機金属膜を形成するショットキー電極形成工程により、バンドギャップが広くて仕事関数が大きいという特徴を有する導電性の有機金属膜15をワイドギャップ半導体のショットキー電極として形成し、単色光照射部23により、単色光として、例えば、十分に波長分解能の高い単色光を有機金属膜15側から分光照射し、電圧パルス発生部21により、有機金属膜15が形成されたワイドギャップ半導体n−GaN膜13に所定のタイミングで所定電圧強度のパルス電圧を印加し、インピーダンス計測部22により、有機金属膜15が形成されたワイドギャップ半導体n−GaN膜13のインピーダンスを検出する。

(もっと読む)

半導体装置の解析装置及び半導体装置の解析方法

【課題】不具合箇所を容易に特定することのできる半導体装置の解析装置及び解析方法の提供。

【解決手段】半導体装置の解析装置は、荷電粒子ビームを試料に照射し、検出した2次電子強度に応じた2次電子像を表示する機能を備える。解析対象の半導体装置に対し、第1の照射パターンで、荷電粒子ビームを照射して、電荷を注入する。次に、前記解析対象の半導体装置の電荷の蓄積状態を観測する。電荷の蓄積状態が正常でない箇所を、半導体装置の不具合箇所として検出することができる。

(もっと読む)

半導体解析装置及び半導体解析方法

【課題】メタル配線の断線を検査することが可能な半導体解析装置を提供する。

【解決手段】検査対象である半導体装置に電圧を印加するための電源部と、レーザ光を発する光源と、前記レーザ光を前記半導体装置に走査しながら照射する光学系と、前記絶縁膜を介し前記半導体装置に設置された検出電極と、を有し、前記検出電極は前記半導体装置の配線と容量的に結合されており、前記レーザ光を走査しながら照射することのより得られる前記検出電極により検出される信号に基づき、前記半導体装置の故障部分を解析することを特徴とする半導体解析装置により上記課題を解決する。

(もっと読む)

半導体装置の製造方法、半導体検査装置、及びプログラム

【課題】半導体チップをTDDB寿命によって分別できるようにする。

【解決手段】信頼性基準記憶部210は、第1配線層と、第1配線層の上に位置する第2配線層の重ね合わせ誤差の大きさに基づいて、半導体装置を3つ以上の信頼性ランクに分けるための基準データを記憶する。誤差記憶部230は、複数の半導体チップ12が切り出される半導体ウェハ10の面内の複数点で測定された重ね合わせ誤差を記憶する。誤差算出部240は、半導体ウェハ10の面内における複数の半導体チップ12の座標、及び誤差記憶部230が記憶している重ね合わせ誤差に基づいて、複数の半導体チップ12別に重ね合わせ誤差を算出する。信頼性情報付与部250は、複数の半導体チップ12別の重ね合わせ誤差と基準データに基づいて、複数の半導体チップ12それぞれに信頼性ランクを示す信頼性情報を付与する。

(もっと読む)

半導体装置の製造方法

【課題】パターン付きウェーハの金属及び有機物の汚染を非破壊で短時間で測定し、処理条件を適正化して後続のウェーハの処理を行う高生産性の半導体装置の製造方法を提供する。

【解決手段】第1基板11の第1主面11a上に、導電膜及び誘電膜の少なくともいずれかを含み第1パターンを有する第1層21を形成し、前記第1層が形成された前記第1主面に対向して設けられた探針30と、前記第1基板と、の間の相対位置を前記第1主面に平行な平面内で変化させ、前記探針に発生する電気信号を検出し、前記電気信号に基づいて設定された条件を用いて、第2基板の第2主面上に、導電膜及び誘電膜の少なくともいずれかを含み第2パターンを有する第2層を形成することを特徴とする半導体装置の製造方法が提供される。

(もっと読む)

半導体装置および該半導体装置の検査方法

【課題】入力端子または出力端子の再配線による抵抗値の異常を簡単な構成で短時間に検査することができる半導体装置とその検査方法を提供する。

【解決手段】半導体チップ10上の入力パッドまたは出力パッドP2と電源パッドP1間(入力パッドまたは出力パッドP2と接地パッドP3間でもよい)に接続された保護用MOSトランジスタM1を有し、半導体装置20の外部端子T4から入力されるテスト信号を保護用MOSトランジスタM1のゲートに印加することにより、入力パッドまたは出力パッドP2を電源パッドP1に接続するかを制御する。また、半導体装置20は半導体チップ10のパッドP1〜P4と半導体装置の外部端子T1〜T4間を接続する再配線手段を備える。半導体装置20はCSPまたはWLCSPで製造されたものである。

(もっと読む)

半導体装置とその検査方法

【課題】素子領域の外側を一巡している周辺耐圧領域を備えた半導体装置のトレンチゲート電極の不良の有無を判定することができる検査方法を提供する。

【解決手段】トレンチゲート電極に負の電圧を印加することによって、素子領域の耐圧を周辺耐圧領域の耐圧(耐圧直線29)よりも低くし、素子領域の耐圧を測定する。トレンチゲート電極に不良がある場合の耐圧直線28の傾きは、トレンチゲート電極に不良がない場合の耐圧直線27の傾きよりも大きい。このため、トレンチゲート電極に印加する負の電圧が等しければ、トレンチゲート電極に不良がある場合の素子領域の耐圧は、トレンチゲート電極に不良がない場合の素子領域の耐圧に比べて低い耐圧が測定される。

(もっと読む)

金属膜の膜厚測定方法及び基板処理方法及び装置

【課題】 インラインにおいても金属膜の実際の膜厚を測定することが可能な金属膜の膜厚測定方法を提供する。

【解決手段】 膜厚測定用の測定光を測定対象物11に照射する工程と、測定対象物11からの反射光からこの測定対象物11の反射率を検出する工程と、検出された測定対象物11の反射率から得た測定反射率データと、膜厚判断の基礎となる基礎反射率データとに基づいて、測定対象物11の膜厚を決定する工程と、を備え、測定対象物11が導電性を有する金属膜であり、金属膜の膜厚が、金属膜に透過した測定光がこの金属膜中で全て吸収されない膜厚以下である。

(もっと読む)

半導体評価装置

【課題】ウェーハレベル信頼性試験において、長期にわたって良好な電気的接触を確保することが可能となる半導体評価装置を提供する。

【解決手段】プローブ5を定電流回路7に接続するか、プローブ5を電圧測定回路8に接続するかを切り替えるスイッチS1と、プローブ3を定電流回路7に接続するか、プローブ3を電圧測定回路8に接続するかを切り替えるスイッチS2と、プローブ4を定電流回路7に接続するか、プローブ4を電圧測定回路8に接続するかを切り替えるスイッチS3と、プローブ6を定電流回路7に接続するか、プローブ6を電圧測定回路8に接続するかを切り替えるスイッチS4と、電極F+、電極F−、電極S+及び電極S−の少なくとも1つの電極上において所定時間後に絶縁膜が成長する電極に接続されたプローブを定電流回路7に接続するようにスイッチS1〜スイッチS4を制御する切替制御回路15とを備えている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体基板に設けられる貫通孔および貫通電極の形成状態および出来映えを容易に確認可能にし、貫通孔および貫通電極の品質向上と、接続不良の早期発見を可能にする技術を提供する。

【解決手段】半導体基板11と、半導体基板11の表面に設けられた内部電極12Aおよび内部電極12Bと、半導体基板11を厚み方向に貫通して内部電極12Aに到達し、内部電極12Aと電気的に接続された第一の貫通電極17Aと、半導体基板11および内部電極12Bを厚み方向に貫通する第二の貫通電極17Bと、半導体基板11の裏面に設けられ、第一の貫通電極17Aと電気的に接続された金属配線18とを備える。

(もっと読む)

半導体ウエハ及び半導体装置

【課題】スクライブ領域の幅を狭くするのに適した半導体ウエハを提供する。

【解決手段】半導体ウエハは、半導体素子の形成された複数のチップ領域が、隣接するチップ領域間にスクライブ領域を介して画定されており、スクライブ領域内に配置されたモニタ素子と、チップ領域内に配置されたパッドと、モニタ素子とパッドとを接続する配線とを有する。

(もっと読む)

1 - 20 / 88

[ Back to top ]