Fターム[4M106AB18]の内容

半導体等の試験・測定 (39,904) | チェック素子の細部 (1,099) | 識別 (30)

Fターム[4M106AB18]に分類される特許

1 - 20 / 30

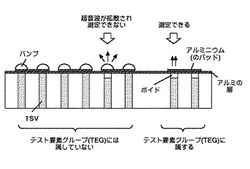

超音波スキャンに基づくシリコン貫通配線(TSV)におけるボイドの存在の推定

【課題】 3次元集積化構造中の不良を超音波スキャンによって検出することであって、シリコンウエハなどのボードに配列されているシリコン貫通配線(TSV)においてプロセス中に発生してしまう可能性のあるボイドの存在を非破壊的に検出すること。

【解決手段】 ボード面にわたって超音波スキャンをすると、(はんだ)バンプ等が物理的な遮蔽物として超音波を散乱させてしまい、超音波スキャンによる測定を妨げてしまう。そこで、これら複数のTSVの中から、テスト要素グループ(TEG)に属する単数または複数のTSVを選び出すにあたって、物理的な遮蔽物を少なく存在するように選び出す。

(もっと読む)

半導体装置、その製造方法及びその検査方法

【課題】半導体装置の配線層或いはビア層の観察に際し、所望の配線層或いはビア層を容易に識別し特定する。

【解決手段】半導体装置100は、複数の配線層1〜5と、これら配線層1〜5の間に設けられたビア層11〜14と、少なくとも1つの配線層1〜5が何れの層であるかを識別させる識別用アクセサリ61〜65と、を有している。識別用アクセサリ61〜65は、複数の配線層1〜5のうちの所定の配線層に形成された識別パターン81〜85を含む。各識別パターン81〜85は、少なくとも1つの配線層1〜5が何れの層であるかを識別させる平面形状に形成されている。

(もっと読む)

欠陥検査パターン回路、半導体ウェーハ及び欠陥検査方法

【課題】欠陥検査パターン回路に関し、p側コンタクト及びn側コンタクトのいずれのコンタクト不良も検出可能にする。

【解決手段】p型半導体基板1と、少なくとも2つのp型ウエル領域2,4と、少なくとも1つのn型ウエル領域3と、p型ウエル領域の一つに設けた第1のp+型活性領域6と、他のp型ウエル領域4に設けたn+型活性領域8と、n型ウエル領域3に設けた第2のp+型活性領域7と、第1のp+型活性領域6に設けたコンタクトプラグ10と、n+型活性領域8及び第2のp+型活性領域7に設けた各一対のコンタクトプラグ12,13と、各コンタクトプラグを、第1のp+型活性領域6に設けたコンタクトプラグ10から順に上下互いに接続してコンタクトチェーンを形成する配線15,16,17とを有する欠陥検査パターン回路におけるn型ウエル領域3の体積を第1のp+型活性領域6を形成したp型ウエル領域2の体積より小さくする。

(もっと読む)

集積回路装置

【課題】チップサイズを増加させずに、チップ位置情報等の識別情報を記録した集積回路装置を提供すること。

【解決手段】集積回路を有する集積回路基板と、前記集積回路に接続された導電性パッドと、前記導電性パッドを露出する開口部を持つ絶縁膜を備えた外部電極構造体とを有し、前記外部電極構造体が、前記集積回路基板の識別情報に対応する形状を有すること。

(もっと読む)

位置識別マーク、および半導体集積回路

【課題】メタル配線層や絶縁層を剥離した場合においても、半導体基板上におけるメモリセル等の物理的な位置を容易に確認できる、位置識別マークを提供する。

【解決手段】本発明の位置識別マークは、拡散層で形成される直線状の基板電位供給用パターン11の側面部(辺側)に、凹凸形状を設けて形成される。そして、基板電位供給用パターン11の一方の側(図1で上側)に、Y(column)方向の個数(左側から何個目の64kブロックかを示す個数)、もう一方の側(図1で下側)に、X(Row)方向の個数(下側から何個目の64kブロックかを示す個数)を示す位置識別マークが形成される。この位置識別マークは、1〜64の間の数値を示すように形成される。図1に示す例では、1,5,10の単位で、幅W・長さLを変えた凸状のパターンa,b,c等を配置する。

(もっと読む)

半導体チップ、半導体ウエハ、及び半導体チップの製造方法

【課題】ウエハ面内の複数のチップに対し、チップ毎に異なる内容の電気的な操作(チップIDの書き込み等)を、チップ毎ではなく複数チップ単位で一括して行えるようにする。

【解決手段】半導体チップ10は、対向する左辺S1及び右辺S2を有する矩形の主面108を有する。主面108上には、半導体素子104A及びBと、配線L11及びL12が形成されている。配線L11は、左辺S1から右辺S2に到達するように形成されるとともに、半導体素子104Aに結合されている。配線L12は、少なくとも左辺S1に接するように形成されるとともに、半導体素子104Bに結合されている。さらに、右辺S2上における配線L11の端部(TR0)と左辺S1上における配線L12の端部(TL0)は、辺S1及びS2に垂直な同一直線上に実質的に位置するように配置されている。

(もっと読む)

半導体装置およびその検査方法

【課題】層間絶縁層の平坦度を、容易に、非破壊で検査することができる半導体装置および半導体装置の検査方法を提供する

【解決手段】本発明に係る半導体装置1000は、層間絶縁層40の表面の平坦度を評価するための評価用素子100を含む半導体装置であって、評価用素子100は、半導体基板10の上方に設けられた、平面視において、矩形状のダミー電極20と、ダミー電極20の少なくとも1つの辺と対向するように設けられた評価用パターン30と、ダミー電極20および評価用パターン30を覆う層間絶縁層40と、を含み、評価用パターン30は、複数のマーカー32を有し、複数のマーカー32は、各々、ダミー電極20から所定の距離に設けられている。

(もっと読む)

スパッタ率補正用標準試料およびその試料を用いたスパッタ率比の算出方法

【課題】イオンスパッタを用いて半導体ウエハ上の結晶シリコン等の深さ方向元素もしくは深さ方向不純物分析を行う際に、アモルファスシリコンで構成される深さ校正用標準試料から結晶シリコン等の正確なスパッタ率を評価することのできるスパッタ率補正用標準試料およびその試料を用いたスパッタ率比の算出方法を提供すること。

【解決手段】第1の材料2からなる第1の層と、第2の材料3からなる第2の層と、を備え、第1の層は、第2の層の上に積層され、第1の層と第2の層は、それぞれ面方向に隣接する第1の領域4と第2の領域5を有し、第1の層における第1の領域4と第2の領域5とは、上面位置が同一であり、第1の領域4における第1の層の厚さは、第2の領域5における第1の層の厚さより薄く形成されていること。

(もっと読む)

半導体チップ

【課題】 加工処理を行なうための加工位置を精度よく特定することができる半導体チップを提供する。

【解決手段】 複数の半導体回路素子が形成され、それら半導体回路素子上に層間絶縁膜と配線層とが交互に積層されてなる半導体チップ10において、この半導体チップ10を構成する最上層の配線層であるダミーメタル13に、半導体チップ10上のX座標の位置を表わすX座標用コードパターン13_1およびY座標の位置を表わすY座標用コードパターン13_2を付加した。

(もっと読む)

画像検査装置の校正用サンプルウエーハ及び画像検査装置の校正方法

【課題】ピンホール検査の検査精度を維持するために行う画像検査装置の校正に用いる校正用サンプルウエーハにおいて、表面にハードレーザーマークを施すことで、効率的に校正を行うことができる校正用サンプルウエーハを提供する。

【解決手段】シリコンウエーハのピンホール欠陥を画像処理により検査する画像検査装置の校正に用いる校正用サンプルウエーハであって、校正用サンプルウエーハの表面にハードレーザーマークが施されたものであることを特徴とする画像検査装置の校正用サンプルウエーハである。

(もっと読む)

半導体基板の表面処理のモニター方法およびマーカ付半導体基板

【課題】正確にかつ簡便に半導体基板の表面処理工程をモニターできる方法を提供する。

【解決手段】本半導体基板の表面処理のモニター方法は、半導体基板の表面にマーカ10を形成する工程と、マーカ10が形成された表面を処理する工程とを備え、表面を処理する工程における表面のマーカ10の形態の変化により表面を処理する工程をモニターする。

(もっと読む)

電子デバイス及びその解析方法

【課題】観察者が論理情報提供者と常に連携することなく優れた作業効率をもって電子デバイスにおける不良箇所を特定するに際して、解析対象物に関する各種情報を認識したり解析対象物上の平坦性を確認したりするための指標体を設けてもその配置位置の制限が緩和され、しかも面積を増加させることなく、更には解析対象物の表面出し作業に際して平坦性を容易且つ確実に確認する。

【解決手段】指標体10は、その直上に存する配線部24下に位置整合するように(平坦視では配線部24に内包されるように)、層間絶縁膜21内で当該層間絶縁膜21に非貫通で形成された窪み内に導電材料が充填されて形成されている。指標体10は、その上部の配線部24とは接続されているが、下部の配線部24とは非接続とされている。指標体10の直下の層間絶縁膜22に設けられた配線部24が解析対象物となる。

(もっと読む)

半導体装置の製造装置および製造方法

【課題】電気特性測定時とピッキング時のチップ座標の対応を正確に取り、簡便にランク分けをして半導体装置の品質を向上させる半導体装置の製造装置および方法を提供する。

【解決手段】プローブ基準チップとピッキング基準チップを設け、プローブ基準座標とプローブ基準チップの電気特性と、ピッキング基準座標と、ピッキング基準チップのパターンと、複数のチップの電気特性とチップの座標を対応付けて記憶するメモリと、プローブ基準チップの電気特性と一致するチップを特定する第1チップ特定部と、特定された第1座標とプローブ基準座標とが異なる場合、第1座標をプローブ基準座標に座標変換し、第1座標以外の座標を座標変換に基づいて座標変換する座標補正部と、ピッキング基準チップのパターンと一致するチップを特定する第2チップ特定部と、特定したチップの座標をピッキング基準座標とするピッキング基準設定部と、を有する半導体装置の製造装置である。

(もっと読む)

半導体チップおよび半導体デバイス

【課題】ダイシング後に各半導体チップのウエハ上の位置を確実に認識できるようにする。

【解決手段】半導体チップ2は、抵抗素子R1〜Rn、測定パッドP1、P2、アルミパターンA1、A2を備える。アルミパターンA1、A2は、測定パッドP1、P2間の抵抗値が、ウエハ上における半導体チップ2の座標に一意に対応するように、抵抗素子R1〜Rnの中の1以上の抵抗素子を測定パッドに接続するように形成される。アルミパターンA1、A2は、視覚的にその形状を観察できる。

(もっと読む)

半導体装置の製造方法

【課題】複数のチップ領域の電気的特性を検査する工程を含む半導体装置の製造技術において、製造歩留まりを向上させる。

【解決手段】ウェハの主面に配列した複数のチップ領域の中から、基準チップ領域を選定し(工程101)、その後、複数のチップ領域に複数の半導体素子および配線を形成する工程102および工程103の際に、基準チップ領域における最上の配線である基準導体膜を、そのパターン形状が、他の複数のチップ領域における最上の配線のパターン形状と異なるようにして形成し、その後、基準チップ領域の位置を半導体基板上の基準アドレスとして特定し(工程104)、その基準アドレスをもとに他の複数のチップ領域にそれぞれアドレスを決め(工程105)、電気的特性を順に検査し(工程106)、複数のチップ領域を選別する(工程106)。

(もっと読む)

半導体装置と検証方法

【課題】IDIPから出力されるIDのユニーク性やランダム性の自己診断を可能にした半導体装置及びその検証方法を提供する。

【解決手段】互いに同じ製造過程をもって同一の形態として半導体基板上に形成された複数の識別要素の持つ電気的特性バラツキに起因する上記複数の識別要素の相互の物理量の大小関係に決定される複数ビットからなる識別情報(ID)を発生させる識別情報発生回路(IDIP)を備えた半導体装置に上記複数ビットの識別情報におけるランダム性を判別する判別回路を設ける。この判別回路は、確率論に基づく簡単な手法により実現することができる。

(もっと読む)

電子デバイス及び解析方法

【課題】電子デバイスの劣化を精度よく解析し、かつ、電子デバイスを精度よく識別する。

【解決手段】電子デバイスの実動作時に動作する実動作回路と、電子デバイスの試験時に動作する第3のテスト用回路及び第2のテスト用回路と、電子デバイスの実動作時に、第2のテスト用回路に電源電圧が印加されない状態を維持して、実動作回路及び第3のテスト用回路に電源電圧を印加し、電子デバイスの識別時に、第2のテスト用回路に電源電圧を印加する電源部とを備える電子デバイスを提供する。第2および第3のテスト用回路は、電気的に並列に設けられた複数のテスト用素子と、電子デバイスの試験時において、それぞれのテスト用素子を順次オン状態に制御する選択部と、選択部が順次オン状態に制御したテスト用素子のそれぞれの端子電圧を、電子デバイスの識別情報として出力する識別情報出力部とを有してよい。

(もっと読む)

透過型電子顕微鏡用観察試料作製方法

【課題】FIB加工による薄板化を行うTEM用観察試料の作製において、FIB加工試料台への試料設置における試料表面の傾斜誤差を精度高く補正する。

【解決手段】観察を行う試料表面とその近傍の斜面部に、それぞれ直線状をなす目印があり、各部の目印の直線状位置関係に関し、一直線に繋がっていない場合、あるいは平行関係にない場合、FIB加工面は所定の位置から傾いており、試料台の回転機構などを用いて、前記関係が一直線に繋がるように調整することで、試料面の傾斜を補正する。

(もっと読む)

半導体装置の製造方法

【課題】LCD製品に備わるドライバICの外観検査において、不良箇所の位置の特定に要する時間を短縮することのできる技術を提供する。

【解決手段】LCD製品に備わるドライバIC1Aの一部を構成する出力回路部5の長手方向の側縁部に沿って複数個の出力バンプ7を形成し、作業者が出力バンプ7の数を間違えることなく容易に数えることのできる個数置き、例えば10の倍数、20の倍数、25の倍数または50の倍数の出力バンプ7の個数置きに最上層配線と同一層からなる目印パターン8を配置し、目印パターン8を数えることによって外観不良9の位置を特定する。

(もっと読む)

半導体装置

【課題】 半導体装置に設ける電子ビームテスティング用のテスト端子に対して、識別マークを設けて容易に特定することを可能にした半導体装置を提供する。

【解決手段】 複数の配線層が絶縁層を介して多層構造になっており、最上層には該配線層がビアを介して接続された電子ビームテスティング用のテスト端子5が設けられている半導体装置10において、該テスト端子5の近傍に該テスト端子5を識別する識別マーク6が設けられており、該識別マーク6が複数の識別パターン61をバーコード状に並設したものであるように構成する。

(もっと読む)

1 - 20 / 30

[ Back to top ]