Fターム[4M106AC04]の内容

半導体等の試験・測定 (39,904) | テスト用回路 (391) | 被テスト回路の配置 (117)

Fターム[4M106AC04]の下位に属するFターム

スクライブ部 (100)

Fターム[4M106AC04]に分類される特許

1 - 17 / 17

テスト回路、集積回路、及び、テスト回路のレイアウト方法

【課題】 より簡易な設計手法で作製可能なテスト回路を提供する。

【解決手段】 テスト回路100は、基板と、基板上に形成された配線部及び被試験デバイス部10とを備える構成とする。テスト回路100では、被試験デバイス本体のパターン形成面内における回転中心位置Oと複数の接続電極13a〜13dのそれぞれとを結ぶ直線L1の延在方向が、配線21の延在方向に対して所定の角度で傾いている。さらに、被試験デバイス本体及び複数の接続電極13a〜13dをパターン形成面内で90度回転させた際にも、複数の接続電極13a〜13d及び複数の配線21〜24間の接続が維持されるような位置に複数の接続電極13a〜13dが配置される。

(もっと読む)

電子部品、電子部品の製造方法、基板

【課題】チッピング検出用配線が他の部材で覆われている状態であっても、ダイシングによって電子部品を形成した後に、チッピング検出用配線の導通状態を検出するための電圧を印加できる基板を提供する。

【解決手段】電子部品40は、互いに平行を成す一方の主面41aと他方の主面41bが矩形状の基体41を有する。基体41の一方の主面41aには、第一チッピング検出用配線42が配されている。また、基体41の他方の主面41bには、第二チッピング検出用配線44が配されている。第一チッピング検出用配線42は貫通配線43aを介して第二チッピング検出用配線44に電気的に接続される。

(もっと読む)

半導体装置の製造方法、半導体装置の製造装置および半導体装置

【課題】配線溝へのめっきの埋め込み性を安定させることができる半導体装置の製造方法等を提供すること。

【解決手段】実施形態によれば、半導体装置の製造方法が提供される。半導体装置の製造方法は、めっき処理によって金属膜を埋め込んで検査パターン10を形成する形成工程と、検査パターン10の特性を検出する検出工程と、検出工程によって検出された検査パターン10の特性に基づいて、前記めっき処理の条件を調整する調整工程とを含む。前記形成工程は、3層以上の配線層11〜13に亘って形成され、かつ中間層にスタックドビア22を有するパターンを、前記検査パターン10として形成する。

(もっと読む)

試験装置

【課題】プローブ検査においても、理想の電源環境を提供する。

【解決手段】試験装置は、ウエハ上に形成されたDUT1を試験する。電源補償回路20は、制御信号SCNT1、SCNT2に応じて制御されるソーススイッチSW1、シンクスイッチSW2を含み、それぞれがオンした状態において補償パルス電流ISRC、ISINKを生成し、補償パルス電流ISRCをメイン電源とは別経路からDUT1の電源端子P1に注入し、またはメイン電源からDUT1へ流れる電源電流から、補償パルス電流ISINKをDUT1とは別経路に引きこむ。電源補償回路20のうち、ソーススイッチSW1、シンクスイッチSW2を含む一部は、ウエハW上に形成される。ウエハには、ウエハ上に形成される電源補償回路20の一部に信号を印加するためのパッドP5〜P7が設けられる。

(もっと読む)

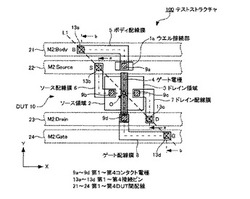

リーク電流モニタ、リーク電流モニタ方法、及び、半導体装置の製造方法

【課題】 リーク電流モニタ、リーク電流モニタ方法、及び、半導体装置の製造方法に関し、複数種類のデバイス特性をできるかぎり同じ構造のモニタで評価する。

【解決手段】 形状或いはしきい値電圧の少なくとも一方が異なる複数種類のトランジスタを異なった領域に同じ間隔で配置するとともに、前記複数種類のトランジスタの内、設計データにおける設置頻度の比を反映した数のトランジスタのゲート電極同士、ソース電極同士、及び、ドレイン電極同士を電気的に共通に接続する。

(もっと読む)

半導体チップの検査方法

【課題】半導体チップの側部に生じた欠損やクラックによるシールリングのダメージを検出して、半導体チップの信頼性向上を図ることが可能な検査方法を提供する。

【解決手段】半導体基板上に、能動素子及び電極パッドを形成した能動領域Aと、これを囲むシールリング5を含む環状の周辺領域Cとを形成して構成され、さらに周辺領域Cのうちシールリング5の外側に、能動領域Aを囲むと共に両端が隣り合って位置する線状を呈して一端7aが半導体基板に接地された検査用配線7、及び、この他端に接続された検査用パッド9を形成した半導体チップ1に対し、キャピラリにより電極パッド3とパッケージ11の接続端子面13とをボンディングワイヤ15により電気接続する工程において、キャピラリの先端部から引き出されたボンディングワイヤ15を検査用パッド9に押し当てることで、キャピラリにより検査用配線7の電気的な導通状態を検出する。

(もっと読む)

半導体装置

【課題】シールリングを加工することなく、半導体装置周辺部の異常を検出可能な半導体装置を提供する。

【解決手段】多層配線層が形成された半導体基板2上に、複数の電極端子5,6,7,8,9を設けるとともに、半導体基板2の外周部に設けられたシールリング3,4と、電極端子5,6,7,8,9とを電気的に接続する不純物注入領域(ドープ領域)2a,2b,2cを半導体基板2に形成することで、電極端子5,6,7,8,9間の抵抗などを測定することにより、半導体装置1周辺部の異常が検出可能になる。

(もっと読む)

半導体集積回路ウエハ、半導体集積回路チップ及び半導体集積回路ウエハのテスト方法

【課題】ボンディングパッドに傷跡を残さず、かつボンディングの不良の削減や接続の信頼性を向上することが可能な半導体集積回路ウエハを提供する。

【解決手段】半導体集積回路領域2aと、スクライブ領域3と、前記スクライブ領域内に備えられたBIST回路4と、半導体集積回路2とBIST回路4とを接続する接続配線9と、BIST切替信号入力パッド7と、BIST切替信号入力パッド7からの駆動信号により駆動されるBIST切替回路8とを備え、BIST切替回路8は、半導体集積回路用の入出力パッド6と、入出力パッド6と半導体集積回路2とを接続する回路配線11と、回路配線11の途中に設けられて、BIST切替信号入力パッド7からの駆動信号によって駆動するスイッチ素子10とを具備してなる半導体集積回路ウエハを採用する。

(もっと読む)

不具合検出機能を備えた半導体装置

【課題】層間絶縁膜の剥離を検出する半導体装置を提供する。

【解決手段】半導体チップ2の外周に沿って層間絶縁膜の剥離を検出するための信号を伝送する検査配線3が形成されている。検査配線3に検出信号を供給するための検出回路4と、検査配線3を流れた検出信号を出力するための出力端子5と、半導体チップ2に設けられた内部回路6と、内部回路6からの出力信号と、検査配線3を流れた検出信号とのいずれか一方を選択して出力端子5に供給する出力切替回路7を備える。検査配線3は適当な間隔毎に切断され、層間配線10を通して最上層配線8に載せ替えて接続されている。以上の構成により、測定端子数を増やすことなく層間絶縁膜の剥離を容易に検出することが可能となり、さらに層間絶縁膜の接着を補強することができる。

(もっと読む)

半導体装置の製造方法と半導体装置

【課題】半導体装置の面積を増大させることなく、測定用の構造を確保し、かつ製造した半導体装置の容量値を直接測定できる、半導体装置の製造方法と半導体装置の構造を提供する。

【解決手段】回路素子が形成された内部回路領域を囲う周辺部に、複数の配線層のそれぞれにリング状の配線が、層間絶縁膜を介して互いに対向して設けられた半導体装置の製造方法において、複数の配線層の内の、上下に隣り合う2層の配線層に設けられたリング状配線を、互いに絶縁された状態に形成し、この2層のリング状配線間の容量を測定し、その後、前記2層のリング状配線の内の少なくとも一方を、前記内部回路に接続することを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置

【課題】半導体チップに発生するクラックを検知することができ、さらに設計の自由度が向上するとともに配線のレイアウトの自由度やLSIのレイアウト効率およびパッケージ基板のレイアウト効率が向上した半導体装置を提供する。

【解決手段】本発明の半導体装置は、多層配線構造を有する半導体チップ10と、半導体チップ10上面において、半導体チップ10の外周縁に沿って形成された複数の電極パッド12と、複数の電極パッド12から選択された2つの第1電極パッド12aおよび第2電極パッド12bに接続するとともに、平面視において、半導体チップ10の全外周縁に沿って設けられた配線18とを備え、配線18は異なる層に形成された第1配線部14と第2配線部16とを含み、第1配線部14と第2配線部16とは接続プラグを介して直列に接続されている。

(もっと読む)

半導体装置の検査方法および接触抵抗測定回路

【課題】半導体集積回路の検査工程において、測定時のプローブピンの接触抵抗の上昇による測定異常を容易にかつ短時間で測定する。

【解決手段】接触抵抗測定回路を用いてプローブピン19,20の針先に定電圧を印加して流れる電流あるいは電圧の値を測定し、この電流値と電圧値とから該針先の接触抵抗値を算出し、この接触抵抗測定回路により測定された抵抗値が所定値より高い場合にプローブピンの針先を研磨する。接触抵抗測定回路は、半導体ウエハの一部あるいは、テスタ内部に、プローブピンの針先位置やプローブピンの数に依存せず測定できる形状の針当て専用領域11〜14を有する。これにより、正確にかつ短時間で接触抵抗を測定できる。

(もっと読む)

半導体試験システム、半導体試験装置、被試験ウェハおよび半導体試験方法

【課題】 被試験ウェハ直前のプローブ針までの全ての系を自己診断する。

【解決手段】 本発明の半導体試験システム100は、被試験ウェハ300と、被試験ウェハと電気的に接続される半導体試験装置200とを用いて、被試験ウェハの電気的試験を行い、被試験ウェハには、複数の半導体回路350と、複数の半導体回路の外縁に配され、半導体回路と等しい電極を有する自己診断回路400と、が印刷され、半導体試験装置は、被試験ウェハに圧接するプローブカード240と、プローブカードに接続され、半導体試験装置とウェハとの電気信号を中継するパフォーマンスボード230と、を備え、プローブカードが半導体回路に接続されているときは半導体回路の試験を行い、プローブカードが自己診断回路に接続されているときは半導体試験装置の自己診断を行う。

(もっと読む)

集積回路の試験方法

【課題】 本発明は集積回路の試験方法を提供する。

【解決手段】 集積回路中の故障の発生又は可能性を評価するプロセスである。プロセスは基板又はダイスの周囲にランナのような導電性領域を形成することを含む。導電性領域は集積回路中の1ないし複数の異なるメタライゼーション層に配置される。導電性領域は1ないし複数のボンディングパッドに結合される。ダイスは抵抗、導電率、漏話又は導電性領域上の他の電気的特性を、ボンディングパッドを通して測定することにより、評価される。評価は集積回路中に形成されたランナが故障しているか、故障する可能性があるかを予測するために使用できる。

(もっと読む)

半導体集積回路及びそのテストシステム

【課題】 物理コンタクトを廃した非接触テストを可能とする半導体集積回路及びそのテストシステムを実現することを目的とする。

【解決手段】 内部回路により動作する半導体集積回路において、前記内部回路に対して試験を行なう試験部と、この試験部と電気的に接続し、無線通信を行なう無線インターフェースモジュールとを設けた半導体集積回路、

及びこの半導体集積回路の無線インターフェースモジュールと無線で通信を行なう無線部を備えるテストシステム。

(もっと読む)

半導体ウエハ、および強誘電体メモリ装置の試験方法

【課題】 製造コストが低減された半導体ウエハ、ならびに製造コストを低減することができる強誘電体メモリ装置の試験方法を提供する。

【解決手段】 本発明の半導体ウエハ200は、強誘電体メモリ装置100を含む複数の半導体チップ領域220と、試験用チップ領域210と、複数の半導体チップ領域220と試験用チップ領域210とを接続する配線230,240と、を含む。

(もっと読む)

半導体ウェーハ、その加熱制御方法、およびバーンイン装置

【課題】 ウェーハレベルでのバーンイン測定時のウェーハ面内の温度バラツキを無くし、安定した温度制御を行えるようにする。

【解決手段】 半導体ウェーハ1の構造を、複数の半導体デバイス2をスクライブレーン3を介して互いに分離して形成し、各半導体デバイス2を加熱する発熱素子4を各半導体デバイス2内とスクライブレーン3内の少なくとも一方に設けたものとする。これにより、バーンイン測定時に発熱素子4によって半導体デバイス2の加熱制御を行うことができ、ウェーハ面内で均一な温度が可能となる。

(もっと読む)

1 - 17 / 17

[ Back to top ]