Fターム[4M106AD08]の内容

半導体等の試験・測定 (39,904) | パッド(電極) (883) | 材質 (28)

Fターム[4M106AD08]に分類される特許

1 - 20 / 28

炭化珪素半導体装置の製造方法及びその検査方法、並びに、炭化珪素半導体ウェハの製造方法及びその検査方法

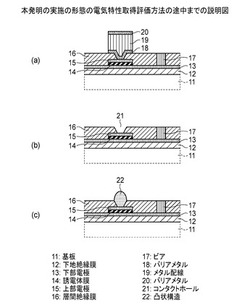

電気特性取得評価方法

【課題】電気特性取得評価方法に関し、試料側にもプローブ側にも問題を発生させることなく安定な電気特性取得評価を行う。

【解決手段】積層体の表面側電極に対するコンタクトホール21を露出する工程と、前記露出したコンタクトホール21に導電性物質を埋め込んで凸状構造22を形成する工程と、前記凸状構造22を含む領域にカンチレバーを間欠接触測定方式で接触させて前記凸状構造22の位置を認識する工程と、前記凸状構造22の中心軸の方向に前記カンチレバーを押しつけて電気特性を取得する工程とを設ける。

(もっと読む)

半導体装置、及び、半導体装置の製造方法

【課題】 プローバーテストの製品への影響をさらに軽減して、より一層信頼性の高い半導体装置を提供する。

【解決手段】 半導体装置100を、半導体基板10aと、半導体基板10aの一方の面上に形成された絶縁膜10bと、縦孔配線部30と、金属膜11と、導電性保護膜12とを備える構成とする。金属膜11は、絶縁膜10b内に形成され、縦孔配線部30と電気的に接続される。そして、導電性保護膜12は、絶縁膜10b内において金属膜11に接して形成され、かつ、金属膜11の膜面において製造途中で行うプローバーテスト時のプローブの接触領域を含む領域に形成される。

(もっと読む)

半導体装置

【課題】LSIチップの製造コストを低減することが可能な半導体装置を提供する。

【解決手段】半導体装置は、半導体基板と、前記半導体基板に形成され、第1の電源配線を含む第1の電源配線層を備える複数のLSI領域と、前記半導体基板に形成された第1の電源端子と、前記LSI領域の間のダイシングライン領域に、前記LSI領域と前記ダイシングライン領域とを区画するダイシングラインに沿って形成され、前記第1の電源配線と前記第1の電源端子とを電気的に接続する第2の電源配線を含む第2の電源配線層と、を備える。少なくとも前記LSI領域において、前記第1の電源配線と前記第2の電源配線との境界にバリアメタル膜が形成されている。

(もっと読む)

半導体装置、及び積層型半導体装置

【課題】本発明は、積み重ねられた半導体装置間の電気的接続信頼性を向上可能な半導体装置及び積層型半導体装置を提供することを課題とする。

【解決手段】表面58a及び裏面58bを有する半導体チップ38を貫通する第1の貫通電極48と、半導体チップ38の表面側に位置する第1の貫通電極48の一端に接続される第1の表面電極53と、半導体チップ38の裏面側に位置する第1の貫通電極48の一端に接続される第1の裏面電極55と、半導体チップ38を貫通する第2の貫通電極49と、半導体チップ38の裏面側に位置する第2の貫通電極49の一端に接続される第2の裏面電極56と、を備え、半導体チップ38の表面側に位置する第2の貫通電極49の一端には電極を設けない。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体装置の検査特性を向上させる。

【解決手段】本発明の半導体装置の製造方法は、(a)基板の上方にアルミニウムを含有する導電性膜(アルミニウム膜10b)を形成する工程と、(b)上記導電性膜をパターニングすることにより配線を形成する工程と、(c)上記配線の上部に第1絶縁膜(第1保護膜)を形成する工程と、を有する。さらに、(d)上記第1絶縁膜をエッチングすることにより、上記配線のパッド領域(Pd)を露出する工程と(e)上記パッド領域(Pd)に、窒素系のプラズマガスを用いたプラズマ処理を行う工程と、(f)上記(e)工程の後、上記パッド領域(Pd)にプローブ針を当接し、上記パッド領域(Pd)に通電する工程と、を有する。上記(e)工程により、上記パッド領域(Pd)に窒化アルミニウム層(15)が形成され、パッド領域(Pd)とプローブ針(N)との接触抵抗を低減することができる。

(もっと読む)

半導体装置およびその製造方法ならびに半導体ウエハ

【課題】ダイシングブレードの寿命を延ばすことができるとともに、半導体装置のエッジ部へのダメージを低減できる半導体装置を提供する。

【解決手段】機能素子領域2においては、第3層間絶縁膜27表面とパッシベーション膜33との間には、下配線25に接続される上配線29およびキャップメタル層32が形成されている。下配線25はCu以外の配線材料からなり、上配線29はCuからなる。このキャップメタル層32におけるパッシベーション膜33のパッド開口34から露出した部分が第1パッド6である。一方、スクライブ領域3においては、第3層間絶縁膜27表面とパッシベーション膜33との間には、下配線25に接続されるキャップメタル層32が形成されている。このキャップメタル層32におけるパッシベーション膜33のパッド開口44から露出した部分が第2パッド10である。

(もっと読む)

半導体基板および半導体基板の製造方法

【課題】ボンディングワイヤが接続されたボンディングパッドを一面に有する半導体基板において、ワイヤの接続によるボンディングパッド下部のクラックの発生を適切に検出できるようにする。

【解決手段】半導体基板1の内部にてボンディングパッド10の下部には、当該半導体基板1の特性を検査するための検査用配線40が設けられており、検査用配線40は、ボンディングパッド10のうちボンディングワイヤ70の端部が位置する部位の直下に配置されている。

(もっと読む)

半導体装置および半導体装置の検査方法

【課題】検査に用いるプローブの耐久性を向上できる半導体装置を提供する。

【解決手段】ウエハーのスクライブ線150上に配置された第1チェック素子1を具備する。第1チェック素子1は、第1配線絶縁膜5と、第1配線絶縁膜5の第1開口部に配置された第1チェック素子パッド10とを備える。第1チェック素子パッド10は、導電性の第1パッドメタル部12と、矩形の平面形状を有する絶縁性の第1ダミー部13とを含む。第1ダミー部13の平面形状は、スクライブ線150の長手方向と垂直な2つの第1長辺と、第1チェック素子パッド10の外周部近傍に配置される2つの第1短辺とを含む。

(もっと読む)

DLTS測定用電極及びその製造方法

【課題】測定時において疑似ピークが現れないDLTS測定用電極を提供する。

【解決手段】シリコン基板上に設けられたアンチモンからなるショットキー電極12aと、シリコン基板10の表面10aとショットキー電極12aとの間に設けられたチタンからなる密着膜12bとを備える。本発明によれば、ショットキー電極の材料としてアンチモンを用いていることから、DLTS測定において疑似ピークがほとんど現れず、しかも、測定時におけるリーク電流を抑制することが可能となる。このため、シリコンウェーハに含まれている重金属の種類や濃度を正確且つ高感度に評価することが可能となる。

(もっと読む)

ボンドパッドを有する半導体装置およびそのための方法

【課題】ワイヤボンド接続の信頼性を低下させることなくダイをプローブ検査でき、小さいボンドパッドおよびボンドパッド間の微細なピッチ間隔でダイについての確実なプローブ検査が行える技術の提供。

【解決手段】ボンドパッド36が、実質的に重なりのないプローブ37領域およびワイヤボンド38領域を有する。ボンドパッド36は最終金属層パッド16に接続されている。ボンドパッド36はアルミニウム製であり、最終金属層パッド16は銅製である。プローブ37領域をワイヤボンド38領域から分離することで、最終金属層パッド16がプローブ検査によって損傷を受けることが防止され、より信頼性の高いワイヤボンドが可能となる。

(もっと読む)

信号送受信方法、半導体装置の製造方法、半導体装置、およびテスタ装置

【課題】インダクタを配置するための必要面積を小さく保ちつつ、電磁誘導で信号の送受信を良好に行う。

【解決手段】一面にインダクタ114が形成された半導体装置100に、半導体装置100のインダクタ114に対応する位置に設けられた外部インダクタ204を含む外部装置(200)から信号の送受信を行う。この手順は、少なくとも半導体装置100のインダクタ114と外部装置200の外部インダクタ204との間に強磁性体の微粒子を含む強磁性体膜130を配置し、強磁性体膜130を介してインダクタ114と外部インダクタ204とを対向配置させる工程と、インダクタ114と外部インダクタ204とを対向配置させた状態で、インダクタ114と外部インダクタ204との間で電磁誘導で信号の送受信を行う工程と、を含む。

(もっと読む)

半導体装置

【課題】手間を要さずに回路部のテストを行うことができ、スクライブ領域の有効活用を図ることができ、半導体チップを安定的に製造することができ、非接触で外部との通信を行うことができる半導体装置を提供する。

【解決手段】半導体装置1は、半導体チップ形成領域14Bと、半導体チップ形成領域14B間に位置するスクライブ領域14Aとが形成された半導体ウェハ11と、半導体ウェハ11上に設けられた複数の半導体チップの回路部12と、各半導体チップ形成領域14B内に設けられ、各回路部12に電気的に接続される複数の第一の導電層13と、第一の導電層13同士をスクライブ領域14Aの一部をまたいで電気的に接続する第一の接続部15とを有する。第一の導電層13および第一の接続部15のいずれか一方に、外部電源供給用あるいは接地用のパッド16が接続される。半導体装置1は、回路部12に接続され、容量結合あるいは誘導結合により外部との通信を行う通信部Tを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】パッド電極の直下でのクラックの発生を抑制できるようにした半導体装置及びその製造方法を提供する。

【解決手段】シリコン基板1と、シリコン基板1上に形成されたLOCOS膜3と、LOCOS膜3上に形成されたポリシリコン膜5と、LOCOS膜3上に形成されたILD膜7と、ILD膜7に形成され、ポリシリコン膜5を底面とする第1の開口部と、第1の開口部内に形成され、ポリシリコン膜5と接するパッド電極9と、を有する。ポリシリコン膜5は、ILD膜7よりも強度があり、衝撃に対する耐性が高いため、プローブ検査の際にクラックの発生を抑制することができる。

(もっと読む)

プローブ検査方法

【課題】探針を有するプローブカードを用いてプローブ検査を行う際に、テストパッドの表面にプローブ痕が残ってしまうことを防止できる技術を提供する。

【解決手段】パッド32上の開口部は、チップ31の表面に開口する開口部33と、開口部33の底部で開口し、パッド32に達する開口部34とからなり、開口部33は、開口部34に比べて大きな平面サイズとする。このような開口部33、34にのみ所定量の導電性流体36を充填した状況下で、プローブ針15の先端をその導電性流体36と接触させて、プローブ針15をパッド32に接触させずに、パッド32とプローブ針15との電気的導通を取ることでプローブ検査を実施する。

(もっと読む)

半導体装置

【課題】多層の金属配線層を有する半導体装置において、より一層のパッド配置面積の低減を図る。

【解決手段】アルミ3と、アルミ3との間に層間絶縁膜を介して設けられたアルミ2と、アルミ2,3間を接続するコンタクトと、アルミ3に対応して設けられた保護膜の開口部1と、を備え、開口部1の内側領域が、外部電極用パッドであり、かつ、ボンディング領域とプローブテスト領域の二つに分けて使用される半導体装置である。前記ボンディング領域では、アルミ3が露出され、該アルミ3によりアルミ2が隠れている。前記プローブテスト領域では、アルミ2が露出されている。

(もっと読む)

半導体装置とその検査方法と異方性導電フィルム

【課題】 パッド電極を被覆している絶縁層を削り取ることなくかつ低荷重でプローブによる特性検査を行うことができる半導体装置とその検査方法と異方性導電フィルムを提供する。

【解決手段】 半導体装置100はパッド電極2の表面に異方性導電層16が形成されている。異方性導電層16はパッド電極2に接している下層14とその下層14に接している上層12を備えている。下層14は導電性であるとともにパッド電極2側の端部が鋭角である第1フィラー群6を含んでおり、上層12は導電性であるとともに下層14側の端部が第1フィラー群6よりも鈍角である第2フィラー群10を含んでいる。第1フィラー群6はパッド電極2の表面を被覆している絶縁層4よりも硬い材料で形成されている。プローブ18を押圧すると第1フィラー群6が絶縁層4を突き破って貫通し、プローブ18とパッド電極2が導通する。

(もっと読む)

電極および電極の形成方法

【課題】半導体シリコンウェーハの電気的特性を評価するにあたり、電気的特性の評価の精度を従来に比べ向上させることが可能なシリコンウェーハ上にショットキー接合された電極とその電極の形成方法を提供する。

【解決手段】半導体シリコンウェーハ上にショットキー接合された電極であって、半導体シリコンウェーハ上に酸化膜を介することなくアルミナ(Al2O3)と金属アルミニウムを真空蒸着したものであることを特徴とする電極とその形成方法である。

(もっと読む)

エピタキシャル層のドーパント濃度測定方法およびこれを用いたエピタキシャル層の抵抗率測定方法

【課題】エピタキシャル層、特には低抵抗のエピタキシャル層の抵抗率測定にあたって、ドーパント濃度を高精度に測定することが可能であり、繰り返し精度も高いドーパント濃度や抵抗率の測定方法を提供する。

【解決手段】シリコン基板上に形成され、該シリコン基板と同じ導電型を有するエピタキシャル層のドーパント濃度をC−V法により測定するエピタキシャル層のドーパント濃度測定方法であって、少なくとも、前記エピタキシャル層上に直径1.5mm以下の電極を形成し、該電極を用いてC−V特性を求めてドーパント濃度を測定するエピタキシャル層のドーパント濃度測定方法。

(もっと読む)

半導体装置、半導体ウエハ構造、及び半導体装置の製造方法

【課題】パッシベーション膜の損傷を防ぎつつ、導電性パッドに導電性の針を当接させて行われる電気的な試験を正確に行うことが可能な半導体装置、半導体ウエハ構造、及び半導体装置の製造方法を提供すること。

【解決手段】シリコン基板10と、シリコン基板10の上方に形成された層間絶縁膜40と、層間絶縁膜40の上に形成され、主導電膜43bと、該主導電膜43bよりも硬い表面導電膜43dとを順に形成してなる導電性パッド43pと、層間絶縁膜40の上に形成され、導電性パッド43pが露出する窓51aを備えたパッシベーション膜51とを有し、導電性パッド43pの上面に、表面導電膜43dよりなる凸パターンPが形成された半導体装置による。

(もっと読む)

1 - 20 / 28

[ Back to top ]