Fターム[4M106CA15]の内容

半導体等の試験・測定 (39,904) | 検査内容 (5,684) | 接続状態 (169)

Fターム[4M106CA15]の下位に属するFターム

断線、短絡 (142)

Fターム[4M106CA15]に分類される特許

1 - 20 / 27

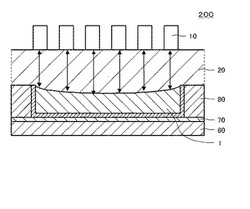

半導体装置および半導体装置の製造方法

【課題】溝配線に生じるディッシングやエロージョンが配線構造に及ぼす影響を簡便に評価できるような半導体装置を提供する。

【解決手段】TEG200は、多層配線層中に設けられている。また、多層配線層中の第1絶縁膜に埋め込まれた下層溝配線1を備えている。TEG200は、第1絶縁膜80(図示せず)の表層に埋め込まれた下層導体パターン1と、第1絶縁膜80上及び下層導体パターン1上に形成された第2絶縁膜20と、それぞれが同一の下層導体パターン1に対向する複数の上層導体パターン10と、を有している。なお、上層導体パターン10は、第2絶縁膜20の表層に埋め込まれていても良いし、第2絶縁膜20上に形成されていても良い。

(もっと読む)

ウェーハ接合強度検査装置及び方法

【課題】接合ウェーハを破壊することなく、接合界面に間隙が生じていない場合であっても、局所的な接合部の接合強度を検査することができる検査装置を提供する。

【解決手段】ウェーハ接合強度検査装置100は、接合ウェーハ200を保持する試料ステージ160と、テラヘルツ波を発生するテラヘルツ波発生器151と、接合ウェーハ200を透過又は反射したテラヘルツ波を検出するテラヘルツ波検出器157と、テラヘルツ波検出器157によって検出したテラヘルツ波より接合ウェーハ200のTHz波特性を演算する演算部と、を有する。演算部は、予め求めた基準試料のTHz波特性と接合強度の間の関係から、検査対象の接合ウェーハのTHz波特性に対応する接合強度を演算する。

(もっと読む)

配線検査方法

【課題】配線の微細化が進むと、実際の配線幅に比較して画像中の配線の幅方向のピクセル数が不十分になり、検査精度を向上させるために、撮影倍率を向上させると、処理能力が落ちて、生産性が落ちてしまうという課題を解消できる技術を提供する。

【解決手段】表面に配線が形成された検査対象物の表面を電子カメラで撮像し、その撮像した画像に含まれる配線パターンを検出し、検出した配線パターンのうち画素の配列に対して傾斜した配線像を抽出し、その抽出した配線像の欠陥の有無を判定する。

(もっと読む)

配線構造、半導体装置及び不良箇所特定方法

【課題】不良箇所の特定の容易化を実現し得る配線構造、半導体装置及び不良箇所特定方法を提供することにある。

【解決手段】基板10上に形成された第1の配線14と、第1の配線上に形成され、第1の領域において第1の配線と重なり合う第2の配線20とを有し、第1の配線は、第1の領域外に突出する第1のタブ部16を有している。

(もっと読む)

故障解析装置

【課題】故障箇所特定の精度を低下させずに観測時間の短縮ができる故障解析装置を実現する。

【解決手段】本発明の故障解析装置は、被解析LSI33のチップ表面にレーザ光を照射して、被解析LSI33の故障箇所を特定する故障解析装置であって、分割制御情報18に基づいて、被解析LSI33へのレーザ光の照射領域を任意の複数の矩形領域であるブロックに分割してブロック情報19を生成するブロック分割制御部14と、ブロック情報19とあらかじめ抽出された被解析LSI33の故障ノード情報20とに基づいて、複数のブロックの優先順位を決定してレーザ照射情報21を生成する優先順位設定制御部15と、レーザ照射情報21に基づいて、被解析LSI33へのレーザ光の照射を制御するレーザ制御部17を有する。

(もっと読む)

電子部品の検査方法及び検査装置

【課題】高抵抗性のオープン抵抗の特定を可能とする電子部品の検査方法および検査装置を提供する。

【解決手段】電子部品の検査装置であって、当該検査装置は、電子部品における故障発生が疑われる配線に接続するための電流検出端子106と、電流検出端子106に接続されており、配線に生じた電流を検出する電流検出器105と、電流検出端子106と電流検出器105との間に設けられ、電流を通過させるか否かをゲートの開閉により切り替えるゲーティング装置112と、電子ビームを生成する電子銃101と、電子ビームをパルス化するパルスビーム発生装置111と、パルス化された電子ビームを配線に照射した際に生じた電流を電流検出器105により検出する際に、ゲーティング装置112のゲートの開閉を調整するゲーティング調整装置113とを備える。

(もっと読む)

半導体装置、電子部品、半導体装置の製造方法

【課題】貫通電極の電気特性を効率よく検査する。

【解決手段】本発明の半導体装置2の製造方法は、シリコン基板20に半導体素子を含んだ電気回路を形成する工程と、シリコン基板20を貫通して設けられ、電気回路と電気的に接続される第1貫通電極22を形成する工程と、シリコン基板20を貫通して設けられ、シリコン基板20の表面20aで第1貫通電極22と短絡する第2貫通電極23を形成する工程と、シリコン基板20の裏面20bにおいて、第1貫通電極22と第2貫通電極23との間の電気特性を検査する工程と、を有する。

(もっと読む)

デバイス搭載ウェーハ、デバイスチップ、デバイスチップの製造方法

【課題】張り合わせウェーハであっても、その上に形成された各デバイスをオンウェーハ状態で確実に通電検査を行うことができるデバイス搭載ウェーハの提供、オンウェーハ状態での通電検査を確実に行うことができるデバイスチップ及びデバイスチップの製造方法の提供を課題とする。

【解決手段】支持基板用ウェーハ11に張り合わせ界面14を介して半導体層12を張り合わせた張り合わせウェーハを用い、スクライブライン10aで区分された複数のチップ領域10bにそれぞれ半導体デバイス13を構成してなるデバイス搭載ウェーハ10であって、前記スクライブライン10aに沿って前記張り合わせ界面14を越える深さの電気的隔離溝15を形成することで、前記各半導体デバイス13を電気的に分離独立させた状態に構成してある。

(もっと読む)

半導体装置、半導体装置の検査方法、半導体装置マザー基板、及び半導体装置の製造方法、並びに電子機器

【課題】半導体装置の機能検査と貫通電極の機能検査とを実施するための検査時間を抑制すると共に、基板の両面から貫通電極に接触することが必要であることに起因して高度な検査技術が必要である貫通電極の検査を容易にすることができる、半導体装置、半導体装置の検査方法、半導体装置マザー基板、及び半導体装置の製造方法、並びに電子機器を提供する。

【解決手段】半導体装置の製造方法は、回路形成面と裏面とを有する半導体基板の、回路形成面に回路素子及び回路配線を形成する工程と、回路形成面と裏面とを電気的に接続する貫通電極を形成する工程と、第二貫通電極を貫通電極に対応して形成する工程と、裏面に配設されており、貫通電極と第二貫通電極とを接続する接続裏面配線を形成する工程と、少なくとも第二貫通電極に、回路形成面側から検査プローブを接触させることによって、回路素子及び回路配線の機能を検査する機能検査工程と、を有する。

(もっと読む)

半導体装置および該半導体装置の検査方法

【課題】入力端子または出力端子の再配線による抵抗値の異常を簡単な構成で短時間に検査することができる半導体装置とその検査方法を提供する。

【解決手段】半導体チップ10上の入力パッドまたは出力パッドP2と電源パッドP1間(入力パッドまたは出力パッドP2と接地パッドP3間でもよい)に接続された保護用MOSトランジスタM1を有し、半導体装置20の外部端子T4から入力されるテスト信号を保護用MOSトランジスタM1のゲートに印加することにより、入力パッドまたは出力パッドP2を電源パッドP1に接続するかを制御する。また、半導体装置20は半導体チップ10のパッドP1〜P4と半導体装置の外部端子T1〜T4間を接続する再配線手段を備える。半導体装置20はCSPまたはWLCSPで製造されたものである。

(もっと読む)

半導体検査装置

【課題】ウェハ等の基板に欠陥などを生じさせることなく、ウェハを帯電させることのできる半導体検査装置を提供する。

【解決手段】電子ビームを用いた吸収電流測定方法を用いて、ウェハ23のコンタクトホール界面状況や薄膜を評価する半導体検査装置において、ウェハ23外から前記電子ビームを照射し、この照射によってウェハ23または薄膜周辺に電子を間接的に照射させ、この後に、前記電子ビームをウェハ23または薄膜等の測定点に照射して前記測定を行う。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体基板に設けられる貫通孔および貫通電極の形成状態および出来映えを容易に確認可能にし、貫通孔および貫通電極の品質向上と、接続不良の早期発見を可能にする技術を提供する。

【解決手段】半導体基板11と、半導体基板11の表面に設けられた内部電極12Aおよび内部電極12Bと、半導体基板11を厚み方向に貫通して内部電極12Aに到達し、内部電極12Aと電気的に接続された第一の貫通電極17Aと、半導体基板11および内部電極12Bを厚み方向に貫通する第二の貫通電極17Bと、半導体基板11の裏面に設けられ、第一の貫通電極17Aと電気的に接続された金属配線18とを備える。

(もっと読む)

半導体検査装置及び検査方法

【課題】 半導体デバイスに対して無バイアス状態での検査を好適に行うことが可能な半導体検査装置及び検査方法を提供する。

【解決手段】 半導体デバイスSに対し、パルスレーザ光の照射によって発生する電磁波を利用して無バイアス状態で検査を行うとともに、半導体デバイスSのレイアウト情報を参照して検査範囲を設定し、その範囲内でパルスレーザ光の検査光L1による2次元走査を行う。また、半導体デバイスSの検査範囲を光学系の光軸に対して所定位置に配置し、半導体デバイスSに対して固浸レンズ36を設置した状態で、走査手段であるガルバノメータスキャナ30により、固浸レンズ36を介して半導体デバイスSの検査範囲内を検査光L1によって2次元走査するとともに、半導体デバイスSから出射された電磁波を光伝導素子40で検出する。

(もっと読む)

検査装置

【課題】放電防止の機能を有し、吸収電流の検出をより効率よく行う検査装置を提供する。

【解決手段】吸収電流検出器23を真空試料室26の内部に搭載し、探針19から吸収電流検出器23までの信号配線のもつ静電容量を数pF程度まで低減することにより、数十kHz以上の高周波数吸収電流信号であっても検出が可能となる。また、信号切換制御部15により信号切換部22を動作させ、試料9に接触した探針19と半導体特性解析装置25の信号線を導通させることにより、探針19に繋がる信号経路を吸収電流の伝送に限定することなく、試料9の電気的特性の測定が可能となる。また、探針19や試料ステージ18に帯電のスローリークのための抵抗を設ける。

(もっと読む)

パターン検査装置、パターン検査方法およびプログラム

【課題】精度および効率に優れたパターン検査装置、パターン検査方法およびプログラムを提供する。

【解決手段】上下方向に互いに隣接する複数層にそれぞれ形成されたパターン同士の相対的位置関係に依存するプロセス上の危険度に応じて欠陥検出のための閾値を変える。

(もっと読む)

ビア不良検出構造及びビア不良検出方法

【課題】多層配線の形成後に、熱履歴に起因するビア不良を検出するビア不良検出構造を提供する。

【解決手段】 ビア不良検出構造は、半導体基板上の第1配線、前記第1配線の上方に位置する第2配線、及び前記第1配線と第2配線を電気的に接続する第1ビアを含むビアチェーン(15)と、前記ビアチェーンの一端側に接続される検査領域(C)と、前記ビアチェーンを、前記半導体基板と電気的に接続するコンタクト領域(B)と、を含み、前記検査領域は、前記ビアチェーンの一端側から引き出され、前記第1配線よりも大きなサイズの引き出し配線(22C、23C、24C)が前記ビアチェーンの第2配線よりも上層まで積層された多層引き出し配線と、前記多層引き出し配線を各層間で接続する引き出し配線ビア(32、33)とを含む。

(もっと読む)

配線検査方法、配線検査装置、およびTFTアレイ検査装置

【課題】基板上に形成された配線の欠陥検出を行う手段の提供。

【解決手段】配線検査装置1は、配線が形成された基板100に検査信号を印加する検査信号印加部4と、基板に電子線を照射する電子線照射部2と、基板から放出される二次電子を検出する二次電子検出部3と、二次電子の信号強度によって配線の電位状態を検出し、この電位状態から配線の欠陥を検出する欠陥検出部6とを備える。基板に配線が形成された段階において、この配線に電気信号を印加して所定の電位状態とし、この電位状態の配線に電子線を照射して放出される二次電子を検出し、この二次電子の信号強度に基づいて配線の欠陥検出を行う。欠陥検出は、配線の欠陥の有無、欠陥位置、ショート欠陥かオープン欠陥かの欠陥種の判別が可能である。

(もっと読む)

不具合検出機能を備えた半導体装置

【課題】層間絶縁膜の剥離を検出する半導体装置を提供する。

【解決手段】半導体チップ2の外周に沿って層間絶縁膜の剥離を検出するための信号を伝送する検査配線3が形成されている。検査配線3に検出信号を供給するための検出回路4と、検査配線3を流れた検出信号を出力するための出力端子5と、半導体チップ2に設けられた内部回路6と、内部回路6からの出力信号と、検査配線3を流れた検出信号とのいずれか一方を選択して出力端子5に供給する出力切替回路7を備える。検査配線3は適当な間隔毎に切断され、層間配線10を通して最上層配線8に載せ替えて接続されている。以上の構成により、測定端子数を増やすことなく層間絶縁膜の剥離を容易に検出することが可能となり、さらに層間絶縁膜の接着を補強することができる。

(もっと読む)

試験回路、半導体ウエハ装置、及び試験方法

【課題】コンタクト不良の発生場所を特定することができる試験回路、半導体ウエハ装置、及び試験方法を提供すること。

【解決手段】直列に接続された複数のコンタクト抵抗Rを含むコンタクトチェーン50と、隣り合うコンタクト抵抗Rの接続点Pに、ソース領域17aが電気的に接続されたトランジスタTRと、ドレイン領域17bに一端が電気的に接続されたヒューズ22とを有する試験回路による。

(もっと読む)

回路パターンの欠陥検査装置および欠陥検査方法

【課題】回路パターンの欠陥検査方法では、処理速度を高めるため、お手本となる基準パターンと被検査物は単純な比較による差異で良不良を判断していた。また、回路パターンは製品の動作に直接関係するため、できるだけ細かな差異を欠陥として判定させていた。しかし、細かな差異は過検出となり、別途目視での再検査が必要となる。

【解決手段】単純な比較による検査で不良と判定された被検査物の欠陥部分の画像を、欠陥の種類毎の分析によって、そもそも欠陥であるか否かと、欠陥であったとしても容認できるか否かを判定する。

(もっと読む)

1 - 20 / 27

[ Back to top ]