Fターム[4M118EA20]の内容

Fターム[4M118EA20]に分類される特許

1 - 20 / 146

固体撮像素子の製造方法、固体撮像素子、および電子情報機器

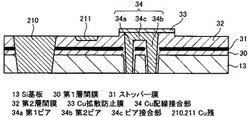

半導体装置の製造方法、及び、半導体装置

【課題】 より一層、製品の歩留まりを向上させることのできる半導体装置の製造方法を提供する。

【解決手段】 本開示の半導体装置の製造方法では、まず、第1半導体部及び第2半導体部を貼り合わせた半導体部材の一方の面上に形成された絶縁膜30上に、所定の薬液で処理された際に該所定の薬液が絶縁膜に浸透しないような耐性を有するストッパー膜31を形成する。次いで、半導体部材のストッパー膜31側に、第1半導体部及び第2半導体部を電気的に接続するためのCu配線接合部34を形成する。次いで、Cu配線接合部34上にCu拡散防止膜34を形成する。次いで、Cu配線接合部34の形成領域以外の領域のCu拡散防止膜33を除去して該領域に存在する不要なCu部210,211を露出させる。そして、所定の薬液を用いて、不要なCu部210,211を除去する。

(もっと読む)

撮像装置の製造方法

【課題】固体撮像素子に付着したゴミを容易かつ確実に除去する。

【解決手段】少なくとも固体撮像素子の上面に粘着性シート形成用溶液を塗布する塗布工程1と、塗布工程1にて形成された粘着性シートに対して引き剥がす方向の力を加えて、粘着性シートを剥離する剥離工程とを備える。

(もっと読む)

プラズマ処理方法、プラズマ処理装置、及び、半導体装置の製造方法

【課題】結晶欠陥および金属汚染低減が可能な半導体基体の処理方法、そのための装置、また、それを用いた半導体装置の製造方法を提供する。

【解決手段】CとNとを含む混合ガスをプラズマ化してCN活性種を生成し、生成したCN活性種により半導体基体11の半導体層の表面を処理する。特に、前記処理としては、前記半導体基体11の表面の半導体層を前記CN活性種によりパッシベートすることを含む。さらに、そのことにより、表面汚染金属および半導体中の欠陥を除去する。

(もっと読む)

エネルギー線検出装置の製造方法

【課題】 信号電荷の収集効率を向上する。

【解決手段】 半導体基板の表面1000の第1区域1001の下に設けられた第1半導体領域131と、表面1000の第2区域1002の下に設けられ、接続部300に接続された第2半導体領域132と、表面1000の第1区域1001と第2区域1002との間の第3区域1003の下に設けられた第3半導体領域133とを有するエネルギー線変換装置の製造方法において、

第1半導体領域131及び第3半導体領域131を、第1区域1001及び第3区域1003を覆い、且つ、第3区域1003を覆う部分203の厚さが第1区域1001を覆う部分201の厚さよりも薄い緩衝膜200を介して、半導体基板100にイオン注入を行うことによって形成する。

(もっと読む)

光学素子およびその製造方法

【課題】サイズが小さくなっても、受光部などの光学領域への集光を向上させることが可能な光学素子を提供する。

【解決手段】光学領域(フォトダイオードである受光部102)を有する半導体基板101と、半導体基板101の上に配置された透明絶縁膜111を有し、透明絶縁膜111は、光学領域直上の第1の領域(遮光膜110によって挟まれる領域)と、第1の領域の上の第2の領域を有し、透明絶縁膜111は、第2の領域と同じ高さにあり、平面視において第2の領域の外側に位置する第3の領域(遮光膜110の上の領域)を有し、第1の領域が有する空孔115の空孔径は第3の領域が有する空孔115の空孔径よりも小さい。

(もっと読む)

フォトマスク、露光方法、及び半導体装置の製造方法

【課題】センサ素子領域が形成されない領域を抑制し、センサ素子領域を広く確保したチップを形成することができる、フォトマスク、露光方法、及び半導体装置の製造方法を提供する。

【解決手段】フォトマスク10では、センサ素子領域22の短辺側のみにガードリングパターン24aが設けられた第1エリア20と、センサ素子領域22の長辺に沿うような形状、かつガードリングパターン24aと接続されるように両端部が鉤状に曲折したガードリングパターン24bを線対称に一対形成された第2エリア40と、が形成されている。当該フォトマスク10を用いてウエハ基板50上に露光装置のブラインド機能を用いて各領域を露光する際は、ガードリングパターン24aの端部及びガードリングパターン24bの端部が接続されるように繰り返し露光すると共に、ガードリングパターン24aの端部同士が接続されるように繰り返し露光する。

(もっと読む)

固体撮像素子及びその製造方法

【課題】製造工程数の増大、ボイドによる感度低下、及び光利用効率の低下を防ぐことが可能な固体撮像素子の製造方法を提供する。

【解決手段】シリコン基板1内に形成された光電変換部(PD)2と、PD2の上方に形成されたカラーフィルタ7と、カラーフィルタ7上方に形成されたマイクロレンズ8と、マイクロレンズ8とPD2との間に形成され、マイクロレンズ8で集光された光をPD2に導く光導波部9とを有する画素部を複数有する固体撮像素子の製造方法であって、光導波部9を形成する工程は、基板1上方に、PD2上方に凹部5Kを有する絶縁膜5を形成する第一の工程と、絶縁膜5上に、絶縁膜5よりも屈折率が高くかつPD2上方に凹部5K内にまで達する凹部6Kを有する高屈折率材料膜6を形成する第二の工程と、高屈折率材料膜6上に、高屈折率材料膜6よりも屈折率が低くかつ凹部6Kを埋めるカラーフィルタ7を形成する第三の工程とを含む。

(もっと読む)

SOI基板のエッチング方法並びにSOI基板上の裏面照射型光電変換モジュール及びその作製方法

【課題】SOI基板のエッチング方法であって、Si基板を高速かつ平坦にウェットエッチングすることのできるエッチング方法を提供すること。

【解決手段】フッ硝酸は、一般にHF(a)HNO3(b)H2O(c)(ここで、a、b及びcの単位はwt%、a+b+c=100)と書ける。本発明者らは、組成を適切に選択することで、高濃度フッ硝酸によるSiO2層のエッチングレートがSi基板と比較して著しく低くなることに見出し、Si基板を、SiO2層が露出するまでエッチングを行う。このようにすることで、Si基板を高速にエッチングすることができ、かつ、エッチングされた表面の平坦性を従来に比して顕著に向上することができる。高濃度フッ硝酸の組成が僅かにSiO2層をエッチングするものであっても、Si基板のエッチングが高速に終了するため、実質的にSiO2層のエッチングはほとんど進まず、平坦な表面を有するSiO2層が露出する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体層の表面から貫通孔絶縁層が後退した場合においても、半導体層と貫通電極との絶縁性を確保する。

【解決手段】貫通孔6には、貫通孔絶縁層7、8を介して貫通電極9が埋め込まれ、貫通孔絶縁層7、8は、半導体層3の表面から後退するようにして形成され、半導体層3と貫通電極9との間には、貫通孔絶縁層7、8の後退部分の対応した凹部10が形成され、貫通電極9の側壁には、凹部10に埋め込まれたサイドウォール絶縁膜12が形成される。

(もっと読む)

半導体デバイスの製造方法、半導体デバイス及び基板処理装置

【課題】レンズの反射を抑制することが可能な酸化膜を低温下で形成する。

【解決手段】基板に形成されたレンズの上に、第1元素を含む第1原料、第2元素を含む第2原料、酸化剤および触媒を用いて空気の屈折率より大きく、レンズの屈折率より小さい屈折率を有する下層酸化膜を形成する下層酸化膜形成工程と、下層酸化膜の上に、第1原料、酸化剤および触媒を用いて空気の屈折率より大きく、下層酸化膜の屈折率より小さい屈折率を有する上層酸化膜を形成する上層酸化膜形成工程と、を有する。

(もっと読む)

酸化物半導体薄膜の製造方法および酸化物半導体薄膜、薄膜トランジスタの製造方法および薄膜トランジスタ、並びに薄膜トランジスタを備えた装置

【課題】300℃以上の高温での熱処理することなく、再現性が高く、大面積デバイス、特にフレキシブルデバイス作製に適したIGZO系酸化物薄膜を製造する。

【解決手段】In,Ga,Zn,Oを主たる構成元素とし、組成比が11/20≦Ga/(In+Ga+Zn)≦9/10、且つ3/4≦Ga/(In+Ga)≦9/10、且つZn/(In+Ga+Zn)≦1/3を満たす酸化物半導体薄膜をスパッタリング法により、アルアゴンガス雰囲気下で酸素ガスを導入することなく成膜し、成膜された酸化物半導体薄膜に対して、酸化性雰囲気中で100℃以上、300℃未満の熱処理を施す。

(もっと読む)

半導体装置の製造方法

【課題】半導体基板の外周での配線層の露出を防ぐことができる半導体装置の製造方法を得ること。

【解決手段】半導体基板の第1の面に活性層を形成し、活性層上に配線層を形成して、配線層を覆うように絶縁層を形成する。そして、絶縁層を介して半導体基板の第1の面と支持基板とを接合し、支持基板に接合された半導体基板を、活性層を第2の面側から覆う所定の厚さの前記半導体基板を残して薄厚化する。薄厚化後の半導体基板の第2の面の外周部および側面に保護膜を形成して、保護膜が形成されていない領域の半導体基板を、活性層が露出するよう除去する。

(もっと読む)

酸化物半導体薄膜およびその製造方法、並びに薄膜トランジスタ、薄膜トランジスタを備えた装置

【課題】生産性、組成均一性を向上させることができ、かつ低温アニール時に低抵抗化が起こらず、再現性が高く、大面積デバイス、特にフレキシブルデバイス作製に適した酸化物半導体薄膜を得る。

【解決手段】In、GaおよびOを主たる構成元素とする酸化物半導体薄膜であって、In,Gaの組成比が3/4≦Ga/(In+Ga)≦9/10であり、かつ、抵抗率が1Ωcm以上、1×106Ωcm以下を満たすものとする。

(もっと読む)

固体撮像装置の製造方法および固体撮像装置

【課題】固体撮像装置の透過率特性に生ずるリップルを抑制することが可能な、カラーフィルタを具備しない固体撮像装置の製造方法を提供する。

【解決手段】フォトダイオード13上に、第1の層間絶縁膜18、第1のメタル配線19、第2の層間絶縁膜20、第2のメタル配線21、パッシベーション膜22を形成する工程と、第2のメタル配線21間のパッシベーション膜22上に複数の第1の開口部26−1を有し、第2のメタル配線21上のパッシベーション膜22上に第2の開口部26−2を有するレジスト層27を、パッシベーション膜22上に形成する工程と、レジスト層27をマスクとして用いて、パッシベーション膜22をエッチングし、第1の開口部26−1に微小突起23を形成する工程と、これによって第2のメタル配線21上のパッシベーション膜22に形成された開口部28に電極パッドを形成する工程と、を具備する。

(もっと読む)

固体撮像装置、及び撮像システム

【課題】 固体撮像装置において、パッドからの外来ノイズの混入を低減する。

【解決手段】 光電変換素子が主面に配された第1基板と、第1配線構造と、周辺回路の少なくとも一部が主面に配された第2基板と、第2配線構造と、を有し、第1基板、第1配線構造、第2配線構造、及び第2基板がこの順に配置された固体撮像装置において、固体撮像装置は周辺回路部を駆動するための電圧が供給されるパッドと保護ダイオード回路とを有し、保護ダイオード回路は前記第2基板に配されている。

(もっと読む)

固体撮像装置の製造方法

【課題】異なる高さのマイクロレンズを有する固体撮像装置を、製造工程を増加させることなく製造可能な固体撮像装置の製造方法を提供すること。

【解決手段】半導体基板上の透明樹脂層を露光する工程と、互いに高さが異なる第1、第2の樹脂パターンを形成する工程と、互いに高さが異なる第1、第2のマイクロレンズを形成する工程と、を具備する固体撮像装置の製造方法。露光する工程は、第1の透過領域、およびこの領域よりも高い透過率の第2の透過領域を有するグレーティングマスクを用いて透明樹脂層を露光する工程である。第1、第2の樹脂パターンを形成する工程は、透明樹脂層を現像することにより、第1の樹脂パターンおよびこのパターンよりも低い第2の樹脂パターンを形成する工程である。第1、第2のマイクロレンズを形成する工程は、第1の樹脂パターンおよび第2の樹脂パターンを熱処理することにより、第1のマイクロレンズおよびこのレンズよりも低い第2のマイクロレンズを形成する工程である。

(もっと読む)

固体撮像素子およびその製造方法、電子情報機器

【課題】表面側の受光センサと裏面側のマイクロレンズおよびカラーフィルタとのアライメント精度をより上げる。

【解決手段】裏面照射タイプにおいて、受光センサ4に対するアライメントマークと同一のアライメントマークを基準として基板表面に位置合わせ用マーク(所定形状のポリシリコン層9)形成する。裏面加工時に、素子分離膜7の表面上まで開口された開口部3Aを通して透明な素子分離膜7下の位置合わせ用マーク(所定形状のポリシリコン層9)をよりはっきりと確認しつつ、位置合わせ用マーク(所定形状のポリシリコン層9)に基づいて、基板表面側フォトダイオードである受光センサ4に対して基板裏面側のマイクロレンズ6およびその下のカラーフィルタ5をアライメント精度をより上げて形成することができる。

(もっと読む)

固体撮像装置及びその製造方法

【課題】集光率を向上できると共に、エッチングダメージ層の形成を防止する。

【解決手段】固体撮像装置は、画素部40と周辺回路部50を有する半導体基板1と、画素部の上部に形成されたフォトダイオード(PD)部3及びフローティングディフュージョン(FD)部20と、周辺回路部の上部に形成された複数のソース/ドレイン領域18と、画素部及び周辺回路部の上に形成されたゲート絶縁膜4と、PD部とFD部との間に形成された転送ゲート電極5と、各ソース/ドレイン領域同士の間に形成された周辺ゲート電極6と、PD部の上を覆うように形成された反射防止膜13と、転送ゲート電極の側面に形成された第1のサイドウォール15と、周辺ゲート電極の側面に形成された第2のサイドウォール16とを備えている。反射防止膜、第1のサイドウォール及び第2のサイドウォールは、酸化膜と窒化膜とを含む積層膜である。

(もっと読む)

マイクロレンズ非搭載の光電変換膜積層型固体撮像素子及びその製造方法並びに撮像装置

【課題】撮像素子前面に貼り付ける透明基板の下に空隙を必要とせず、また、接着材として屈折率に依存しない透明樹脂を選択できるようにした小型,薄型の固体撮像素子を提供する。

【解決手段】半導体基板121と、半導体基板121の光入射側上層に積層された光電変換膜130と、半導体基板121の表面部に形成され光電変換膜130が入射光量に応じて検出した信号電荷量に応じた信号を撮像画像信号として外部に読み出す信号読出手段(図示省略)と、光電変換膜130の光入射側上層に透明樹脂を接着材として貼り付けられた透明基板(図示省略)と、前記信号読出手段に配線接続され半導体基板121に貫通して設けられると共に半導体基板121の光電変換膜130が設けられた面と反対側の面に露出して設けられた電気的接続端子113とを備える。

(もっと読む)

1 - 20 / 146

[ Back to top ]