Fターム[4M119AA07]の内容

MRAM・スピンメモリ技術 (17,699) | 目的 (2,141) | 誤書込防止 (92)

Fターム[4M119AA07]に分類される特許

1 - 20 / 92

記憶素子、記憶装置

【課題】熱安定性の情報書き込み方向に対する非対称性をすくなくし特性バランスに優れた記憶素子を実現する。

【解決手段】記憶素子は、膜面に垂直な磁化を有し、情報に対応して磁化の向きが変化される記憶層と、上記記憶層に記憶された情報の基準となる膜面に垂直な磁化を有する磁化固定層と、上記記憶層と上記磁化固定層の間に設けられる非磁性体による中間層とを有する層構造を備える。そして上記層構造の積層方向に電流を流すことで記憶層の磁化の向きが変化して、記憶層に対して情報の記録が行われる。この場合に、磁化固定層を少なくとも2層の強磁性層とCrを含む非磁性層とを有する積層フェリピン構造とする。

(もっと読む)

記憶素子、記憶装置

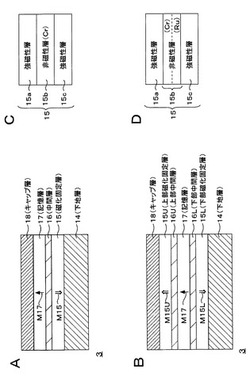

【課題】書き込みエラーを生じることなく、短い時間で書き込み動作を行うことができる記憶素子及び記憶装置を提供する。

【解決手段】情報に対応して磁化の向きが変化される記憶層14と、磁化の向きが固定された磁化固定層12と、上記記憶層14と上記磁化固定層12との間に配された非磁性体による中間層13と、垂直磁気異方性誘起層15とを含む層構造を有する記憶素子3を構成する。そして、上記記憶層14が、第1の強磁性層14aと第1の結合層14bと第2の強磁性層14cと第2の結合層14dと第3の強磁性層14eとが同順に積層されて、上記第1の強磁性層14aが上記中間層13に接し、上記第3の強磁性層14eが上記垂直磁気異方性誘起層15に接し、上記結合層14b,14dを介して隣接する上記強磁性層14a,14c,14eの磁化の向きが膜面に垂直な方向から傾斜している。

(もっと読む)

記憶素子、記憶装置

【課題】熱安定性の情報書き込み方向に対する非対称性をすくなくし特性バランスに優れた記憶素子を実現する。

【解決手段】記憶素子は、膜面に垂直な磁化を有し、情報に対応して磁化の向きが変化される記憶層と、上記記憶層に記憶された情報の基準となる膜面に垂直な磁化を有する磁化固定層と、上記記憶層と上記磁化固定層の間に設けられる非磁性体による中間層とを有する層構造を備える。そして上記層構造の積層方向に電流を流すことで記憶層の磁化の向きが変化して、記憶層に対して情報の記録が行われる。この場合に、磁化固定層を少なくとも2層の強磁性層と非磁性層とを有する積層フェリピン構造とし、かつ、いずれかの上記強磁性層に接して反強磁性酸化物層が形成されているようにする。

(もっと読む)

記憶素子、記憶装置

【課題】熱安定性を確保して特性バランスに優れた記憶素子を実現する。

【解決手段】記憶素子は、膜面に垂直な磁化を有し、情報に対応して磁化の向きが変化される記憶層と、上記記憶層に記憶された情報の基準となる膜面に垂直な磁化を有する磁化固定層と、上記記憶層と上記磁化固定層の間に設けられる非磁性体による中間層とを有する層構造を備える。

そして、上記記憶層は非磁性体と酸化物が積層された積層構造層を含み、上記層構造の積層方向に電流を流すことにより、上記記憶層の磁化の向きが変化して、上記記憶層に対して情報の記録が行われる。

(もっと読む)

記憶素子、記憶装置

【課題】書き込みエラーを生じることなく、短い時間で書き込み動作を行うことができる記憶素子及び記憶装置を提供する。

【解決手段】情報に対応して磁化の向きが変化される記憶層と、磁化の向きが固定された磁化固定層と、上記記憶層と上記磁化固定層との間に配された非磁性体による中間層とを含む層構造を有する記憶素子を構成する。そして上記磁化固定層が、少なくとも2つの強磁性層が結合層を介して積層され、上記2つの強磁性層が上記結合層を介して磁気的に結合し、上記2つの強磁性層の磁化の向きが膜面に垂直な方向から傾斜している。このような構成により、上記記憶層及び上記磁化固定層のそれぞれの磁化の向きがほぼ平行又は反平行とされてしまうことによる磁化反転時間の発散を効果的に抑えることができ、書き込みエラーを低減し、より短い時間で書き込みができる。

(もっと読む)

半導体記憶装置

【課題】誤書込を抑制することが可能なMRAM装置を提供する。

【解決手段】三角波状のパルス電流Iwをワード線に流してパルス磁場をトンネル磁気抵抗素子の自由層に印加する。また、パルス電流Iwがピークに達した後にピークに達する三角波状のパルス電流Ibをビット線に流してパルス磁場を自由層に印加する。これにより、自由層の磁化ベクトルの歳差運動をその熱揺動よりも大きくして、パルス電流Iwのみで自由層の磁化方向が反転するのを防止できる。また、パルス電流Ibによって自由層の磁化方向を確実に反転させることができる。

(もっと読む)

半導体装置

【課題】抵抗変化素子を備える半導体装置(半導体チップ)のチップ面積を削減すること。

【解決手段】半導体装置(1)は、半導体基板(50)上に形成されたトランジスタ(71)を含む下層回路(70)と、半導体基板(50)の上方の配線層(60)に形成されたメモリセルアレイ(20)と、を備える。メモリセルアレイ(20)の各メモリセル(MC)は、配線層(60)に形成された抵抗変化素子(40)を記憶素子として備る。メモリセルアレイ(20)は、メモリセル(MC)の直下に当該メモリセル(MC)との電気的接続用のビアが形成されていない第1領域(RF)を有している。下層回路(70)は、第1領域(RF)の少なくとも一部とオーバーラップするように配置されている。

(もっと読む)

不揮発性記憶装置

【課題】安定した動作が可能な不揮発性記憶装置を提供する。

【解決手段】実施形態によれば、磁気記憶素子と制御部とを備えた不揮発性記憶装置が提供される。磁気記憶素子は積層体を含む。積層体は第1積層部と第2積層部とを含む。第1積層部は、磁化が固定された第1強磁性層と、磁化の方向が可変の第2強磁性層と、第1強磁性層と第2強磁性層との間に設けられた第1非磁性層と、を含む。第2積層部は、積層方向に沿って第1積層部と積層される。第2積層部は、通電される電流によって磁化が回転して発振が生じる第3強磁性層と、磁化が固定された第4強磁性層と、第3強磁性層と第4強磁性層との間に設けられた第2非磁性層と、を含む。制御部は、第2強磁性層の磁化の向きに応じた第3強磁性層の発振の周波数の変化を検出することで、第2強磁性層の磁化の向きを読み出す読み出し部を含む。

(もっと読む)

半導体記憶装置

【課題】参照セルにおける誤書き込みの発生を抑制し、より高精度にデータを読み出すことが可能な半導体記憶装置を提供する。

【解決手段】半導体記憶装置100の参照セルは、第3のビット線BL3に一端が接続され且つ第2のワード線RWLにゲートが接続された第3の選択トランジスタTr3と、第3の選択トランジスタの他端に一端が接続され且つ第3の電圧端子G3に他端が接続された第3の抵抗変化素子R3とを有する第3のメモリセルM3と、第4のビット線BL4に一端が接続された第4の抵抗変化素子R4と、第4の抵抗変化素子の他端と第4の電圧端子G4との間に接続され且つ第2のワード線RWLにゲートが接続された第4の選択トランジスタTr4とを有する第4のメモリセルM4から構成される。さらに第3のビット線BL3と前記第4のビット線BL4との間に接続され、読み出し動作時に電位とを等価にするための第1の電位制御回路Ti1を備える。

(もっと読む)

記憶素子及び記憶装置

【課題】外部放射線に対し耐性を有し、誤動作なく安定した動作する信頼性の高い記憶素子の提供。

【解決手段】記憶素子は、情報を磁性体の磁化状態により保持する記憶層と、記憶層に記憶された情報の基準となる磁化を有する磁化固定層と、記憶層と上記磁化固定層の間に設けられる非磁性体による中間層とを有する。そして記憶層、中間層、磁化固定層を有する層構造の積層方向に流れる電流に伴って発生するスピントルク磁化反転を利用して記憶層の磁化を反転させることにより情報の記憶を行うとともに、記憶層は、Bを含有する強磁性層を含み、Bにふくまれる10Bの同位体比率が、自然界における19.9%よりも低くなっている。

(もっと読む)

磁気記憶素子および磁気記憶装置

【課題】半選択状態になった磁気記憶素子のデータの誤反転を抑制することにより信頼性の高い書き込み動作を行うことができる磁気記憶素子、およびこれを用いた磁気記憶装置を提供する。

【解決手段】磁化容易軸91と磁化困難軸92とを有する記録層3は、平面視においてすべての領域が第1導電層WTまたは第2導電層BLの少なくとも一方と重なる。磁化容易軸91に沿い、記録層3と平面視において重なる寸法が最大となる第1の線分の第1の端点TP,BPは、第2導電層BLと平面視において重ならない。上記第1の線分の中点を通り、平面視において第1の線分に直交し、記録層3と平面視において重なる第2の線分の1対の端点である第2の端点LP,RPのうち少なくとも一方は、第1導電層WTと平面視において重ならない。

(もっと読む)

磁気素子及び不揮発性記憶装置

【課題】読み出し時の誤書き込みを抑制する磁気素子及び不揮発性記憶装置を提供する。

【解決手段】実施形態によれば、第1導電層と、第2導電層と、中間配線と、第1積層部と、第2積層部と、を備えた磁気素子が提供される。中間配線は、第1導電層と第2導電層との間に設けられる。第1積層部は、第1導電層と中間配線との間に設けられる。第1積層部は、第1方向に磁化が固定された第1強磁性層と、第1強磁性層と積層され、磁化の方向が可変である第2強磁性層と、第1強磁性層と第2強磁性層との間に設けられた第1非磁性層と、を含む。第2積層部は、第2導電層と中間配線との間に設けられる。第2積層部は、磁化の方向が可変である第3強磁性層と、第3強磁性層と積層され、第2方向に磁化が固定された第4強磁性層と、第3強磁性層と第4強磁性層との間に設けられた第2非磁性層と、を含む。

(もっと読む)

記憶素子及び記憶装置

【課題】垂直磁気異方性を利用したST−MRAMの書込電流の低減及び熱安定性を向上し、回路の複雑化や読み出し速度の低下を防止する。

【解決手段】膜面に垂直な磁化を有し、情報に対して磁化の向きが変化する記憶層と、膜面に垂直な磁化を有する磁化固定層と、上記記憶層と上記磁化固定層の間の非磁性体による絶縁層とを有し、上記記憶層、上記絶縁層、上記磁化固定層の積層方向に流れる電流により発生するスピントルク磁化反転を利用して上記記憶層の磁化を反転させることにより情報の記憶を行い、上記記憶層を、磁性層と導電性酸化物との積層構造で構成する。記憶層において磁性層と酸化物層と積層構造を採ることで垂直磁気異方性が誘起され書込電流が低減し熱安定性が向上し、当該酸化物として導電性酸化物が用いられることで読み出し時にトンネル磁気抵抗効果に寄与しない抵抗成分が小となり、回路の複雑化や読み出し速度の低下を防止する。

(もっと読む)

記憶素子及び記憶装置

【課題】垂直磁気異方性を利用したST−MRAMの書込電流の低減及び熱安定性の向上を図り、回路の複雑化や読み出し速度の低下の防止を図る。

【解決手段】膜面に垂直な磁化を有し、情報に対し磁化の向きが変化する記憶層と、上記記憶層に記憶された情報の基準となる膜面に垂直な磁化を有する磁化固定層と、上記記憶層と上記磁化固定層の間に非磁性体による絶縁層を有し、上記記憶層、上記絶縁層、上記磁化固定層の積層方向に流れる電流により発生するスピントルク磁化反転を利用して上記記憶層の磁化を反転させることにより情報の記憶を行い、上記記憶層に接し上記絶縁層と反対側の層を、導電性酸化物で構成する。記憶層との界面に酸化物を用いることで垂直磁気異方性が誘起され書込電流低減、熱安定性向上を図り、導電性酸化物を用いることで読み出し時のトンネル磁気抵抗効果に寄与しない抵抗成分が小となり、回路の複雑化や読み出し速度低下の防止を図る。

(もっと読む)

半導体装置

【課題】磁気抵抗素子を有する半導体装置であって、フリー層に所望の磁化方向と反対方向の磁界の成分が印加されることによる誤動作を抑制することが可能な半導体装置を提供する。

【解決手段】半導体基板の主表面上に位置する、磁化自由層を有する磁気抵抗素子TMRと、磁気抵抗素子TMRの下方に位置し、第1方向に向けて延び、発生する磁界により磁化自由層の磁化状態を変化させることが可能な第1配線DLと、磁気抵抗素子TMRの上方に位置し、第2方向に向けて延び、発生する磁界により磁化自由層の磁化状態を変化させることが可能な第2配線BLとを備えている。磁化自由層は、第2方向に対して対称であり、平面視における第2方向に垂直な方向に対して非対称である。上記第1配線DLは、磁化自由層と平面視において重なる領域において、磁化自由層が磁化されやすい方向に延びる磁化容易軸の延在する方向Heに沿うように延在している。

(もっと読む)

磁気抵抗効果メモリ

【課題】読み出しディスターブを低減する磁気抵抗効果メモリを提供する。

【解決手段】本発明の例に関わる磁気抵抗効果メモリは、磁化方向が不変な第1の磁性層と、磁化方向が可変な第2の磁性層と、第1の磁性層と第2の磁性層の間に設けられた中間層とを有する磁気抵抗効果素子1と、磁気抵抗効果素子1にパルス形状の読み出し電流を流して、前記磁気抵抗効果素子に記憶されたデータを判別する読み出し回路2と、を具備し、読み出し電流のパルス幅は、第2の磁性層内に含まれる磁化が、初期状態から共動してコヒーレントに歳差運動するまでの期間より短い。

(もっと読む)

耐久性が改良された熱アシスト磁気ランダムアクセスメモリ素子

【課題】 耐久性が改良された熱アシスト磁気ランダムアクセスメモリ素子を提供する。

【解決手段】 本発明は、熱アシストスイッチング書き込み操作に適した磁気メモリ素子であって、磁気トンネル接合の一端と電気的に連絡した電流線を備え、磁気トンネル接合が、固定磁化を有する第1の強磁性層と、所定の高温しきい値で自由に整列させることができる磁化を有する第2の強磁性層と、第1の強磁性層と第2の強磁性層の間に提供されたトンネル障壁とを備え、電流線が、書き込み操作中に磁気トンネル接合を通して加熱電流を流すように適合され、前記磁気トンネル接合が、加熱電流が磁気トンネル接合を通して流されるときに熱を発生するように適合された少なくとも1つの加熱要素と、前記少なくとも1つの加熱要素と直列の熱障壁とをさらに備え、前記熱障壁が、磁気トンネル接合内部で前記少なくとも1つの加熱要素によって発生する熱を閉じ込めるように適合される磁気メモリ素子に関する。

(もっと読む)

抵抗変化型メモリ

【課題】 メモリの動作特性の向上を図る。

【解決手段】実施形態の抵抗変化型メモリは、ビット線BLとワード線WLと、第1エミッタ21と、第1ベース23と、第1コレクタ22とを有する、第1駆動型の第1バイポーラトランジスタ2と、第2エミッタ31と、第2ベース33と、第2コレクタ32とを有する第2駆動型の第2バイポーラトランジスタ3と、第1及び第2端子を有する抵抗変化型メモリ素子1と、を具備し、メモリ素子1の第1端子は第1及び第2エミッタ21,31に接続され、メモリ素子1の第2端子は、ビット線BLに接続され、第1及び第2ベース23,33はワード線WLに接続される。

(もっと読む)

不揮発性記憶装置およびその製造方法

【課題】不揮発性記憶装置およびその製造方法に関し、抵抗変化材料を利用したメモリの信頼性の向上を実現する。

【解決手段】積半導体素子を形成する基板の上方に、第1方向に延伸するように複数の金属配線層2を設け、金属配線層2のさら上方に、前記第1方向に直交する第2方向に延伸するように複数の金属配線層3を設ける。また、金属配線層2と金属配線層3とが交差する空間のそれぞれにメモリセルを設ける。前記メモリセルは、選択素子と相変化材料層7とが並列接続された構成とする。ここで、前記選択素子の前記第1方向の寸法が、相変化材料層7の前記第1方向の寸法よりも大きくなるように加工する。

(もっと読む)

半導体装置

【課題】電源電圧の変動に起因した書込電流の変動を抑制する。

【解決手段】ドライブ回路25において、第1のMOSトランジスタPMは、第1および第2の電源ノード28,29間にデータ書込線DLと直列に設けられる。第2のMOSトランジスタPSは、第1のMOSトランジスタPMと並列に設けられる。第3および第4のMOSトランジスタPa,Pbは、互いに同じ電流電圧特性を有する。第1の素子Eaは、第1および第2の電源ノード28,29間に第3のMOSトランジスタPaと直列に接続される。第2の素子Ebは、第1および第2の電源ノード28,29間に第4のMOSトランジスタPbと直列に接続され、第1の素子Eaの電流電圧特性曲線と交差する電流電圧特性を有する。比較器30は、第1の素子Eaにかかる電圧と第2の素子Ebにかかる電圧とを比較し、比較結果に応じて第2のMOSトランジスタPSをオンまたはオフにする。

(もっと読む)

1 - 20 / 92

[ Back to top ]