Fターム[4M119AA20]の内容

MRAM・スピンメモリ技術 (17,699) | 目的 (2,141) | その他の目的 (79)

Fターム[4M119AA20]に分類される特許

1 - 20 / 79

記憶素子、記憶装置

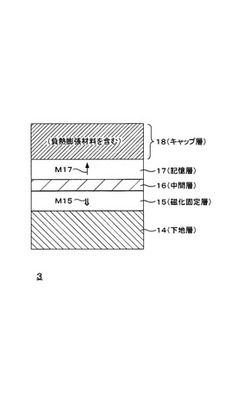

【課題】環境温度によらず、熱安定性を確保して特性バランスに優れた記憶素子を実現する。

【解決手段】記憶素子は、膜面に垂直な磁化を有し、情報に対応して磁化の向きが変化される記憶層と、上記記憶層に記憶された情報の基準となる膜面に垂直な磁化を有する磁化固定層と、上記記憶層と上記磁化固定層の間に設けられる非磁性体による中間層とを有する層構造を備える。そして上記層構造の積層方向に電流を流すことで記憶層の磁化の向きが変化して、記憶層に対して情報の記録が行われる。この場合に、記憶層は正の磁歪定数を持つ磁性層を有するようにし、上記層構造に加えてさらに、負熱膨張材料層が設けられるようにする。

(もっと読む)

半導体装置

【課題】直流電源配線に電流が流れたか否かを検出可能な回路を備えた半導体装置を提供する。

【解決手段】半導体装置において、駆動回路BLDU,BLDD,BLBDU,BLBDDは、電流磁界またはスピン注入によってトンネル磁気抵抗素子TMR,TMRBを第1の磁化状態に初期設定するために、制御信号線BL,BLBに直流電流を流す。電源配線DLは、トンネル磁気抵抗素子TMR,TMRBに近接して設けられる。ここで、トンネル磁気抵抗素子TMR,TMRBは、電源配線DLに直流電流が流れるときに生じる電流磁界によって第2の磁化状態に変化する。センスアンプ10は、トンネル磁気抵抗素子TMR,TMRBが第1の磁化状態から第2の磁化状態に変化したか否かを判定するために、制御信号線BL,BLBを介してトンネル磁気抵抗素子TMR,TMRBに流れる電流を検出する。

(もっと読む)

半導体集積回路およびその動作方法

【課題】半導体集積回路の内蔵メモリとしてのMRAMへの不正アクセスに対する保護を改善すること。

【解決手段】半導体集積回路(10)は、プロセッサ(1)と不揮発性メモリ(3)とを具備する。不揮発性メモリ(3)は、複数の磁気ランダムアクセスメモリセルと、複数の磁気リードオンリーメモリセルとを含む。複数の磁気ランダムアクセスメモリセルはプロセッサ(1)による通常書き込みによって書き換えが可能とされ、複数の磁気リードオンリーメモリセルはプロセッサ(1)による通常書き込みによって書き換えが不可能とされる。不揮発性メモリ(3)と接続された感知回路(2)は、不揮発性メモリ(3)の不正アクセスによる複数の磁気リードオンリーメモリセルの状態遷移を感知する。状態遷移に応答して、感知回路(2)は不正アクセスの検出結果をプロセッサ(1)に通知する。

(もっと読む)

半導体装置

【課題】オフリーク電流の抑制および駆動電流の増大を図ることが可能な半導体装置を提供する。

【解決手段】実施形態の半導体装置において、ゲート電極は、第1および第2のソース・ドレイン領域の間に設けられた第1リセス内に少なくとも一部がゲート絶縁膜を介して埋め込まれて第1および第2のソース・ドレイン領域よりも深い位置まで形成される。チャネルは、素子領域においてゲート絶縁膜に隣接して第1および第2のソース・ドレイン領域の間に形成される。一対の応力付与部は、素子分離領域において、ゲート電極のゲート幅方向に垂直な面内において第1および第2のソース・ドレイン領域の下部のチャネルと重複する領域に設けられ、素子分離領域の構成材料と異なる絶縁材料からなりチャネルに対してゲート幅方向の両側から応力を付与する。

(もっと読む)

磁気メモリチップを有する半導体装置の製造方法

【課題】アセンブリ段階において外部磁場から磁気メモリチップを保護する。

【解決手段】主面に磁気メモリ素子および複数のワイヤボンドパッドが形成された磁気メモリチップを準備する。シリコンより高透磁率を有する第1の磁気シールド板を磁気メモリチップの主面に搭載する。磁気メモリチップをリードフレームのダイパッド上に搭載しダイアタッチフィルムにより接着する。磁気メモリチップのワイヤボンドパッドとリードフレームのリードとをワイヤで電気的に接続する。磁気メモリチップ、磁気シールド板、ワイヤ及びリードの一部を樹脂により封止する。複数の磁気メモリチップを有するシリコンウェハを準備し、シリコンウェハの裏面を研削することによりシリコンウェハを所定の厚さまで薄くしてダイアタッチフィルムを張り付けた後にシリコンウェハをダイシングして各々がダイアタッチフィルムをその裏面に有する複数の磁気メモリチップを形成する。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】製造コストの増加を抑えつつ、直列に接続されたMTJ素子を所望の特性の抵抗体として機能させることが可能な半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、磁化方向に応じて抵抗値が変化可能な複数の記憶用MTJ素子が、半導体基板上に配置されたメモリセルアレイ領域を備える。半導体記憶装置は、複数の抵抗用MTJ素子が、前記半導体基板上に第1の方向および前記第1の方向に垂直な第2の方向に沿って配置された抵抗素子領域を備える。前記半導体基板の上面に平行な前記抵抗用MTJ素子の第1の断面の面積は、前記半導体基板の前記上面に平行な前記記憶用MTJ素子の第2の断面の面積よりも、大きい。

(もっと読む)

三値連想メモリ用デュアル接合式磁気ランダムアクセスメモリセルとそのメモリセルの書込み及び読出し方法

【課題】 本発明は、磁化方向が自由な軟強磁性層と第一の記録磁化を有する第一の硬強磁性層の間に配備された第一のトンネル障壁層と、軟強磁性層と第二の記録磁化を有する第二の硬強磁性層の間に配備された第二のトンネル障壁層とを備えた、第一の所定の高い閾値温度で第一の記録磁化を自由な方向に向けることができ、第二の所定の高い閾値温度で第二の記録磁化を自由な方向に向けることができ、第一の所定の高い閾値温度が第二の所定の高い閾値温度よりも高いMRAMセルに関する。

【解決手段】 本MRAMセルは、三値連想メモリ(TCAM)として使用して、三つまでの異なる状態レベルを記録することができる。本MRAMセルは、サイズが小さく、低コストで製造することができる。

(もっと読む)

マイクロコンピュータ周辺装置、初期設定方法、半導体集積装置

【課題】半導体集積回路装置におけるマイクロコンピュータ周辺装置の高速起動。

【解決手段】マイクロコンピュータ周辺装置は、マイクロコンピュータから受信した初期設定コマンドに基づく設定信号をレジスタを介して機能回路部に出力し、初期設定を行う。ここで、レジスタにおける設定信号のデータをMTJ素子等の不揮発性記憶素子を用いた保持回路で記憶しておく。電源再投入時には、保持回路に記憶された設定信号のデータで初期設定を行う。

(もっと読む)

トランジスタおよびメモリアレイ

【課題】大きな順方向−逆方向電流比を有するスイッチングデバイスを提供する。

【解決手段】トランジスタは、ソースと、ドレインと、ゲート領域と、ソースバリヤと、ドレインバリヤとを含む。ゲート領域は、ゲートと、アイランドと、ゲート酸化物とを含み、ゲート酸化物は、ゲートとアイランドとの間に配置される。ゲートおよびアイランドは、互いに、同時活性的に結合される。ソースバリヤはゲート領域からソースを分離し、ドレインバリヤはゲート領域からドレインを分離する。

(もっと読む)

集積磁気薄膜増強回路素子を有する磁気抵抗ランダムアクセスメモリ(MRAM)

半導体装置および半導体装置の製造方法

【課題】MRAMにおいては、書き込み電流の低減やディスターブ回避を目的に、書き込みに使用する配線を強磁性体膜で覆うクラッド配線構造がよく用いられている。また、高信頼性製品の信頼性確保のためCu配線中に微量のAlを添加するCuAl配線が広く使用されている。MRAMも高信頼性製品に搭載される可能性が高く、信頼性は重要である。しかし、クラッド配線は、もともと配線抵抗が高いCuAl配線の配線抵抗を更に上昇させるというデメリットがあるため、両方の技術を同時に使用すると配線抵抗のスペックを満たさなくなる可能性が高い。

【解決手段】本願発明は、多層銅埋め込み配線を有する半導体装置において、MRAMメモリセルマトリクス領域を構成する複数の銅埋め込みクラッド配線の銅配線膜を比較的純粋な銅で構成し、これらの配線層よりも下層の銅埋め込み非クラッド配線の銅配線膜を、Alを添加したCuAl配線膜とするものである。

(もっと読む)

不揮発性記憶装置

【課題】電源投入後、高速なセットアップが可能な不揮発性記憶装置を提供する。

【解決手段】不揮発性記憶装置は、データを不揮発的に記憶するメモリセルを有する第1および第2のメモリモジュール16−1、16−2と、第1および第2のメモリモジュールとそれぞれ接続されて、前記第1および第2のメモリモジュールを駆動するための外部電源を供給する第1および第2の外部電源線VL11、VL12とを備え、第1の外部電源線の電源容量C1は、前記第2の外部電源線の電源容量C2よりも小さい。

(もっと読む)

三端子型磁気抵抗効果素子

【課題】 三端子型磁気抵抗効果素子に関し、一次元線状巨大磁気抵抗素子の特性や磁壁の移動を外部から制御する。

【解決手段】 第1の強磁性体層と、前記第1の強磁性体層より保磁力の大きな第2の強磁性体層と、前記第1の強磁性体層と前記第2の強磁性体層との間に設けられた膜厚が単調に変化する非磁性体と、前記第1の強磁性体層上にゲート絶縁膜を介して設けられたゲート電極とを設ける。

(もっと読む)

磁気ランダムアクセスメモリ及びその初期化方法

【課題】下層のハード層の面内ばらつきに影響されず初期化可能なMRAMを提供する。

【解決手段】MRAMは、強磁性の磁気記録層10と、磁化が固定された強磁性の磁化固定層30と、磁気記録層10と磁化固定層30との間に設けられた非磁性のスペーサ層20と磁気記録層10の両端部の上部又は下部に設けられた導電層14a、14bとを具備する。磁気記録層10は、磁化が反転可能であり、スペーサ層20を介して磁化固定層30に接合される磁化反転領域13と、第1方向の磁化を有し、磁化反転領域13と平行に設けられた第1磁化領域11aと、第2方向の磁化を有し、磁化反転領域13と平行に設けられた第2磁化領域11bと、磁化反転領域13及び第1磁化領域11aと所定の傾斜角度φを成して結合する第1傾斜領域12aと、磁化反転領域13及び第2磁化領域11bと傾斜角度φを成して結合する第2傾斜領域12bとを備える。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】上面にストラップ配線が形成された絶縁膜と、この絶縁膜の下面に形成された配線と間で剥離が生じることが抑制された半導体装置および半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置は、半導体基板SSと、半導体基板SS上に形成され、周辺配線P1および配線L2が形成された配線層LL1,LL2と、配線層LL2に形成され、配線L3を含む配線層LL3と、配線層LL3上に形成され、磁気記憶素子MRを含む配線層LL4とを備え、配線L1,L2上に形成された拡散防止膜NF1,NF2は、SiCN膜またはSiC膜から形成され、配線L3上に形成された拡散防止膜NF3は、SiNから形成される。

(もっと読む)

電子回路基板、これを用いた磁気センサ、及び、電子回路の電源部の保護方法

【課題】TMR素子の故障時に発生しうる短絡事故を、有効に防止しうる小型で低コストな電子回路基板、これを用いた磁気センサ、及びTMR素子を含む電子回路の電源部の保護方法を提供する。

【解決手段】電子回路基板は、2つの端子s1,s2が、少なくともリードL11〜L15を介して、電源とグランドにそれぞれ接続されたTMR素子11〜14を含む。リードL11,L12の少なくとも一部は、TMR素子のトンネルバリア膜が破壊された後、2つの端子s1,s2間の短絡により発生する過電流によって断線する。これによると、TMR素子11〜14の故障により両端子s1,s2間が短絡した場合、電源とグランドが短絡されて過電流が発生する。その過電流によって、リードL11,L12の少なくとも一部が断線されるようにしており、これにより、過電流を遮断して電源を保護することができる。

(もっと読む)

半導体装置およびその検査方法

【課題】半導体基板上に形成された周辺回路上にさらに多層配線層が形成された構造の半導体装置において、周辺回路を構成する素子の特性を変化させずに周辺回路の不良解析を行うことができる半導体装置を提供する。

【解決手段】半導体基板11と、半導体基板11上に層間絶縁膜30を介して形成される多層配線構造を有する不揮発性メモリ層14と、半導体基板11上に形成され、不揮発性メモリ層14中のメモリセルを制御する回路を含む周辺回路12と、を備え、周辺回路12を構成する素子に接続され、周辺回路12の外部に引き出される配線35と、配線35の形成位置に対応する半導体基板11の上面から所定の深さまで設けられる拡散層27と、配線35と拡散層27との間を接続するコンタクト31と、を有する電極加工部15が、半導体基板11上の周辺回路12の形成領域R1以外の領域R2に形成される。

(もっと読む)

情報処理方法、積層型集積回路メモリ

【課題】メモリの単位メガバイト当たり製造コストを、単にモノリシック回路集積法で慣用的に製造される回路の数分の一に低減させる。

【解決手段】各層が別々に最適化されるように、別々の層(103)上へのメモリ回路(103)および制御論理回路(101)の物理的分離が可能な三次元(3DS)メモリ(100)。幾つかのメモリ回路(103)について1つの制御論理回路(101)で十分であり、コストを低減できる。3DSメモリ(100)の製造は、メモリ回路(103)を50μm以下の厚さに薄肉化する工程と、該メモリ回路を、ウェーハ基板形態のまま回路積層体に接合する工程とを有する。微粒子の高密度層間垂直バス相互接続部(105)が使用されている。3DSメモリ(100)製造方法は、幾つかの性能および物理的サイズ効率を可能にしかつ確立された半導体加工技術により実施される。

(もっと読む)

磁気トンネル接合に加えられる電流の方向を制御するためのシステムおよび方法

磁気トンネル接合に加えられる電流の方向を制御するためのシステムおよび方法が、開示される。ある特定の実施形態では、装置は、磁気トンネル接合(MTJ)記憶素子およびセンス増幅器を含む。センス増幅器は、第1の経路および第2の経路に結合される。第1の経路は、第1の電流方向選択トランジスタを含み、第2の経路は、第2の電流方向選択トランジスタを含む。第1の経路は、MTJ記憶素子のビット線に結合され、第2の経路は、MTJ記憶素子のソース線に結合される。  (もっと読む)

(もっと読む)

半導体パッケージ

【課題】磁気メモリ素子に記憶された情報を不正な手段で読み出すことを困難にして、磁気メモリ素子に記憶された情報が漏洩することを抑制できる半導体パッケージを提供すること。

【解決手段】磁気を加えることにより情報を記憶するメモリセル11を有するダイ10を内部に備える半導体パッケージ1であって、パッケージ本体20の内部に配置され、メモリセル11の磁気メモリ素子を磁化可能な磁界MF1を少なくともメモリセル11が位置する空間に発生させる磁界源41と、ダイ10の基板面10Aを覆って配置され、メモリセル11に加わる磁界MF1を減衰させる磁気シールド材42と、を備えることを特徴とする。

(もっと読む)

1 - 20 / 79

[ Back to top ]