Fターム[4M119DD35]の内容

MRAM・スピンメモリ技術 (17,699) | セル構成 (5,615) | 選択素子 (926) | FET (832) | MISFET (805) | TFT、SOI上のFET (11)

Fターム[4M119DD35]に分類される特許

1 - 11 / 11

メモリ装置

【課題】増加されたメモリ容量を具現できるメモリ装置を提供する。

【解決手段】メモリ装置は、水平な共通導電領域の上に配置され、前記共通導電領域に一端が電気的に連結され、互いに離隔水平な第1選択ラインの上で互いに平行に延長され前記水平な第1選択ラインと交差し前記垂直な半導体柱の側面に対向する側面を包含する水平な第1選択ラインと、前記水平な第1選択ラインと前記垂直な半導体柱との間に、そして前記水平な第2選択ラインと前記垂直な半導体柱との間に介在される少なくとも1つの誘電パターンを包含する選択構造体を含む。前記メモリ装置は、前記選択構造体の上に配置され前記垂直な半導体柱に電気的に連結されたメモリセルを含むメモリセルアレイをさらに含む。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】ビット当たりの単価を低減できる半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、第1方向に沿う第1部分(11a)と第2方向に沿いかつ第1部分と接続された第2部分(11b)とを有し、第2部分において半導体材料を含み、第1方向および第2方向からなる第1平面と交わる方向に沿って離れて並ぶ少なくとも2つの第1配線(11)を含む。可変抵抗膜(15)は、第1配線の第2部分に接続された第1面を有し、相違する抵抗値を示す複数の状態を取り得る。第2配線(12)は、可変抵抗膜の第1面と対向する第2面と接続されている。制御線(13)は、第1平面と交わる方向に沿い、少なくとも2つの第1配線の第2部分の半導体材料を含む部分と絶縁膜を介して接し、第1配線の第2部分の半導体材料を含む部分および絶縁膜とともにトランジスタを構成する。

(もっと読む)

トランジスタおよびメモリアレイ

【課題】大きな順方向−逆方向電流比を有するスイッチングデバイスを提供する。

【解決手段】トランジスタは、ソースと、ドレインと、ゲート領域と、ソースバリヤと、ドレインバリヤとを含む。ゲート領域は、ゲートと、アイランドと、ゲート酸化物とを含み、ゲート酸化物は、ゲートとアイランドとの間に配置される。ゲートおよびアイランドは、互いに、同時活性的に結合される。ソースバリヤはゲート領域からソースを分離し、ドレインバリヤはゲート領域からドレインを分離する。

(もっと読む)

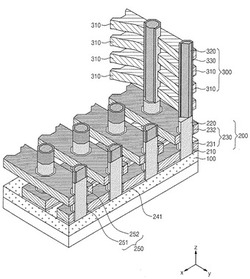

縦型トランジスタSTRAMアレイ

【課題】複数の不揮発性可変抵抗メモリセルを含む縦型のメモリアレイを提供する。

【解決手段】方法は、半導体ウェハから垂直に伸延する複数のピラー構造を有する半導体ウェハを提供するステップを含む。導電相互接続素子が、少なくとも選択された縦型ピラートランジスタ上に堆積されるとともに、不揮発性可変抵抗メモリセルが、導電相互接続素子上に堆積されて、縦型トランジスタメモリアレイを形成する。

(もっと読む)

不揮発性記憶装置およびその製造方法

【課題】不揮発性記憶装置およびその製造方法に関し、抵抗変化材料を利用したメモリの信頼性の向上を実現する。

【解決手段】積半導体素子を形成する基板の上方に、第1方向に延伸するように複数の金属配線層2を設け、金属配線層2のさら上方に、前記第1方向に直交する第2方向に延伸するように複数の金属配線層3を設ける。また、金属配線層2と金属配線層3とが交差する空間のそれぞれにメモリセルを設ける。前記メモリセルは、選択素子と相変化材料層7とが並列接続された構成とする。ここで、前記選択素子の前記第1方向の寸法が、相変化材料層7の前記第1方向の寸法よりも大きくなるように加工する。

(もっと読む)

アッド‐オン層形成方法

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、堆積可能なアッド‐オン層形成方法を提供することを目的とする。

【解決手段】堆積可能なアッド‐オン層形成方法であって、第一半導体基板の取り外し層の形成、取り外し層の上の第一半導体基板に多くのドーピング領域の形成、ここで多くのドーピング層の形成は、第一電導型を有するように、ドーピングされ、取り外し層の上の第一半導体基板の第一ドーピング層の形成、第一電導型に対する第二電導型を有するようにドーピングされ、第一ドーピング層の上の第一半導体基板に最低中間ドーピング層の形成、及び中間ドーピング層上の第一半導体基板に最低第三ドーピング層の形成からなり、第三ドーピング層上に第一の電導性ブランケット層の形成、第一電導ブランケット層上に第二の電導性ブランケット層の形成、及び第二電導性ブランケット層が第二半導体基板の対応する電導性上部層と接触するように、第一半導体基板を第二半導体基板への取り付け、からなる。

(もっと読む)

三次元的スタックド不揮発性メモリユニット

メモリユニット(200)であって、メモリユニットの第1の層において第1のトランジスタ領域に広がる第1のトランジスタ(210)と、メモリユニットの第2の層において第2のトランジスタ領域に広がる第2のトランジスタ(220)と、メモリユニットの第3の層において第1のメモリ領域に広がる第1の抵抗センスメモリ(RSM)セル(230)と、メモリユニットの第3の層において、第2のメモリ領域に広がる第2のRSMセル(250)とを含む。第1のトランジスタは第1のRSMセルに電気的に結合され、第2のトランジスタは第2のRSMセルに電気的に結合される。第2の層は第1の層と第3の層との間にある。第1のトランジスタおよび第2のトランジスタは、トランジスタ重畳領域を有する。第1のメモリ領域および第2のメモリ領域は、第1のトランジスタ領域および第2のトランジスタ領域を越えて延在しない。  (もっと読む)

(もっと読む)

磁気ランダムアクセスメモリ及びその製造方法

【課題】セル面積を縮小する。

【解決手段】磁気ランダムアクセスメモリは、側面と上面とを有する段差部が形成された半導体基板11と、段差部の側面上にゲート絶縁膜20を介して形成されたゲート電極Gと、段差部の上面内に形成されたドレイン拡散層24と、ドレイン拡散層より下方の半導体基板内にドレイン拡散層と離間して形成されたソース拡散層18と、ドレイン拡散層に接続され、磁化方向が固定された固定層31と磁化方向が反転可能な記録層33と固定層及び記録層の間に設けられた非磁性層32とを有し、固定層及び記録層の間に流す電流の向きに応じて固定層及び記録層の磁化方向が平行状態又は反平行状態となる磁気抵抗効果素子MTJと、磁気抵抗効果素子に接続されたビット線BLを具備する。

(もっと読む)

半導体記憶装置

【課題】より微細化が可能な半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、半導体基板21の上方に設けられ、かつ第1の方向に延在する第1乃至第3の配線と、半導体基板21に設けられ、かつ第1の方向に対して斜め方向に延在する複数の活性領域AAと、活性領域AAに設けられ、かつ第2の配線に電気的に接続されたソース領域25を共有する第1および第2の選択トランジスタ12と、一端が第1の選択トランジスタ12のドレイン領域26に電気的に接続され、他端が第1の配線に電気的に接続された第1の記憶素子11と、一端が第2の選択トランジスタ12のドレイン領域26に電気的に接続され、他端が第3の配線に電気的に接続された第2の記憶素子11とを含む。

(もっと読む)

大電流および大電流対称性を有する電流駆動メモリセル

磁気メモリを供給し使用する方法およびシステム。方法およびシステムは、複数の磁気記憶セルを設けることを含む。各磁気記憶セルは、磁気素子と磁気素子に接続される選択素子とを含む。磁気素子は、磁気素子を介して第1または第2の方向に駆動される書込電流によってプログラムされる。1つの態様では、方法およびシステムは、電圧源と磁気記憶セルおよび電圧源に接続される電圧ポンプとを設けることを含む。電圧源は供給電圧を供給する。電圧ポンプは、供給電圧より大きなバイアス電圧を選択素子に供給する。別の態様は、酸化物上シリコントランジスタを選択素子として設けることを含む。別の態様は、トランジスタがオフのとき第1の電圧、トランジスタがオンのとき第2の電圧であるボディバイアス電圧をトランジスタのボディに供給することを含む。 (もっと読む)

レーザ移動を用いて感熱基板上に移植した磁気ランダム・アクセス・メモリ(MRAM)デバイスおよびこれを製造する方法

【課題】 ポリマおよびプラスチック等の低温基板上に磁気メモリ・デバイスを製造する方法を提供する。

【解決手段】 低温基板上に磁気メモリ・デバイス(およびその結果として生じる構造)を形成する方法は、メモリ・デバイスを、分解可能な材料層で被覆された透明基板上に形成し、所定の高圧を生成させる急速加熱を施すステップと、メモリ・デバイスを低温基板に移動するステップと、を含む。

(もっと読む)

1 - 11 / 11

[ Back to top ]