Fターム[4M119DD37]の内容

MRAM・スピンメモリ技術 (17,699) | セル構成 (5,615) | 選択素子 (926) | ダイオード、サイリスタ、整流素子 (80)

Fターム[4M119DD37]に分類される特許

1 - 20 / 80

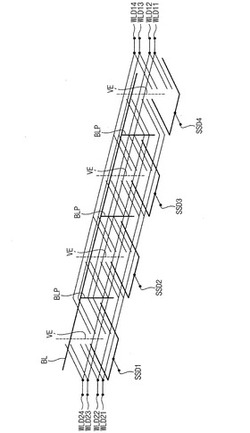

3次元半導体装置

【課題】増加された集積度を有し且つ高密度で高速の3次元(抵抗性)半導体(メモリ)装置を、最小限のマスク工程数で提供する。

【解決手段】チャンネル領域によって分離された第1及び第2不純物領域を含む基板、前記第1不純物領域に接続するビットライン、前記第2不純物領域に接続する垂直電極、前記基板と前記ビットラインとの間に配置される水平電極の積層体、及び、前記積層体と前記基板との間に配置される選択ラインを含む。この時,前記選択ラインは平面形状及び平面位置において、前記水平電極の各々と実質的に同一であり得る。

(もっと読む)

磁気抵抗効果素子、ダイオードおよびトランジスタを用いた磁気ランダムアクセスメモリ

【課題】高速動作を可能にする磁気メモリを提供する。

【解決手段】本実施形態の磁気メモリは、スピン注入書込みによって磁化の方向が不変の第1磁性層と、磁化の方向が可変の第2磁性層と、前記第1磁性層と前記第2磁性層との間に設けられたトンネル障壁層とを有する磁気抵抗効果素子と、前記磁気抵抗効果素子の前記第1および第2磁性層の一方の磁性層に電気的に接続された第1配線と、ソース/ドレインの一方が前記磁気抵抗素子の前記第1および第2磁性層の他方に電気的に接続された選択トランジスタと、前記選択トランジスタのソース/ドレインの他方に電気的に接続された第2配線と、前記磁気抵抗素子の前記第1および第2磁性層の他方に電気的に一端子が電気的に接続されたダイオードと、前記ダイオードの他の端子に電気的に接続された第3配線と、前記第3配線に電気的に接続されたセンスアンプと、を備えている。

(もっと読む)

磁気トンネリング接合装置、メモリ、メモリシステム及び電子装置

【課題】磁気トンネリング接合装置を具備する半導体メモリ装置、メモリ、メモリシステム及び電子装置が提供される。

【解決手段】磁気トンネリング接合装置が提供される。この装置は磁性膜を含む第1構造体と、少なくとも2つの外因性垂直磁化構造体を含み、前記外因性垂直磁化構造体の各々は磁性膜及び前記磁性膜上の垂直磁化誘導膜を含む、第2構造体と、前記第1及び第2構造体の間のトンネルバリアと、を包含できる。前記第2構造体は追加的な外因性垂直磁化構造体をさらに含み、その各々が磁性膜及び前記磁性膜上の垂直磁化誘導膜を含んでもよい。

(もっと読む)

磁気抵抗効果素子、およびその製造方法

【課題】CCP−CPP素子のMR変化率を向上させる。

【解決手段】磁化が実質的に一方向に固着された磁化固着層と、前記磁化固着層と対向するようにして形成され、磁化が外部磁界に対して変化する磁化自由層と、前記磁化固着層と前記磁化自由層との間に位置し、絶縁層、及びこの絶縁層を層方向に電流を通過させる導電体とを有する電流狭窄層を含むスペーサ層と具える磁気抵抗効果素子において、前記磁化固着層の層中、前記磁化自由層の層中、前記磁化固着層及び前記スペーサ層の界面、並びに前記磁化自由層及び前記スペーサ層の界面の少なくとも一か所に、Si、Mg、B、Alを含む機能層を設ける。

(もっと読む)

磁気抵抗効果素子、磁気ヘッドアセンブリ、磁気記録再生装置、メモリセルアレイ、及び磁気抵抗効果素子の製造方法

【課題】 本発明の実施形態によれば、劣化しにくく、MR変化率の大きい磁気抵抗効果素子、それを用いた磁気ヘッドアセンブリ、磁気記録再生装置、メモリセルアレイ、及び磁気抵抗効果素子の製造方法を提供することができる。

【解決手段】 磁気抵抗効果素子は、第1の電極と、第1の磁性層と、第2の磁性層と、スペーサ層と、Zn、In、Sn、及びCdから選択される少なくとも一つの元素とFe、Co、及びNiから選択される少なくとも一つの元素とを含む酸化物層と、酸化物層に接して設けられ、Zn、In、Sn、及びCdから選択される少なくとも一つの元素を0.5at%以上80at%以下の濃度で含み、かつFe、Co、及びNiから選択される少なくとも一つの元素を含む金属層とを備える。

(もっと読む)

磁気抵抗効果素子、磁気メモリ、磁気抵抗効果ヘッド、および磁気記録再生装置

【課題】MR変化率の向上が図れる磁気抵抗素子、磁気メモリ、磁気ヘッド、及び磁気記録再生装置を提供する。

【解決手段】磁化方向が実質的に一方向に固着された第1の磁性層と、外部磁界に応じて磁化方向が変化する第2の磁性層と、上記第1の磁性層と前記第2の磁性層との間に設けられたスペーサ層とを有し、上記第1の磁性層と前記第2の磁性層の少なくともいずれかは、式M1a M2bXc (5≦a≦68、10≦b≦73、22≦c≦85)で表される磁性化合物を有し、M1は、Co,Fe,Niから選択される少なくとも一種の元素、M2は、Ti,V,Cr,Mnから選択される少なくとも一種の元素、Xは、N,O,Cから選択される少なくとも一種の元素である。

(もっと読む)

薄膜磁性体記憶装置

【課題】高集積化に適したメモリセル配置、特に折り返し型ビット線構成に適したメモリセル配置を有する薄膜磁性体記憶装置を提供する。

【解決手段】メモリアレイにおいて、1個のメモリセルMCと対応する繰り返し単位140aが連続的に配置されて、メモリセルMCが行列状に配置される。隣接するメモリセル列間で、繰り返し単位140aは、1/2ピッチ(ハーフピッチ)分だけずらして配置される。ビット線BL1およびBL2は同一のビット線対を構成し、ビット線BL2はデータ読出時において、ビット線BL1の相補線/BL1として動作する。選択されたリードワード線RWLに対応して、1本おきのビット線にメモリセルが接続されるので、セルサイズを増加させることなく折返し型ビット線構成に基づくデータ読出に適したメモリセル配置を実行できる。

(もっと読む)

薄膜磁性体記憶装置

【課題】製造時ばらつきに対応して、データ読出時における高い信号マージンを確保可能な薄膜磁性体記憶装置を提供する。

【解決手段】ダミーメモリセルDCPは、2個のセルユニットCU0およびCU1を含む。各セルユニットCU0,CU1は、メモリセルと同様の構成を有し、ビット線BLと接地電圧Vssとの間に直列に結合された、トンネル磁気抵抗素子TMRおよびアクセストランジスタATRを有する。セルユニットCU0,CU1に対しては、異なる記憶データ“0”および“1”がそれぞれ書込まれる。データ読出時において、2個のセルユニットCU0,CU1が、読出参照電圧Vrefを伝達するためのビット線BLと接地電圧Vssとの間に並列に接続される。さらに、ダミーメモリセルDCPに対して、電流供給回路52からメモリセルに供給されるセンス電流Isの2倍、すなわち2・Isの一定電流が供給される。

(もっと読む)

不揮発性記憶装置およびその製造方法

【課題】不揮発性記憶装置およびその製造方法に関し、抵抗変化材料を利用したメモリの信頼性の向上を実現する。

【解決手段】積半導体素子を形成する基板の上方に、第1方向に延伸するように複数の金属配線層2を設け、金属配線層2のさら上方に、前記第1方向に直交する第2方向に延伸するように複数の金属配線層3を設ける。また、金属配線層2と金属配線層3とが交差する空間のそれぞれにメモリセルを設ける。前記メモリセルは、選択素子と相変化材料層7とが並列接続された構成とする。ここで、前記選択素子の前記第1方向の寸法が、相変化材料層7の前記第1方向の寸法よりも大きくなるように加工する。

(もっと読む)

磁気抵抗効果素子及び磁気ランダムアクセスメモリ

【課題】単一方向電流を用いて誤書き込みのない安定な書き込みを行う。

【解決手段】磁化が略垂直でかつ可変の第1強磁性層12と、磁化が略垂直でかつ不変の第2強磁性層16と、第1強磁性層と第2強磁性層との間の第1非磁性層14と、第2強磁性層に対して第1非磁性層と反対側に設けられ、膜面に略平行な磁化を有し、スピン偏極された電子の注入によりマイクロ波磁界を発生する第3強磁性層20と、第2強磁性層と第3強磁性層との間の第2非磁性層18と、を備え、第3強磁性層から第1強磁性層に向かう方向および第1強磁性層から第3強磁性層に向かう方向のうちの一方の方向に第1電流を流すことにより第3強磁性層から発生する第マイクロ波磁界によって第1強磁性層の磁化を反転し、一方の方向に第1電流と異なる電流密度を有する第2電流を流し第2強磁性層によってスピン偏極された電子によって第1強磁性層の磁化を異なる方向に反転する。

(もっと読む)

磁気抵抗効果素子、磁気抵抗効果ヘッド、磁気記憶装置、および磁気メモリ

【課題】スピントランスファートルクに起因するノイズの低減を図った磁気抵抗効果素子

、磁気抵抗効果ヘッド、磁気記憶装置、および磁気メモリを提供する。

【解決手段】磁化固着層、非磁性層、磁化自由層を有する磁気抵抗効果素子の磁化固着層

、または磁化自由層内にZr,Nb,Mo,Ru,Rh,Pd,Ag,La,Hf,Ta

,W,Re,Os,Ir,Pt,Auのいずれかを含む層を配置する。

(もっと読む)

抵抗変化メモリ

【課題】高い抵抗値の抵抗素子を実現する。

【解決手段】本実施形態の抵抗変化メモリは、第1の配線レベルILV1に位置し、第1の方向に延びる制御線L1と、第2の配線レベルILV2に位置し、第2の方向に延びる制御線L2と、制御線L1と制御線L2との間に設けられるセルユニットCUとを含むメモリセルアレイを有し、複数の配線レベルに設けられる少なくとも2つの抵抗線RL3A,RL5と、抵抗線RL3A,RL5間に設けられ、セルユニットCUの構成部材又はコンタクトプラグZCの構成部材と同じ構成部材を含む抵抗体91と、を有し、抵抗素子領域17内に設けられる抵抗素子90を含んでいる。

(もっと読む)

半導体装置

【課題】コンタクト電極と配線とを安定して接続する。

【解決手段】実施形態の半導体装置は、平面形状がリング状の第1のコンタクト部41を有する第1の配線40と、第1の配線40より下層に設けられる第2の配線50と、コンタクト部41のリング状の部分を貫通して、2つの配線40,50を電気的に接続するコンタクト電極60とを含み、基板11上に設けられる配線領域を具備する。

(もっと読む)

抵抗変化メモリ

【課題】非オーミック素子の厚さを薄くする。

【解決手段】本発明の例に係わる抵抗変化メモリは、第1方向に延びる第1の配線と、第2方向に延びる第2の配線と、第1の配線と第2の配線との交点に設けられ、抵抗状態の変化に応じてデータを記憶するメモリ素子20と非オーミック素子30とが直列接続されたセルユニットセルユニットCUと、を具備し、非オーミック素子30Aは、メタル層31と、第1の半導体層33と、半導体層33とメタル層31との間に設けられ、第1のメタル層31との界面に偏在層38bを有する第2の半導体層38とを含む。

(もっと読む)

不揮発性半導体メモリ及びその製造方法

【課題】不揮発性半導体メモリのリーク電流を削減する。

【解決手段】本発明の一態様に係る不揮発性半導体メモリ1は、複数のワード線WL0〜WLnと、複数のワード線WL0〜WLnと交差する複数のビット線BL0〜BLmと、複数のワード線WL0〜WLnと複数のビット線BL0〜BLmとの交差部のそれぞれに対して備えられており、第1のダイオード5aと抵抗変化型記憶素子5bとを含む複数のメモリセル5と、複数のビット線BL0〜BLmと交差するダミーワード線DWLと、複数のワード線WL0〜WLnと交差するダミービット線DBLと、ダミーワード線DWLと複数のビット線BL0〜BLmとの交差部、及び、ダミービット線DBLと複数のワード線WL0〜WLnとの交差部のそれぞれに対して備えられており、それぞれが第2のダイオード6aを含む複数のダミーセル6とを具備する。

(もっと読む)

磁気抵抗効果素子、磁気ヘッドアセンブリ、及び磁気記録再生装置

【課題】 大きなMR変化率を有する磁気抵抗効果素子、磁気ヘッドアセンブリ、及び磁気記録再生装置を提供する。

【解決手段】 磁化固着層5と、磁化自由層7と、磁化固着層5と磁化自由層7との間に設けられた非磁性層6と、磁化自由層7の非磁性層6が設けられた側とは反対の側に設けられたAuを含む第1の金属層4と、第1の金属層4の磁化自由層7が設けられた側とは反対の側に設けられたCuNi合金を含む第2の金属層3と第2の金属層3の第1の金属層4が設けられた側とは反対の側に設けられた第1の電極2と、磁化固着層5の非磁性層6が設けられた側とは反対の側に設けられた第2の電極8とを備え、磁化固着層5及び磁化自由層7の一方がハーフメタルを含み、第1の電極2から第2の電極8に向かって電流が流れることを特徴とする。

(もっと読む)

抵抗変化メモリ

【課題】抵抗変化メモリに用いられる素子特性の劣化を抑制できる。

【解決手段】本発明の例に関わる抵抗変化メモリは、n型伝導性の第1のシリコン層と第1のシリコン層と接触する導電層36とを有する非オーミック素子30と、導電層36を介して非オーミック素子30に接続され、抵抗状態の可逆的な変化に応じてデータを記憶するメモリ素子と、を含み、配線L2(i)と配線L3(j)との間に設けられるセルユニットと、を具備し、シリコン層33は、ドナー不純物として、第1の元素41と第2の元素42とを含む。

(もっと読む)

抵抗変化メモリ

【課題】抵抗変化メモリに用いられる素子特性の劣化を抑制できる。

【解決手段】本発明の例に関わる抵抗変化メモリは、2つの配線L2(i),L3(j)と、少なくとも一方の端部に設けられる導電層36と2つの端部間に設けられるシリコン部とを有する非オーミック素子30と、導電層36を介して非オーミック素子30に接続され、抵抗状態の可逆的な変化に応じてデータを記憶するメモリ素子20とを含み、2つの配線L2(i),L3(j)間に設けられるセルユニットCUと、を具備し、非オーミック素子30は、シリコン部37内に、シリコンゲルマニウム領域39を有している。

(もっと読む)

抵抗変化メモリ及びその製造方法

【課題】抵抗変化メモリに用いられる素子特性の劣化を抑制できる。

【解決手段】本発明の例に関わる抵抗変化メモリは、配線60と配線65との交点に設けられ、第1及び第2の端部の少なくとも一方にシリサイド層39を有する非オーミック素子30と抵抗状態の可逆的な変化に応じてデータを記憶するメモリ素子20とを含むセルユニットCUを具備し、シリサイド層39は、Si元素50とシリサイドを形成する少なくとも1種類の3d遷移金属元素51と、3d遷移金属元素51の原子半径r1より大きい原子半径r2を有する少なくとも1種類の添加元素52とを含む。

(もっと読む)

薄膜磁性体記憶装置

【課題】磁気トンネル接合部(MTJ)を有するメモリセルを用いてデータ記憶を行なう薄膜磁性体記憶装置において、データ読出動作を高速化する。

【解決手段】MTJメモリセルに対しては、データ書込およびデータ読出にそれぞれ用いられるライトワード線WWLおよびリードワード線RWLが独立して設けられる。メモリアレイ10を列方向に分割して形成される領域AR1,AR2ごとにリードワード線RWLを分割配置することによって、リードワード線RWLにおける信号伝搬遅延を低減して、データ読出動作を高速化できる。各リードワード線RWLの活性化は、行選択結果に応じてライトワード線WWLと階層的に制御される。ワード線電流制御回路40は、データ書込時およびデータ読出時のそれぞれに対応して、ライトワード線WWLにおける電流経路を形成および遮断する。

(もっと読む)

1 - 20 / 80

[ Back to top ]