Fターム[4M119EE35]の内容

MRAM・スピンメモリ技術 (17,699) | 配線構成 (2,374) | 配線の共用化 (32)

Fターム[4M119EE35]に分類される特許

1 - 20 / 32

3次元半導体装置

【課題】増加された集積度を有し且つ高密度で高速の3次元(抵抗性)半導体(メモリ)装置を、最小限のマスク工程数で提供する。

【解決手段】チャンネル領域によって分離された第1及び第2不純物領域を含む基板、前記第1不純物領域に接続するビットライン、前記第2不純物領域に接続する垂直電極、前記基板と前記ビットラインとの間に配置される水平電極の積層体、及び、前記積層体と前記基板との間に配置される選択ラインを含む。この時,前記選択ラインは平面形状及び平面位置において、前記水平電極の各々と実質的に同一であり得る。

(もっと読む)

半導体装置及び磁気ランダムアクセスメモリ

【課題】磁壁移動型MRAMのメモリセルの面積を低減する。

【解決手段】メモリセル200−1が、固定層11と磁気記録層21とリファレンス層41とトンネルバリア膜31とMOSトランジスタ51とを備えており、メモリセル200−2が、固定層13と磁気記録層22とリファレンス層42とトンネルバリア膜32とMOSトランジスタ52とを備えている。固定層11、13は、第1方向に固定された磁化を有している。第1方向と反対の第2方向に固定された磁化を有する固定層12が磁気記録層21、22に接合されている。固定層12と共通ビット線CBLとが、それらの間の電気的接続が分離不能であるように接続される。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】製造コストの増加を抑えつつ、直列に接続されたMTJ素子を所望の特性の抵抗体として機能させることが可能な半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、磁化方向に応じて抵抗値が変化可能な複数の記憶用MTJ素子が、半導体基板上に配置されたメモリセルアレイ領域を備える。半導体記憶装置は、複数の抵抗用MTJ素子が、前記半導体基板上に第1の方向および前記第1の方向に垂直な第2の方向に沿って配置された抵抗素子領域を備える。前記半導体基板の上面に平行な前記抵抗用MTJ素子の第1の断面の面積は、前記半導体基板の前記上面に平行な前記記憶用MTJ素子の第2の断面の面積よりも、大きい。

(もっと読む)

半導体記憶装置

【課題】上部電極と第2のビット線との間のビアコンタクトの劣化を抑制し、信頼性の高い半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、半導体基板上に配置された複数の磁気トンネル接合素子と、複数の磁気トンネル接合素子の一端に電気的に接続された複数の選択トランジスタとを備える。第1のビット線が、各磁気トンネル接合素子の一端に1つまたは複数の選択トランジスタを介して接続されている。複数の上部電極は、複数の磁気トンネル接合素子の他端に接続されえいる。第2のビット線は、各磁気トンネル接合素子の他端に上部電極を介して接続されている。上部電極は、第2のビット線に沿って延伸しており第2のビット線の延伸方向に配列された複数の磁気トンネル接合素子の各他端に共通に接続されている。

(もっと読む)

不揮発性記憶装置およびその製造方法

【課題】不揮発性記憶装置およびその製造方法に関し、抵抗変化材料を利用したメモリの信頼性の向上を実現する。

【解決手段】積半導体素子を形成する基板の上方に、第1方向に延伸するように複数の金属配線層2を設け、金属配線層2のさら上方に、前記第1方向に直交する第2方向に延伸するように複数の金属配線層3を設ける。また、金属配線層2と金属配線層3とが交差する空間のそれぞれにメモリセルを設ける。前記メモリセルは、選択素子と相変化材料層7とが並列接続された構成とする。ここで、前記選択素子の前記第1方向の寸法が、相変化材料層7の前記第1方向の寸法よりも大きくなるように加工する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】MRAMにおいては、書き込み電流の低減やディスターブ回避を目的に、書き込みに使用する配線を強磁性体膜で覆うクラッド配線構造がよく用いられている。また、高信頼性製品の信頼性確保のためCu配線中に微量のAlを添加するCuAl配線が広く使用されている。MRAMも高信頼性製品に搭載される可能性が高く、信頼性は重要である。しかし、クラッド配線は、もともと配線抵抗が高いCuAl配線の配線抵抗を更に上昇させるというデメリットがあるため、両方の技術を同時に使用すると配線抵抗のスペックを満たさなくなる可能性が高い。

【解決手段】本願発明は、多層銅埋め込み配線を有する半導体装置において、MRAMメモリセルマトリクス領域を構成する複数の銅埋め込みクラッド配線の銅配線膜を比較的純粋な銅で構成し、これらの配線層よりも下層の銅埋め込み非クラッド配線の銅配線膜を、Alを添加したCuAl配線膜とするものである。

(もっと読む)

抵抗変化型半導体メモリ

【課題】セル面積の縮小及び動作特性の向上に優れたレイアウトを提案する。

【解決手段】実施形態によれば、抵抗変化型半導体メモリは、第1方向に並ぶ第1乃至第4メモリセルを備える。第1乃至第4メモリセルの各々は、第1ソース/ドレインが第1方向に延びる第1ビット線BLA1に接続され、ゲートが第2方向に延びるワード線WL1, WL2, WL3, WL4に接続されるセルトランジスタT11, T12, T13, T14と、一端がセルトランジスタT11, T12, T13, T14の第2ソース/ドレインに接続され、他端が第2方向に延びる第2ビット線BLB1, BLB2, BLB3, BLB4に接続される抵抗性記憶素子M11, M12, M13, M14とを有する。第1及び第2メモリセル内の第1ソース/ドレインは、共有化され、第3及び第4メモリセル内の第1ソース/ドレインは、共有化される。

(もっと読む)

不揮発性記憶装置

【課題】消費電力を低減することができるプレート方式の不揮発性記憶装置を提供する。

【解決手段】複数のメモリセルをそれぞれ有する複数のメモリマットと、メモリマット毎に設けられ、複数のメモリセルに電圧を与える複数のプレート電極と、複数のプレート電極に電圧を与える電源部と、電源部とプレート電極との間、及びプレート電極間にそれぞれ設けられた複数のスイッチを有するスイッチ回路と、スイッチ回路を制御して、電源部とプレート電極の間を非接続とすると共にプレート電極間を接続して、プレート電極間で電荷の充放電を行う制御部と、を備えた不揮発性記憶装置とした。

(もっと読む)

情報記憶素子及びその駆動方法

【課題】高い記録密度を実現することができる情報記憶素子を提供する。

【解決手段】連続して形成された導電性の第1の磁性体を含むワード電極1と、第1の磁性体に接して形成された非磁性膜と、第1の磁性体に対して、非磁性膜5を介して接続された第2の磁性体とを含む。そして、ワード電極1の両端部に配置され、ワード電極1の端部の磁化の方向を設定するための磁化設定機構2と、第2の磁性体の保磁力を低減させるための保磁力低減機構と、ワード電極1と交差するように連続して形成された導電性のビット電極3を含む情報記憶素子を構成する。ワード電極1は、第1の磁性体を兼ねていてもよい。ビット電極3は、保磁力低減機構や第2の磁性体を兼ねていてもよい。

(もっと読む)

半導体記憶装置

【課題】2つの選択トランジスタと1つの抵抗性記憶素子から成るメモリセルのレイアウト面積を縮小する。

【解決手段】半導体記憶装置は、それぞれが第1および第2のビット線から成り、且つカラム方向に延びる複数のビット線対と、各ビット線対に接続され、且つ複数のメモリセルから成るメモリセル群とを含む。各メモリセルは、第1のトランジスタT1、第2のトランジスタT2および抵抗性記憶素子10から成る。ロウ方向に隣接する2つのビット線対は、第1のビット線同士が共通接続され、もしくは第2のビット線同士が共通接続されて第1のカラムユニットを構成する。少なくとも片側の端部に配置される第1のビット線もしくは第2のビット線は、それと下層との接続部分よりも、第1のカラムユニットの中央寄りに配置される。

(もっと読む)

半導体集積回路

【課題】リードワード線およびライトワード線のドライブ回路を分割配置してレイアウト面線を減少させる。

【解決手段】

磁性体メモリセルMCは、メモリアレイに行列状に配置される。リードワード線RWL1〜RWLnおよびライトビット線WBL1〜WBLnは、磁性体メモリセルの行に対応して配置される。ライトワード線WWL1〜WWLmおよびリードビット線RBL1〜RBLmは、磁性体メモリセルの列に対応して配置される。この結果、リードワード線ドライバ30rおよびリードワード線ドライバ30wは、メモリアレイに対して異なる方向に隣接するように分割配置することができる。

(もっと読む)

磁気ランダムアクセスメモリを製造するシステムおよび方法

磁気ランダムアクセスメモリを製造するシステムおよび方法が開示される。特定の一実施形態では、磁気トンネル接合メモリシステムを作製する方法は、金属層の一部分を、ほぼ直線の部分を有する無分岐のソースラインの中に形成するステップを含む。この方法はまた、ソースラインをほぼ直線の部分で、第1のビアを使用して第1のトランジスタに結合するステップを含む。第1のトランジスタは、ソースラインから受け取った第1の電流を第1の磁気トンネル接合デバイスに供給するように構成される。この方法は、ソースラインを、第2のビアを使用して第2のトランジスタに結合するステップを含み、第2のトランジスタは、ソースラインから受け取った第2の電流を第2の磁気トンネル接合デバイスに供給するように構成される。  (もっと読む)

(もっと読む)

薄膜磁性体記憶装置

【課題】磁気トンネル接合部(MTJ)を有するメモリセルを用いてデータ記憶を行なう薄膜磁性体記憶装置において、データ読出動作を高速化する。

【解決手段】MTJメモリセルに対しては、データ書込およびデータ読出にそれぞれ用いられるライトワード線WWLおよびリードワード線RWLが独立して設けられる。メモリアレイ10を列方向に分割して形成される領域AR1,AR2ごとにリードワード線RWLを分割配置することによって、リードワード線RWLにおける信号伝搬遅延を低減して、データ読出動作を高速化できる。各リードワード線RWLの活性化は、行選択結果に応じてライトワード線WWLと階層的に制御される。ワード線電流制御回路40は、データ書込時およびデータ読出時のそれぞれに対応して、ライトワード線WWLにおける電流経路を形成および遮断する。

(もっと読む)

半導体装置

【課題】MTJメモリセルを有するMRAMデバイスにおいて、データ読出動作の高速化および、配線層数の減少による製造コスト低減を図る。

【解決手段】MTJメモリセルは、記憶データのデータレベルに応じて抵抗値が変化する磁気トンネル接合部MTJと、アクセストランジスタATRとを備える。アクセストランジスタATRのゲートはリードワード線RWLと結合される。ビット線BLは、磁気トンネル接合部MTJと直接結合されず、アクセストランジスタATRを介して磁気トンネル接合部MTJと電気的に結合される。磁気トンネル接合部MTJは、ライトワード線WWLおよびアクセストランジスタATRの間に結合される。データ読出時において、ライトワード線WWLの電圧は接地電圧Vssに設定されて、データ読出のための電流経路が形成される。さらに、ライトワード線WWLは、ビット線BLよりも上層側に形成される。

(もっと読む)

三次元的スタックド不揮発性メモリユニット

メモリユニット(200)であって、メモリユニットの第1の層において第1のトランジスタ領域に広がる第1のトランジスタ(210)と、メモリユニットの第2の層において第2のトランジスタ領域に広がる第2のトランジスタ(220)と、メモリユニットの第3の層において第1のメモリ領域に広がる第1の抵抗センスメモリ(RSM)セル(230)と、メモリユニットの第3の層において、第2のメモリ領域に広がる第2のRSMセル(250)とを含む。第1のトランジスタは第1のRSMセルに電気的に結合され、第2のトランジスタは第2のRSMセルに電気的に結合される。第2の層は第1の層と第3の層との間にある。第1のトランジスタおよび第2のトランジスタは、トランジスタ重畳領域を有する。第1のメモリ領域および第2のメモリ領域は、第1のトランジスタ領域および第2のトランジスタ領域を越えて延在しない。  (もっと読む)

(もっと読む)

半導体記憶装置及びその製造方法

【課題】可変抵抗素子の特性バラツキを低減することで、動作マージンを大きくすることが可能な半導体記憶装置及びその製造方法を提供する。

【解決手段】半導体記憶装置は、メモリ領域に配置され、かつ抵抗値の変化に応じてデータを記憶し、かつ第1の配線SLに一端が電気的に接続され、第2の配線に他端が電気的に接続された複数の可変抵抗素子23と、メモリ領域に配置され、かつ可変抵抗素子23と同じ材料からなり、かつ電気的に絶縁された複数のダミー素子28とを含む。MTJ素子23及びダミー素子28を合わせた素子アレイは、格子状の密集パターンを有している。すなわち、MTJ積層膜を加工する際のレジストパターンを格子状の密集パターンによって形成する。そして、このレジストパターンを用いてMTJ積層膜を加工することで、MTJ素子23とダミー素子28とを合わせた素子アレイを格子状の密集パターンに配置する。

(もっと読む)

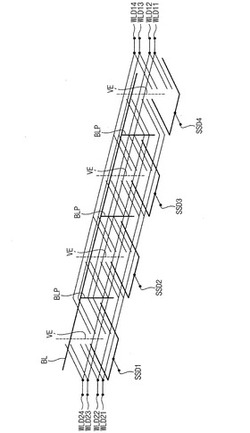

不揮発性半導体記憶装置、及びその製造方法

【課題】コストを抑えた不揮発性半導体記憶装置、及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、ビット線BL0i〜BL2i、ビット線BL0i〜BL2iと交差するワード線WL0i、WL1i、及びビット線BL0i〜BL2i及びワード線WL0i、WL1iの交差部で両配線間に接続されたメモリセルMC0〜MC3を有する単位セルアレイMAT00を備える。さらに、不揮発性半導体記憶装置は、第1位置に設けられたビット線BL0iの側部に接し、第1位置よりも上方の第2位置に設けられたビット線BL1iまで積層方向に延びるコンタクトプラグCL1〜CL3と、第1位置と第2位置の間の第3位置に設けられたワード線WL0iの側部に接し、第2位置よりも上方の第4位置に設けられたワード線WL1iまで積層方向に延びるコンタクトプラグCL5、CL6とを備える。

(もっと読む)

三値連想磁気抵抗ランダムアクセスメモリセル

【課題】磁気ランダムアクセスメモリ(MRAM)に基づいた三値連想メモリ(TCAM)に書き込んで検索する方法を提供する。

【解決手段】三値連想メモリセル1は、ストレージ層23から形成されている第1磁気トンネル接合2、ストレージ層の磁化に対して調整可能な磁化方向を有するセンス層21、及び、ストレージ層とセンス層との間の絶縁層22を有し、ストレージ層に接続されているセンス線3を有し、第1フィールド線4及び第2フィールド線5を有する。第1フィールド線は、第2フィールド線に対して直交し、第2フィールド線を介してストレージ層に対して第1書込みデータを提供して、高い論理状態又は低い論理状態を有する第1記憶データを記憶する。第1フィールド線を介してストレージ層に対して第1書込みデータを提供して、マスクされた論理状態を有する第1記憶データを記憶する。

(もっと読む)

半導体記憶装置

【課題】メモリセルの面積を縮小しつつ、メモリセルの寄生抵抗を低減する。

【解決手段】半導体記憶装置は、半導体基板30の上方の同一レベル層に設けられたビット線BL,/BLと、ビット線BLの下方に設けられかつ直列に接続された第1の抵抗変化素子10及び第1のMOSFET20と、ビット線/BLの下方に設けられかつ直列に接続された第2の抵抗変化素子10及び第2のMOSFET20とを含む。さらに、第1の抵抗変化素子10の一端及び第2のMOSFET20の一端とビット線BLとを電気的に接続する第1の配線層35と、第2の抵抗変化素子10の一端及び第1のMOSFET20の一端とビット線/BLとを電気的に接続する第2の配線層35とを含む。

(もっと読む)

記憶装置

【課題】スピン注入メモリ等の抵抗変化素子を用いた記憶装置において、抵抗変化素子の高集積化を可能とした記憶装置を提供する。

【解決手段】供給される電流の向きにより抵抗値が変化する複数の抵抗変化素子と、各抵抗変化素子への電流供給をオン−オフ制御する複数のアクセス用トランジスタと、複数の抵抗変化素子の一方端に接続したビット線と、複数の抵抗変化素子の他方端にそれぞれアクセス用トランジスタを介して接続したソース線と、各アクセス用トランジスタのゲートにそれぞれ接続した複数のワード線と、接地電位が印加されるグランド線と、オン状態となることによりビット線またはソース線とグランド線とを接続するスイッチ用トランジスタとを備えた記憶装置とし、抵抗変化素子へ電流供給する際に、スイッチ用トランジスタをオン状態にして、ビット線またはソース線を接地電位にする。

(もっと読む)

1 - 20 / 32

[ Back to top ]