Fターム[4M119FF04]の内容

MRAM・スピンメモリ技術 (17,699) | コンタクト (2,004) | コンタクトの形状又は作成方法 (789) | コンタクト下地層、バリア層を有するもの (50)

Fターム[4M119FF04]に分類される特許

1 - 20 / 50

半導体装置及びその製造方法

【課題】配線コーナーでの電子散乱を減らし、配線の抵抗率の増大を抑制する。

【解決手段】実施形態によれば、半導体装置は、半導体基板と、前記半導体基板上に形成され、配線溝を有する層間絶縁膜とを備える。さらに、前記装置は、前記配線溝内に形成された配線を備える。さらに、前記配線溝の底面と側面との間の角部の曲率半径は、前記配線の配線幅の1/10以上である。

(もっと読む)

半導体装置の製造方法

【課題】TATの短縮及び製造コストの低下を図る。

【解決手段】実施形態に係わる半導体装置の製造方法は、下地層上にピラーを形成する工程と、GCIB法を用いて、下地層上に、ピラーを覆い、かつ、上面の最も低い部分がピラーの上面よりも下にある絶縁層を形成する工程と、CMP法を用いて、絶縁層及びピラーを、絶縁層の上面の最も低い部分まで研磨する工程とを備える。

(もっと読む)

半導体装置、電子装置、配線基板、半導体装置の製造方法、及び配線基板の製造方法

【課題】配線基板に半導体素子を形成する場合において、配線基板の製造工程数を少なくする。

【解決手段】コア層200の一面上には、第1配線232が設けられている。第1配線232上、及びその周囲に位置するコア層200の一面上には、半導体層236が形成されている。第1配線232及び半導体層236は、半導体素子を形成している。本実施形態において半導体素子は、第1配線232をゲート電極としたトランジスタ230であり、半導体層236と第1配線232の間に、ゲート絶縁膜234を有している。

(もっと読む)

半導体記憶装置

【課題】記憶素子に充分な電流を流すことができるようにセルトランジスタの電流駆動能力を充分に確保しつつ、ユニットセルのレイアウト面積が従来よりも小さい半導体記憶装置を提供する。

【解決手段】本実施形態による半導体記憶装置は、半導体基板と、半導体基板に形成されたアクティブエリアを備える。複数のセルトランジスタがアクティブエリアに形成されている。第1のビット線および第2のビット線は、互いに対をなす。複数のワード線は第1および第2のビット線と交差する。複数の記憶素子の一端がセルトランジスタのソースまたはドレインに電気的に接続され、他端が第1または第2のビット線に接続されている。第1および第2のビット線は、両方とも同一のアクティブエリアに対して記憶素子を介して接続されている。

(もっと読む)

磁気メモリデバイスの駆動方法及び磁気メモリデバイス

【課題】基準素子におけるディスターバンスの発生を防止することができる磁気メモリデバイスを提供する。

【解決手段】基準セル28が、基準素子20を含む。基準素子は、固定磁化層21、絶縁層22、自由磁化層23を含み、自由磁化層の磁化方向は固定磁化層の磁化方向と反平行であり、メモリセル18の磁気抵抗素子10が平行状態のときの抵抗値と反平行状態のときの抵抗値との間の抵抗値を有する。基準素子に、基準素子の固定磁化層から自由磁化層に向かう読出電流を流し、磁気抵抗素子の抵抗値と、基準素子の抵抗値との大小関係に依存する物理量を検出することにより、情報の読出しを行う。

(もっと読む)

磁気抵抗素子及び磁気記憶装置

【課題】高い熱揺らぎ耐性を確保しつつ、スイッチング電流を低減するも、記憶保持特性を向上させ、更なる高速動作化及び高集積化を可能する信頼性の高い磁気抵抗素子及び磁気記憶装置を提供する。

【解決手段】反強磁性層51及び積層フェリー固定層50と、トンネルバリア層2と、非磁性層4を間に挟持した第1の磁性層3と第2の磁性層5とを有する積層磁化自由層11とを有してMTJ10が構成されており、MTJ10は、その周縁において、当該MTJ10の面内磁化容易軸の方向と垂直となる方向に一対の溝10a,10bが形成されている。

(もっと読む)

磁気記憶装置の製造方法および磁気記憶装置

【課題】TMR素子間の特性のばらつきを低減でき、かつ製造歩留まりの高い不揮発性磁気メモリの製造方法およびその構造を提供する。

【解決手段】TMR素子を含む磁気記憶装置の製造方法が、配線層が設けられた層間絶縁膜の上に、絶縁膜を形成する工程と、絶縁膜に、配線層が露出するように開口部を形成する開口工程と、開口部を埋めるように、絶縁膜上に金属層を形成する金属層形成工程と、CMP法を用いて絶縁膜上の金属層を研磨除去し、開口部内に残った金属層を下部電極とするCMP工程と、下部電極上にTMR素子を形成する工程とを含む。

(もっと読む)

磁気記憶素子および磁気記憶装置

【課題】半選択状態になった磁気記憶素子のデータの誤反転を抑制することにより信頼性の高い書き込み動作を行うことができる磁気記憶素子、およびこれを用いた磁気記憶装置を提供する。

【解決手段】磁化容易軸91と磁化困難軸92とを有する記録層3は、平面視においてすべての領域が第1導電層WTまたは第2導電層BLの少なくとも一方と重なる。磁化容易軸91に沿い、記録層3と平面視において重なる寸法が最大となる第1の線分の第1の端点TP,BPは、第2導電層BLと平面視において重ならない。上記第1の線分の中点を通り、平面視において第1の線分に直交し、記録層3と平面視において重なる第2の線分の1対の端点である第2の端点LP,RPのうち少なくとも一方は、第1導電層WTと平面視において重ならない。

(もっと読む)

磁気メモリ及びその製造方法

【課題】磁気抵抗素子間での電気的特性のバラツキを低減する。

【解決手段】磁気メモリの製造方法は、半導体基板20上のセルアレイ部に磁気抵抗素子37を形成する工程と、半導体基板20上の周辺回路部に、磁気抵抗素子37と同じ積層構造を有しかつ磁気抵抗素子37と同じレベルに配置されたダミー素子68を形成する工程と、磁気抵抗素子37及びダミー素子68を一括して平坦化する工程と、ダミー素子68にレーザー光線を照射し、ダミー素子68を非磁性体化する工程と、平坦化された磁気抵抗素子37上に上部電極41を形成する工程とを含む。

(もっと読む)

磁気ランダムアクセスメモリ及びその製造方法

【課題】 配線の信頼性が劣化しない磁気ランダムアクセスメモリ及びその製造方法を提供することである。

【解決手段】 実施形態に係る磁気ランダムアクセスメモリは、下部電極、磁気抵抗効果素子、上部電極が下層から順に積層された積層膜が設けられる。前記磁気抵抗効果素子、前記上部電極の側面に接し、上面が前記上部電極の上面と実質的に同一の高さであるストッパ層平坦部が設けられる。前記上部電極上にバリアメタル膜が設けられる。前記バリアメタル膜上にコンタクトプラグが設けられる。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】 メモリセルの微細化を図りつつ、セル電流を確保する。

【解決手段】 実施形態による半導体記憶装置は、ゲート溝15と第1乃至第3の溝19a、19b、18とを有し、第1乃至第3の溝はゲート溝の底面に形成され、第3の溝は第1及び第2の溝の間に形成された半導体基板11と、第1の溝内形成された第1のゲート部21aと第2の溝内形成された第2のゲート部21bと第3の溝内形成された第3のゲート部21cとゲート溝内に形成された第4のゲート部21dとを有するゲート電極21と、を具備する。ゲート電極を有するセルトランジスタTrは、第1及び第3のゲート部間の半導体基板内に形成された第1のチャネル領域Ch1と、第2及び第3のゲート部間の半導体基板内に形成された第2のチャネル領域Ch2と、を有する。

(もっと読む)

磁気ランダムアクセスメモリ

【課題】書き込み電流を低減する磁気ランダムアクセスメモリを提供する。

【解決手段】磁気ランダムアクセスメモリは、半導体基板と、半導体基板の上方に配置され、垂直磁化膜で形成されたMTJ素子10と、MTJ素子10の上側に配置されかつ半導体基板に対して引っ張る方向に応力を加える引っ張り応力膜21及びMTJ素子10の下側に配置されかつ半導体基板に対して圧縮する方向に応力を加える圧縮応力膜の少なくとも一方を有する応力膜と、を具備する。

(もっと読む)

磁気トンネル接合素子及び磁気ランダムアクセスメモリ

【課題】 GMR素子では、十分大きなMR比を得ることが困難である。大きなMR比を実現することが可能なMTJ素子において、反転電流を低減させることが望まれている。

【解決手段】 下部電極の上に、磁化容易方向が厚さ方向を向く垂直磁気異方性膜が形成されている。垂直磁気異方性膜の上に、非磁性材料で形成されたスペーサ層が配置されている。スペーサ層の上に、アモルファスの導電材料からなる下地層が配置されている。下地層の上に、磁化容易方向が面内方向を向く磁化自由層が配置されている。磁化自由層の上にトンネルバリア層が配置されている。トンネルバリア層の上に、磁化方向が面内方向に固定された磁化固定層が配置されている。スペーサ層は、垂直磁気異方性膜と磁化自由層との間に交換相互作用が働かない厚さであり、かつスピン緩和長よりも薄い。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】孤立パターンに銅の化合物が析出するのを抑制する半導体装置の製造方法と、半導体装置とを提供する。

【解決手段】半導体装置では、素子・基板層ESLの低誘電率膜LOW1、ファイン層FLの極低誘電率膜ELK1等およびセミグローバル層SGLの低誘電率膜LOW2等のそれぞれの開口部に形成されるアライメントマークAMおよび重ね合わせ検査マークKMが、半導体基板SUBに形成された所定の導電型の不純物領域IRに電気的に接続されて、アライメントマークAMおよび重ね合わせ検査マークKMが接地電位に固定されている。

(もっと読む)

半導体装置

【課題】磁気抵抗素子を有する半導体装置であって、フリー層に所望の磁化方向と反対方向の磁界の成分が印加されることによる誤動作を抑制することが可能な半導体装置を提供する。

【解決手段】半導体基板の主表面上に位置する、磁化自由層を有する磁気抵抗素子TMRと、磁気抵抗素子TMRの下方に位置し、第1方向に向けて延び、発生する磁界により磁化自由層の磁化状態を変化させることが可能な第1配線DLと、磁気抵抗素子TMRの上方に位置し、第2方向に向けて延び、発生する磁界により磁化自由層の磁化状態を変化させることが可能な第2配線BLとを備えている。磁化自由層は、第2方向に対して対称であり、平面視における第2方向に垂直な方向に対して非対称である。上記第1配線DLは、磁化自由層と平面視において重なる領域において、磁化自由層が磁化されやすい方向に延びる磁化容易軸の延在する方向Heに沿うように延在している。

(もっと読む)

抵抗変化型メモリ

【課題】 メモリの動作特性の向上を図る。

【解決手段】実施形態の抵抗変化型メモリは、ビット線BLとワード線WLと、第1エミッタ21と、第1ベース23と、第1コレクタ22とを有する、第1駆動型の第1バイポーラトランジスタ2と、第2エミッタ31と、第2ベース33と、第2コレクタ32とを有する第2駆動型の第2バイポーラトランジスタ3と、第1及び第2端子を有する抵抗変化型メモリ素子1と、を具備し、メモリ素子1の第1端子は第1及び第2エミッタ21,31に接続され、メモリ素子1の第2端子は、ビット線BLに接続され、第1及び第2ベース23,33はワード線WLに接続される。

(もっと読む)

半導体装置およびその製造方法

【課題】MRAMを構成する上部の導電要素と下部の導電要素との短絡を抑制することが可能な半導体装置、およびその製造方法を提供する。

【解決手段】主表面を有する半導体基板SUBと、半導体基板SUBの主表面上に位置する、ピン層MPLと、トンネル絶縁層MTLと、フリー層MFLとを含む磁気トンネル接合構造MRDと、磁気トンネル接合構造MRDの下側側面に接する下側絶縁層III1と、下側絶縁層III1上に位置して磁気トンネル接合構造MRDの上側側面に接し、かつ磁気トンネル接合構造MRDの上面を露出する側壁絶縁層III2と、側壁絶縁層III2から露出する磁気トンネル接合構造MRDの上面に接する導電層BLとを備えている。

(もっと読む)

磁気ランダムアクセスメモリ及びその製造方法

【課題】 セルの微細化を図る。

【解決手段】 実施形態による磁気ランダムアクセスメモリは、半導体基板1上に形成された選択素子Trと、選択素子上に形成された多層配線層7a−cと、多層配線層上に形成された層間絶縁膜8と、層間絶縁膜内に形成され、多層配線層を介して選択素子と電気的に接続されたコンタクト層9と、コンタクト層と電気的に接続され、金属材で形成された下部電極層21と、下部電極層の側面を取り囲み、金属材の酸化物で形成された金属酸化絶縁膜26と、下部電極層上に形成された磁気抵抗素子10と、磁気抵抗素子上に形成された上部電極層23と、磁気抵抗素子及び上部電極層の側面上に形成された側壁絶縁膜25と、上部電極層と電気的に接続されたビット線29と、を具備する。

(もっと読む)

半導体装置

【課題】 スピン注入磁化反転を用いたメモリにおいて、高速動作時の低電流書き換え動作を実現し、メモリセル毎のばらつきを抑え、読み出しディスターブを抑える。

【解決手段】 書き換え前に弱いパルスを与えてスピンの状態を不安定にし、書き換え電流を低減する。書き換え電流がパルス幅により非線形に大きくなる領域で読み出しを行い

、ディスターブを抑える。更に、ビット線電荷で注入スピン量を一定とした駆動方法によりばらつきを抑える。

(もっと読む)

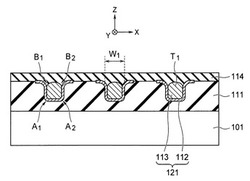

半導体装置および半導体装置の製造方法

【課題】MRAMにおいては、書き込み電流の低減やディスターブ回避を目的に、書き込みに使用する配線を強磁性体膜で覆うクラッド配線構造がよく用いられている。また、高信頼性製品の信頼性確保のためCu配線中に微量のAlを添加するCuAl配線が広く使用されている。MRAMも高信頼性製品に搭載される可能性が高く、信頼性は重要である。しかし、クラッド配線は、もともと配線抵抗が高いCuAl配線の配線抵抗を更に上昇させるというデメリットがあるため、両方の技術を同時に使用すると配線抵抗のスペックを満たさなくなる可能性が高い。

【解決手段】本願発明は、多層銅埋め込み配線を有する半導体装置において、MRAMメモリセルマトリクス領域を構成する複数の銅埋め込みクラッド配線の銅配線膜を比較的純粋な銅で構成し、これらの配線層よりも下層の銅埋め込み非クラッド配線の銅配線膜を、Alを添加したCuAl配線膜とするものである。

(もっと読む)

1 - 20 / 50

[ Back to top ]