Fターム[4M119HH04]の内容

MRAM・スピンメモリ技術 (17,699) | 回路技術 (628) | 読出回路 (209)

Fターム[4M119HH04]の下位に属するFターム

センスアンプ (107)

Fターム[4M119HH04]に分類される特許

1 - 20 / 102

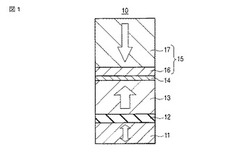

磁気記憶素子

【課題】記憶層に印加される漏れ磁界を低減する。

【解決手段】磁気記憶素子10は、膜面に垂直方向の磁気異方性を有し、かつ磁化方向が可変である記憶層11と、記憶層11上に設けられた非磁性層12と、非磁性層12上に設けられ、かつ膜面に垂直方向の磁気異方性を有し、かつ磁化方向が不変である参照層13と、参照層13上に設けられた非磁性層14と、非磁性層14上に設けられ、かつ参照層13からの漏れ磁界を低減する調整層15とを含む。調整層15は、界面層16と、膜面に垂直方向の磁気異方性を有する磁性層17とが積層されて構成され、界面層16の飽和磁化は、磁性層17の飽和磁化より大きい。

(もっと読む)

磁気メモリ素子

【課題】実施形態による、磁壁制御が容易な磁気メモリ素子を提供する。

【解決手段】磁気メモリ素子100は、第1方向に延在し、磁壁により隔てられた複数の磁区を有する磁性細線20と、前記磁性細線20に対して前記第1の方向又は前記第1の方向と逆方向に通電可能な一対の第1の電極30と、前記第1の方向に直交する第2の方向において、前記磁性細線20上に設けられた第1の絶縁層40と、前記第2の方向であって前記第1の絶縁層40上に離間して設けられた複数の第2の電極50と、複数の前記第2の電極50と電気的に接続された第3の電極60と、を備える。

(もっと読む)

磁気抵抗効果素子、磁気メモリ及び磁気抵抗効果素子の製造方法

【課題】磁気抵抗効果素子の特性劣化を抑制する。

【解決手段】本実施形態の磁気抵抗効果素子は、膜面に対して垂直方向に磁気異方性と不変な磁化方向とを有する第1の磁性体30と、膜面に対して垂直方向に磁気異方性と可変な磁化方向とを有する第2の磁性体10と、磁性層10,30の間の非磁性体20とを、含む。第1及び第2の磁性体のうち少なくとも一方は、ボロン(B)及び希土類金属及び遷移金属を含む磁性層301を備え、磁性層301において、希土類金属の含有量は、20at.%以上であり、遷移金属の含有量は、30at.%以上であり、ボロンの含有量が、1at.%以上、50at.%以下である。

(もっと読む)

電子装置、半導体装置およびその制御方法、ならびに携帯端末装置

【課題】選択されない磁気抵抗素子の磁化状態が誤って書き換えられる現象の発生が確実に抑制される半導体装置の制御方法を提供する。

【解決手段】当該制御方法は、半導体基板と、半導体基板の主表面上に位置する、固定層MPLと、トンネル絶縁層と、磁化容易軸を有する自由層MFLとを含む磁気抵抗素子と、磁気抵抗素子に隣接する第1の配線とを備える半導体装置における磁化状態を書き換える制御方法である。上記制御方法は以下の工程を備えている。まず上記自由層MFLの磁化状態を変更する前の初期磁化状態が判定される。上記判定する工程において、自由層MFLの磁化状態を変更する必要があると判定された場合に、第1の配線にパルス電流が流される。上記パルス電流により、自由層MFLの磁化容易軸と交差する方向に発生するパルス磁場を磁気抵抗素子に印加することにより自由層MFLの磁化状態が変更される。

(もっと読む)

磁気抵抗素子、磁気メモリ及び磁気抵抗素子の製造方法

【課題】低電流で記憶層の磁化を反転させることができるスピン注入書き込み方式の磁気抵抗素子を提供する。

【解決手段】膜面に垂直方向の磁化容易軸を有し、磁化方向が可変の記憶層3と、膜面に垂直方向の磁化容易軸を有し、磁化方向が不変の固定層2と、記憶層3と固定層2との間に設けられた非磁性層4と、記憶層3の、非磁性層4が配置された面と反対の面側に配置された配線層10を有する。記憶層3は、磁性材料31、33と非磁性材料32、34とが交互に積層された構造を有する。非磁性材料32、34がTa、W、Nb、Mo、Zr、Hfの少なくとも1つの元素を含む。磁性材料31、33はCoとFeを含む。磁性材料のうちの1つは非磁性層4と接し、非磁性材料のうちの1つは配線層と接している。

(もっと読む)

磁気抵抗素子及び磁気メモリ

【課題】熱的に安定であると共に、磁気抵抗比の低下が抑制できるスピン注入書き込み方式の磁気抵抗素子を提供する。

【解決手段】固定層2は、非磁性層4に接するように設けられた第1磁性材料膜2aと、第1磁性材料膜2aに接するように設けられた非磁性材料膜2bと、非磁性材料膜2bに接するように設けられた第2磁性材料膜2cと、第2磁性材料膜2cに接するように設けられた第3磁性材料膜2dとが積層された構造を備える。第2磁性材料膜2cは第1磁性材料膜2aよりも高いCo濃度を有する。固定層2と記憶層3との間に非磁性層4を介して電流を流すことにより、記憶層3の磁化の向きを可変する。

(もっと読む)

磁気抵抗素子及び磁気メモリ

【課題】微細化に伴って増大する固定層からの漏れ磁場を低減でき、記憶層における磁化の平行と反平行の2つの状態を安定に存在できるようにした磁気抵抗素子を提供する。

【解決手段】磁気抵抗素子1は、固定層2、記憶層3、及び非磁性層4を備える。固定層2は、非磁性層4に接する第1強磁性材料31、第2強磁性材料32、第1強磁性材料31と第2強磁性材料32との間に設けられた第1非磁性材料33を有する。第1強磁性材料31は、Zr、Nb、Mo、Hf、Ta、Wのうちの少なくとも1つの元素と、Coとを含む。

(もっと読む)

半導体記憶装置

【課題】高速読み出しが可能なMRAMを得る。

【解決手段】行列に並べられたメモリセルを備えるメモリセルアレイと、センスアンプ回路26とを具備し、メモリセルのそれぞれは、データを記憶する少なくとも一の磁気抵抗素子を備え、メモリセルアレイには、n個(n≧2)のメモリセル毎に設けられ、磁気抵抗素子に電流が流されることによって生成される電位を増幅する複数の増幅回路30が配置され、複数の増幅回路のうち、入力されるアドレスに対応して選択されるメモリセルと接続される増幅回路が選択され、センスアンプ回路は、選択された増幅回路の出力に応答して、磁気抵抗素子に記憶された前記データを識別する。

(もっと読む)

磁気ランダムアクセスメモリ及びその動作方法

【課題】スピン注入方式の書き込みを実行するとき磁化方向に依らず書き込み特性が同様となる磁気ランダムアクセスメモリ及びその動作方法を提供する。

【解決手段】スピン注入方式の磁気ランダムアクセスメモリは、複数の磁気メモリセル10と電流供給部43+47+49と制御部41+70+80とを具備する。電流供給部は、磁気メモリセル又はその近傍へ書き込み電流を供給する。磁気メモリセルは、磁化状態によりデータを記憶する磁性体記憶層と、書き込み電流に基づいて書き込むデータに依らず同一の制御原理で磁性体記憶層にスピン電子を供給するスピン制御層とを備える。制御部は、書き込むデータに基づいて、スピン制御層の磁化方向を時間的に連続的に回転させながら、電流供給部の書き込み電流の供給を制御する。

(もっと読む)

抵抗変化型メモリ

【課題】メモリの動作マージンを向上する。

【解決手段】本実施形態の抵抗変化型メモリは、ビット線BLA,BLC間に接続された第1のセルSCAとビット線BLB,BLC間に接続された第2のセルSCBとを含むメモリセルMCと、第1のセルSCAを形成するメモリ素子8A及び選択トランジスタTrAと、第2のセルSCBを形成するメモリ素子8B及び選択トランジスタTrBとを具備し、メモリセルに対する書き込み動作時、ワード線が活性化されている期間において、メモリセルMC内の2つのメモリ素子8A,8Bを第1の抵抗状態に変化させた後、2つのメモリ素子8A,8Bのうち一方のメモリ素子を第2の抵抗状態に変化させる。

(もっと読む)

記憶装置、書込制御方法

【課題】ST−MRAMにおいて記憶素子の破壊を防ぎつつ記憶素子に情報を記憶させ、併せて書込速度の向上を図る。

【解決手段】メモリブロック1−1、1−2に対する書込制御部51−1、51−2とを複数対設け、各書込制御部51−1、51−2が、対を為すメモリブロック1−1または1−2の各記憶素子に書き込まれるべき情報をシフトレジスタ52に格納し、当該シフトレジスタ52から1つの情報をメモリブロック1−1、1−2に出力し、当該出力した情報の書込成否を判定し、書込失敗と判定した場合はメモリブロック1−1、1−2に対して再度同一情報を出力し、書込成功と判定した場合はメモリブロック1−1、1−2において書込可能状態とする前記記憶素子を選択するためのアドレス値を増加させかつ、シフトレジスタ52から次の情報をメモリブロック1−1、1−2に出力する、という書込制御を個々に独立して行う。

(もっと読む)

メモリセルおよび方法

【課題】マルチビット磁気ランダムアクセスメモリセルの不揮発性メモリセルのための装置およびプログラム方法を提供する。

【解決手段】第1の磁気トンネル接合(MTJ)192は、磁気フィルタ208を有する第2のMTJ192に隣接する。第2のMTJ192がプログラムされることを防ぐために第1の磁束212を磁気フィルタ208が吸収しつつ、第1の磁束212を用いて第1のMTJ192が第1の論理状態にプログラムされる。

(もっと読む)

磁気抵抗効果メモリ

【課題】読み出しディスターブを低減する磁気抵抗効果メモリを提供する。

【解決手段】本発明の例に関わる磁気抵抗効果メモリは、磁化方向が不変な第1の磁性層と、磁化方向が可変な第2の磁性層と、第1の磁性層と第2の磁性層の間に設けられた中間層とを有する磁気抵抗効果素子1と、磁気抵抗効果素子1にパルス形状の読み出し電流を流して、前記磁気抵抗効果素子に記憶されたデータを判別する読み出し回路2と、を具備し、読み出し電流のパルス幅は、第2の磁性層内に含まれる磁化が、初期状態から共動してコヒーレントに歳差運動するまでの期間より短い。

(もっと読む)

薄膜磁性体記憶装置

【課題】高集積化に適したメモリセル配置、特に折り返し型ビット線構成に適したメモリセル配置を有する薄膜磁性体記憶装置を提供する。

【解決手段】メモリアレイにおいて、1個のメモリセルMCと対応する繰り返し単位140aが連続的に配置されて、メモリセルMCが行列状に配置される。隣接するメモリセル列間で、繰り返し単位140aは、1/2ピッチ(ハーフピッチ)分だけずらして配置される。ビット線BL1およびBL2は同一のビット線対を構成し、ビット線BL2はデータ読出時において、ビット線BL1の相補線/BL1として動作する。選択されたリードワード線RWLに対応して、1本おきのビット線にメモリセルが接続されるので、セルサイズを増加させることなく折返し型ビット線構成に基づくデータ読出に適したメモリセル配置を実行できる。

(もっと読む)

薄膜磁性体記憶装置

【課題】製造時ばらつきに対応して、データ読出時における高い信号マージンを確保可能な薄膜磁性体記憶装置を提供する。

【解決手段】ダミーメモリセルDCPは、2個のセルユニットCU0およびCU1を含む。各セルユニットCU0,CU1は、メモリセルと同様の構成を有し、ビット線BLと接地電圧Vssとの間に直列に結合された、トンネル磁気抵抗素子TMRおよびアクセストランジスタATRを有する。セルユニットCU0,CU1に対しては、異なる記憶データ“0”および“1”がそれぞれ書込まれる。データ読出時において、2個のセルユニットCU0,CU1が、読出参照電圧Vrefを伝達するためのビット線BLと接地電圧Vssとの間に並列に接続される。さらに、ダミーメモリセルDCPに対して、電流供給回路52からメモリセルに供給されるセンス電流Isの2倍、すなわち2・Isの一定電流が供給される。

(もっと読む)

半導体集積回路

【課題】 メモリの動作特性の向上を図る。

【解決手段】本実施形態の半導体集積回路は、第1の端子aが第1の電源スイッチを介して第1の電源に接続され、第2の端子bがノードN1に接続される第1の抵抗変化型メモリ素子R1と、第3の端子aがノードN1に接続され、第4の端子bが第2の電源スイッチを介して第2の電源に接続される第2の抵抗変化型メモリ素子R2と、電流経路の一端が第1のプログラム電源PV1に接続され、電流経路の他端がノードN1に接続される第1のスイッチM2と、電流経路の一端がノードN1に接続され、電流経路の他端が第1のプログラム電源PV1と異なる電圧値を出力する第2のプログラム電源PV2に接続される第2のスイッチM3と、を含んでいる。

(もっと読む)

半導体装置

【課題】電源電圧の変動に起因した書込電流の変動を抑制する。

【解決手段】ドライブ回路25において、第1のMOSトランジスタPMは、第1および第2の電源ノード28,29間にデータ書込線DLと直列に設けられる。第2のMOSトランジスタPSは、第1のMOSトランジスタPMと並列に設けられる。第3および第4のMOSトランジスタPa,Pbは、互いに同じ電流電圧特性を有する。第1の素子Eaは、第1および第2の電源ノード28,29間に第3のMOSトランジスタPaと直列に接続される。第2の素子Ebは、第1および第2の電源ノード28,29間に第4のMOSトランジスタPbと直列に接続され、第1の素子Eaの電流電圧特性曲線と交差する電流電圧特性を有する。比較器30は、第1の素子Eaにかかる電圧と第2の素子Ebにかかる電圧とを比較し、比較結果に応じて第2のMOSトランジスタPSをオンまたはオフにする。

(もっと読む)

磁気メモリ

【課題】磁気メモリの信頼性及び動作特性の向上を図る。

【解決手段】磁気メモリは、第1及び第2の磁性層の間に設けられた中間層とを有する磁気抵抗効果素子と、磁気抵抗効果素子に書き込まれた第1のデータが第1のデータが誤りを含むか否かを検出し、第1のデータが誤りを含む場合にその誤りが訂正された第2のデータを出力する誤り検出訂正回路と、第1のパルス幅Twp1を有する第1の書き込み電流Iw1及び第1のパルス幅Twp1より長い第2のパルス幅Twp2を有する第2の書き込み電流Iw2のいずれか一方を生成し、磁気抵抗効果素子に流す書き込み回路と、第2のデータを磁気抵抗効果素子に書き込む場合、第2の書き込み電流Iw2を磁気抵抗効果素子に流すように書き込み回路を制御する制御回路と、を備える。

(もっと読む)

不揮発性半導体記憶装置

【課題】メモリセルのトランジスタの配置効率が高い不揮発性半導体記憶装置を提供する。

【解決手段】このMRAMでは、各メモリセルMCのアクセストランジスタを2つのトランジスタQA,QBに分割し、トランジスタQA,QBのゲートをそれぞれワード線WLA,WLBに接続し、奇数番のメモリブロックMBのワード線WLA,WLBを主ワード線MWLAに接続し、偶数番のメモリブロックMBのワード線WLA,WLBを主ワード線MWLBに接続する。したがって、メモリセルMCのトランジスタの配置効率を高めることができる。

(もっと読む)

抵抗変化型半導体メモリ

【課題】セル面積の縮小及び動作特性の向上に優れたレイアウトを提案する。

【解決手段】実施形態によれば、抵抗変化型半導体メモリは、第1方向に並ぶ第1乃至第4メモリセルを備える。第1乃至第4メモリセルの各々は、第1ソース/ドレインが第1方向に延びる第1ビット線BLA1に接続され、ゲートが第2方向に延びるワード線WL1, WL2, WL3, WL4に接続されるセルトランジスタT11, T12, T13, T14と、一端がセルトランジスタT11, T12, T13, T14の第2ソース/ドレインに接続され、他端が第2方向に延びる第2ビット線BLB1, BLB2, BLB3, BLB4に接続される抵抗性記憶素子M11, M12, M13, M14とを有する。第1及び第2メモリセル内の第1ソース/ドレインは、共有化され、第3及び第4メモリセル内の第1ソース/ドレインは、共有化される。

(もっと読む)

1 - 20 / 102

[ Back to top ]