Fターム[4M119HH05]の内容

MRAM・スピンメモリ技術 (17,699) | 回路技術 (628) | 読出回路 (209) | センスアンプ (107)

Fターム[4M119HH05]に分類される特許

1 - 20 / 107

半導体記憶装置

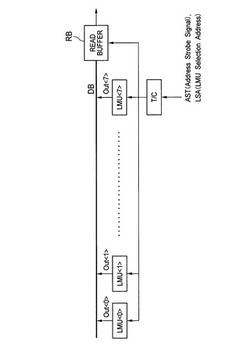

【課題】共通データバスを共有する複数のローカルメモリユニットが重複してデータを転送すること、あるいは、複数のローカルメモリユニットに対して重複してデータを転送することを抑制した半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、複数のメモリセルを含む複数のローカルメモリユニットLMU<0>〜LMU<7>を備える。共通データバスDBは、複数のローカルメモリユニットに共有され、複数のローカルメモリユニットからデータを転送し、あるいは、複数のローカルメモリユニットへデータを転送する。タイミングコントローラT/Cはローカルメモリユニットの単位で配置するのではなく、インターリーブ動作を行なう単位(ローカルメモリユニットLMU<0>〜LMU<7>のグループ)に対して1つ配置する。これにより読出しデータまたは書込みデータは、共通データバスDBにおいて衝突しない。

(もっと読む)

半導体装置

【課題】直流電源配線に電流が流れたか否かを検出可能な回路を備えた半導体装置を提供する。

【解決手段】半導体装置において、駆動回路BLDU,BLDD,BLBDU,BLBDDは、電流磁界またはスピン注入によってトンネル磁気抵抗素子TMR,TMRBを第1の磁化状態に初期設定するために、制御信号線BL,BLBに直流電流を流す。電源配線DLは、トンネル磁気抵抗素子TMR,TMRBに近接して設けられる。ここで、トンネル磁気抵抗素子TMR,TMRBは、電源配線DLに直流電流が流れるときに生じる電流磁界によって第2の磁化状態に変化する。センスアンプ10は、トンネル磁気抵抗素子TMR,TMRBが第1の磁化状態から第2の磁化状態に変化したか否かを判定するために、制御信号線BL,BLBを介してトンネル磁気抵抗素子TMR,TMRBに流れる電流を検出する。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】ビット当たりの単価を低減できる半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、第1方向に沿う第1部分(11a)と第2方向に沿いかつ第1部分と接続された第2部分(11b)とを有し、第2部分において半導体材料を含み、第1方向および第2方向からなる第1平面と交わる方向に沿って離れて並ぶ少なくとも2つの第1配線(11)を含む。可変抵抗膜(15)は、第1配線の第2部分に接続された第1面を有し、相違する抵抗値を示す複数の状態を取り得る。第2配線(12)は、可変抵抗膜の第1面と対向する第2面と接続されている。制御線(13)は、第1平面と交わる方向に沿い、少なくとも2つの第1配線の第2部分の半導体材料を含む部分と絶縁膜を介して接し、第1配線の第2部分の半導体材料を含む部分および絶縁膜とともにトランジスタを構成する。

(もっと読む)

半導体装置およびその製造方法

【課題】素子特性を劣化させることなく、半導体材料または絶縁膜の結晶特性を改善することができる低温アニールを用いた半導体装置の製造方法、並びに、このような低温アニールに適した半導体装置を提供する。

【解決手段】本実施形態による半導体装置は、半導体基板の上方に設けられた金属からなる下部電極と、下部電極の上方に設けられた金属からなる上部電極と、下部電極と上部電極との間に設けられた結晶層とを備える。下部電極および上部電極の各膜厚は、結晶層の結晶化に用いられるマイクロ波の周波数に対応する表皮効果における表皮層よりも薄い。

(もっと読む)

半導体記憶装置

【課題】4個のトランジスタと2個のMTJ素子からなり、電源を印加しないでも不揮発性メモリとして動作するSRAMからなる半導体記憶装置を提供する。

【解決手段】第1及び第2のインバータ2,4と第1及び第2の転送用MOSFET3,5とを含むメモリセル1からなるSRAMにおいて、第1及び第2のインバータ2,4はスピン注入型のMTJ素子6,8と駆動用MOSFET7,9とからなり、これらのインバータ2,4からフリップフロップ回路が構成され、第1及び第2のインバータ2,4の出力端子は、それぞれ第1及び第2の転送用MOSFET3,5を介してビットライン及びビットラインバーに接続され、第1及び第2の転送用MOSFET3,5のゲートは、同一のワードラインに接続される。従来のSRAMに比較してメモリセルの面積が小さく、高速で低消費電力の不揮発性メモリが得られる。

(もっと読む)

磁気ランダムアクセスメモリ

【課題】磁壁移動型MRAMのメモリセルの面積を小さくする。

【解決手段】磁気ランダムアクセスメモリが、メモリセルC1〜C3が形成されたメモリセルライン1と、書き込みビット線12−1〜12−4とを具備する。メモリセルライン1は、磁気記録層4と、磁化固定層3−1〜3−4と、リファレンス層6−1〜6−3と、スペーサ層5−1〜5−3と、nMOSトランジスタ2−1〜2−4とを備えている。スペーサ層5−iとリファレンス層6−iとは、磁化固定層3−iと磁化固定層3−(i+1)の間に位置している。磁化固定層3−1、3−3と、磁化固定層3−2、3−4は、互いに逆の方向に固定された磁化を有している。リファレンス層6−1〜6−3も、固定された磁化を有している。nMOSトランジスタ2−iは、書き込みビット線12−iと磁化固定層3−iの間に設けられている。

(もっと読む)

半導体記憶装置

【課題】参照セルにおける誤書き込みの発生を抑制し、より高精度にデータを読み出すことが可能な半導体記憶装置を提供する。

【解決手段】半導体記憶装置100の参照セルは、第3のビット線BL3に一端が接続され且つ第2のワード線RWLにゲートが接続された第3の選択トランジスタTr3と、第3の選択トランジスタの他端に一端が接続され且つ第3の電圧端子G3に他端が接続された第3の抵抗変化素子R3とを有する第3のメモリセルM3と、第4のビット線BL4に一端が接続された第4の抵抗変化素子R4と、第4の抵抗変化素子の他端と第4の電圧端子G4との間に接続され且つ第2のワード線RWLにゲートが接続された第4の選択トランジスタTr4とを有する第4のメモリセルM4から構成される。さらに第3のビット線BL3と前記第4のビット線BL4との間に接続され、読み出し動作時に電位とを等価にするための第1の電位制御回路Ti1を備える。

(もっと読む)

半導体記憶装置

【課題】MTJ素子にデータを書き込むために充分に大きな電流を駆動することができるセルトランジスタを備え、かつ、容易に製造可能なメモリを提供する。

【解決手段】本実施形態によるメモリはアクティブエリアを備え、セルトランジスタはアクティブエリアに形成されている。MTJ素子の一端がセルトランジスタのソース/ドレインの一方に電気的に接続されている。第1のビット線は、セルトランジスタのソース/ドレインの他方に電気的に接続されている。第2のビット線は、MTJ素子の他端に電気的に接続されている。ワード線は、セルトランジスタのゲートに電気的に接続され、あるいは、セルトランジスタのゲートとして機能する。1つの第1のビット線に対して複数の第2のビット線が対応している。MTJ素子が同一のワード線および同一のアクティブエリアを共有している。アクティブエリアは、第1および第2のビット線の延伸方向に連続して形成されている。

(もっと読む)

半導体記憶装置

【課題】記憶素子に充分な電流を流すことができるようにセルトランジスタの電流駆動能力を充分に確保しつつ、ユニットセルのレイアウト面積が従来よりも小さい半導体記憶装置を提供する。

【解決手段】本実施形態による半導体記憶装置は、半導体基板と、半導体基板に形成されたアクティブエリアを備える。複数のセルトランジスタがアクティブエリアに形成されている。第1のビット線および第2のビット線は、互いに対をなす。複数のワード線は第1および第2のビット線と交差する。複数の記憶素子の一端がセルトランジスタのソースまたはドレインに電気的に接続され、他端が第1または第2のビット線に接続されている。第1および第2のビット線は、両方とも同一のアクティブエリアに対して記憶素子を介して接続されている。

(もっと読む)

磁気メモリ

【課題】書き込み時に固定層が安定化された、垂直磁化型トンネル磁気抵抗効果素子を用いたスピントルク磁化反転応用の磁気メモリを提供する。

【解決手段】膜面に垂直な方向の磁化を有する自由層62と、膜面に垂直な一方向に磁化が固定された固定層64と、固定層と自由層の間に形成された非磁性障壁層63を有する磁気抵抗効果素子において、互いに隣接したメモリセルの固定層を一列方向に接続する。

(もっと読む)

磁気メモリデバイスの駆動方法及び磁気メモリデバイス

【課題】基準素子におけるディスターバンスの発生を防止することができる磁気メモリデバイスを提供する。

【解決手段】基準セル28が、基準素子20を含む。基準素子は、固定磁化層21、絶縁層22、自由磁化層23を含み、自由磁化層の磁化方向は固定磁化層の磁化方向と反平行であり、メモリセル18の磁気抵抗素子10が平行状態のときの抵抗値と反平行状態のときの抵抗値との間の抵抗値を有する。基準素子に、基準素子の固定磁化層から自由磁化層に向かう読出電流を流し、磁気抵抗素子の抵抗値と、基準素子の抵抗値との大小関係に依存する物理量を検出することにより、情報の読出しを行う。

(もっと読む)

非揮発性メモリ装置及びセンシング方法

【課題】抵抗変化を利用したマルチレベルのデータをセンシングする非揮発性メモリ装置において、読出し動作の回数を減らし、読出し動作の制御に係わる回路の面積を縮小する。

【解決手段】非揮発性メモリ装置は、1つ以上の単位セルを含んでデータの読出し又は書込みが行なわれるセルアレイと、単位セルに格納されたデータに対応するセンシング電圧SAIと基準電圧REFを比較及び増幅して出力し、ビットラインがプリチャージされた以後にセンシングイネーブル信号SENの活性化区間で、単位セルの抵抗値に応じてセンシング電圧がディスチャージされる時間の差を測定し、データをセンシングするセンシング部100とを含む。

(もっと読む)

集積回路装置及びその製造方法

【課題】ビアの形成が容易で抵抗が低い集積回路装置及びその製造方法を提供する。

【解決手段】相互に平行に配列された複数本の配線14a、14bと、各配線に接続されたビア16とを備える。配線におけるビアが接続された部分には、配列の方向に延出した凸部31が形成されており、配線における凸部が形成された部分から離隔した部分には、配列の方向に後退した凹部32が形成されている。隣り合う2本の配線において、一方の配線に形成された凸部と他方の配線に形成された凹部とは相互に対向している。各配線において、凹部が形成された部分はその両側の部分から切込33で分断されており、凸部が形成された部分からも分断されている。

(もっと読む)

半導体記憶装置

【課題】記憶素子の配置を均等にし、微細化および大容量化を実現可能な半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、複数のビット線と、複数のワード線と、互いに隣接する2本の前記ビット線間に直列に接続された記憶素子およびセルトランジスタを含む複数のメモリセルとを備える。2本のビット線間に接続された複数のメモリセルのそれぞれのセルトランジスタのゲートは、互いに異なるワード線に接続されている。互いに隣接する複数のメモリセルの複数の前記記憶素子および複数のセルトランジスタは、交互に直列に接続される。

(もっと読む)

抵抗変化型メモリ

【課題】メモリの動作マージンを向上する。

【解決手段】本実施形態の抵抗変化型メモリは、ビット線BLA,BLC間に接続された第1のセルSCAとビット線BLB,BLC間に接続された第2のセルSCBとを含むメモリセルMCと、第1のセルSCAを形成するメモリ素子8A及び選択トランジスタTrAと、第2のセルSCBを形成するメモリ素子8B及び選択トランジスタTrBとを具備し、メモリセルに対する書き込み動作時、ワード線が活性化されている期間において、メモリセルMC内の2つのメモリ素子8A,8Bを第1の抵抗状態に変化させた後、2つのメモリ素子8A,8Bのうち一方のメモリ素子を第2の抵抗状態に変化させる。

(もっと読む)

磁気抵抗効果素子、磁気ヘッドアセンブリ及び磁気記録装置

【課題】MR変化率を高くすることができる磁気抵抗効果素子、磁気ヘッドアセンブリ及び磁気記録装置を提供する。

【解決手段】実施形態に係る磁気抵抗効果素子は、積層体と、前記積層体の積層方向に電流を流すための一対の電極と、を備える。前記積層体は、第1の磁性層と、第2の磁性層と、前記第1の磁性層と前記第2の磁性層との間に配置されたスペーサ層と、を有する。そして、前記第1の磁性層、前記第2の磁性層及び前記スペーサ層の少なくとも1つの層が金属酸化物からなる酸化物層を含み、前記金属酸化物の結晶構造は、NaCl構造である。

(もっと読む)

半導体記憶装置

【課題】 スピン注入磁化反転を用いた磁性体メモリにおいて、微細な磁気抵抗素子を用いると書き込み電流が低減できるが、読み出し時のデータ破壊を防止するために読み出し電流も小さくする必要があり、読み出し動作の遅延につながる。

【解決手段】 ワード線(WL)が選択された後に、センスアンプ(SA)が活性化されて第1ビット線(BLt0)が第1電位(VDD)に、第2ビット線(BLb0)が第2電位(VSS)に駆動され、その後、ソース線(SL0)が第1電位から第2電位に駆動されることにより、時分割で反平行状態と平行状態の再書き込み動作を行う。

(もっと読む)

磁気ランダムアクセスメモリ

【課題】一端がビット線に接続された磁気抵抗素子と、一端が磁気抵抗素子の他端に接続され、ゲートが読み出し用ワード線に接続され、他端が接地に接続された選択トランジスタとで構成されたメモリセルよりなるスピン注入方式の磁気ランダムアクセスメモリであって、従来と同等の書き込み電流値を確保し、書き込みマージンと読み出しマージンの両方を確保できる磁気ランダムアクセスメモリを提供する。

【解決手段】磁気抵抗素子は個別の磁気抵抗素子を複数直列に接続されてなり、個別の磁気抵抗素子の両端部に、それぞれNチャンネルトランジスタおよびPチャンネルトランジスタがドレインで接続され、Nチャンネルトランジスタのゲートに書き込み用ワード線が接続されソースに接地電圧が接続され、Pチャンネルトランジスタのゲートに反転書き込み用ワード線が接続されソースに電源電圧が接続された構成であることを特徴とする。

(もっと読む)

半導体装置

【課題】正常な書込動作が実現できるセグメント書込み手法を用いた半導体装置を提供する。

【解決手段】第1および第2DLドライバ12a,12bは、それぞれ選択された1つのブロックのディジット線に磁化電流を流す。BLドライバ6は、データ信号の論理に応じた方向の書込電流を選択されたセグメント内の全ビット線に流して、選択されたブロックのメモリセルにデータ信号を書込む。セグメントデコーダ14は、外部から1個のセグメントのアドレスが入力されたときに、アドレスに対応する1個のセグメントを選択し、選択したセグメント第1DLドライバ12aへ接続し、外部から2個以上のセグメントのアドレスが入力されたときに、アドレスに対応する2個以上のセグメントを選択し、選択した2個のセグメントをそれぞれ第1DLドライバ12aと第2DLドライバ12bへ接続する。

(もっと読む)

磁気メモリ

【課題】書き込みマージン及び読み出しマージンを改善する。

【解決手段】磁気メモリ10は、磁気抵抗素子20と、選択トランジスタ21及び22とを含む。磁気抵抗素子20は、参照層30、非磁性層31、記録層32、非磁性層33、及び参照層34が順に積層されて構成され、記録層32は、磁化方向が可変でありかつハイレベル電圧が印加される端子に接続され、参照層30及び34は、磁化方向が不変でありかつ互いの磁化方向が反平行である。選択トランジスタ21は、ビット線BLと参照層30との間に接続され、N型MOSFETからなる。選択トランジスタ22は、ビット線BLBと参照層34との間に接続され、N型MOSFETからなる。選択トランジスタ21及び22のゲートは、共通のワード線WLに接続される。

(もっと読む)

1 - 20 / 107

[ Back to top ]