Fターム[4M119HH07]の内容

MRAM・スピンメモリ技術 (17,699) | 回路技術 (628) | アドレス選択回路 (81)

Fターム[4M119HH07]に分類される特許

1 - 20 / 81

半導体装置の製造方法

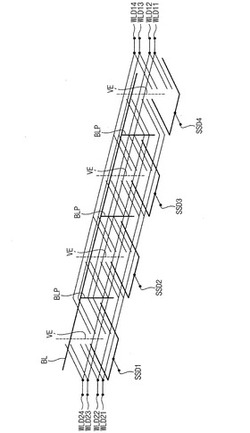

3次元半導体装置

【課題】増加された集積度を有し且つ高密度で高速の3次元(抵抗性)半導体(メモリ)装置を、最小限のマスク工程数で提供する。

【解決手段】チャンネル領域によって分離された第1及び第2不純物領域を含む基板、前記第1不純物領域に接続するビットライン、前記第2不純物領域に接続する垂直電極、前記基板と前記ビットラインとの間に配置される水平電極の積層体、及び、前記積層体と前記基板との間に配置される選択ラインを含む。この時,前記選択ラインは平面形状及び平面位置において、前記水平電極の各々と実質的に同一であり得る。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板上の複数の半導体層のうちの1つを正確に選択する。

【解決手段】実施形態に係わる半導体装置は、第1乃至第3の半導体層12−1〜12−3と、第1乃至第3の半導体層12−1〜12−3のうちの1つを選択するレイヤー選択トランジスタ15(LST)とを備える。第1のノーマリーオン領域17−1は、第1の半導体層12−1内において第1乃至第3のゲート電極16−1〜16−3に隣接するチャネルをノーマリーオンチャネルにし、第2のノーマリーオン領域17−2は、第2の半導体層12−2内において第2乃至第4のゲート電極16−2〜16−4に隣接するチャネルをノーマリーオンチャネルにし、第3のノーマリーオン領域17−3は、第3の半導体層12−3内において第3乃至第5のゲート電極16−3〜16−5に隣接するチャネルをノーマリーオンチャネルにする。

(もっと読む)

縮小されたビットセル寸法を有するスピン注入トルク磁気抵抗ランダムアクセスメモリ

【課題】スピン注入トルク磁気抵抗ランダム・アクセス・メモリ(STT−MRAM)のメモリセル寸法を縮小する。

【解決手段】ワード・ラインWLに対して実質的に平行にかつビット・ラインBLに対して実質的に垂直にソース・ラインSLを配列することによって、縮小されたビット・セル寸法が達成される。さらに、1つの実施の形態では、書込み動作時に、無効な書込み動作を防止するために、選択されないビット・セルのビット・ラインにハイ論理/電圧レベルが印加される。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】ビット当たりの単価を低減できる半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、第1方向に沿う第1部分(11a)と第2方向に沿いかつ第1部分と接続された第2部分(11b)とを有し、第2部分において半導体材料を含み、第1方向および第2方向からなる第1平面と交わる方向に沿って離れて並ぶ少なくとも2つの第1配線(11)を含む。可変抵抗膜(15)は、第1配線の第2部分に接続された第1面を有し、相違する抵抗値を示す複数の状態を取り得る。第2配線(12)は、可変抵抗膜の第1面と対向する第2面と接続されている。制御線(13)は、第1平面と交わる方向に沿い、少なくとも2つの第1配線の第2部分の半導体材料を含む部分と絶縁膜を介して接し、第1配線の第2部分の半導体材料を含む部分および絶縁膜とともにトランジスタを構成する。

(もっと読む)

半導体記憶装置

【課題】4個のトランジスタと2個のMTJ素子からなり、電源を印加しないでも不揮発性メモリとして動作するSRAMからなる半導体記憶装置を提供する。

【解決手段】第1及び第2のインバータ2,4と第1及び第2の転送用MOSFET3,5とを含むメモリセル1からなるSRAMにおいて、第1及び第2のインバータ2,4はスピン注入型のMTJ素子6,8と駆動用MOSFET7,9とからなり、これらのインバータ2,4からフリップフロップ回路が構成され、第1及び第2のインバータ2,4の出力端子は、それぞれ第1及び第2の転送用MOSFET3,5を介してビットライン及びビットラインバーに接続され、第1及び第2の転送用MOSFET3,5のゲートは、同一のワードラインに接続される。従来のSRAMに比較してメモリセルの面積が小さく、高速で低消費電力の不揮発性メモリが得られる。

(もっと読む)

不揮発性メモリセルおよび不揮発性メモリ

【課題】 スタティックノイズマージンを損なうことなく、揮発性記憶部および不揮発性記憶部間のストアとリコールを行える不揮発性メモリセルを提供する。

【解決手段】 不揮発性記憶部12は、揮発性記憶部11のノードV1とバイアス供給ノードNSとの間に直列に介挿されたNチャネルトランジスタTw1および抵抗変化型素子R1と、揮発性記憶部11のノードV2とバイアス供給ノードNSとの間に直列に介挿されたNチャネルトランジスタTw2および抵抗変化型素子R2を有する。ストア時、NチャネルトランジスタTw1およびTw2はONとされ、抵抗変化型素子R1およびR2は、ノードV1(V2)からバイアス供給ノードNSに向かう電流を通過させたときに高抵抗となり、逆方向の電流を通過させたときに低抵抗となる。リコール時は、揮発性記憶部11のフリップフロップに対する電源電圧を立ち上げる。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】高集積化に適した不揮発性半導体記憶装置を提供する。

【解決手段】実施形態に係わる不揮発性半導体記憶装置は、第1乃至第3のフィン型積層構造Fin1〜Fin3を有する。第1乃至第3のフィン型積層構造Fin1〜Fin3は、第1の方向に積み重ねられる第1及び第2の半導体層Sm1,Sm2を備える。第1及び第2のアシストゲート電極AG1,AG2は、第3の方向に並んで配置され、第3のフィン型積層構造Fin3の第1の方向にある表面上で互いに分断される。第1のアシストゲートトランジスタAGT1は、第1及び第3のフィン型積層構造Fin1,Fin3内に形成され、第2のアシストゲートトランジスタAGT2は、第2及び第3のフィン型積層構造Fin2,Fin3内に形成される。

(もっと読む)

半導体記憶装置

【課題】MTJ素子にデータを書き込むために充分に大きな電流を駆動することができるセルトランジスタを備え、かつ、容易に製造可能なメモリを提供する。

【解決手段】本実施形態によるメモリはアクティブエリアを備え、セルトランジスタはアクティブエリアに形成されている。MTJ素子の一端がセルトランジスタのソース/ドレインの一方に電気的に接続されている。第1のビット線は、セルトランジスタのソース/ドレインの他方に電気的に接続されている。第2のビット線は、MTJ素子の他端に電気的に接続されている。ワード線は、セルトランジスタのゲートに電気的に接続され、あるいは、セルトランジスタのゲートとして機能する。1つの第1のビット線に対して複数の第2のビット線が対応している。MTJ素子が同一のワード線および同一のアクティブエリアを共有している。アクティブエリアは、第1および第2のビット線の延伸方向に連続して形成されている。

(もっと読む)

磁気メモリ

【課題】書き込み時に固定層が安定化された、垂直磁化型トンネル磁気抵抗効果素子を用いたスピントルク磁化反転応用の磁気メモリを提供する。

【解決手段】膜面に垂直な方向の磁化を有する自由層62と、膜面に垂直な一方向に磁化が固定された固定層64と、固定層と自由層の間に形成された非磁性障壁層63を有する磁気抵抗効果素子において、互いに隣接したメモリセルの固定層を一列方向に接続する。

(もっと読む)

抵抗変化型メモリ

【課題】メモリの動作マージンを向上する。

【解決手段】本実施形態の抵抗変化型メモリは、ビット線BLA,BLC間に接続された第1のセルSCAとビット線BLB,BLC間に接続された第2のセルSCBとを含むメモリセルMCと、第1のセルSCAを形成するメモリ素子8A及び選択トランジスタTrAと、第2のセルSCBを形成するメモリ素子8B及び選択トランジスタTrBとを具備し、メモリセルに対する書き込み動作時、ワード線が活性化されている期間において、メモリセルMC内の2つのメモリ素子8A,8Bを第1の抵抗状態に変化させた後、2つのメモリ素子8A,8Bのうち一方のメモリ素子を第2の抵抗状態に変化させる。

(もっと読む)

半導体記憶装置

【課題】書き込みマージンの増加および回路面積の縮小を図ることが可能な半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、第1のビット線の一端に一端が接続された第1のスイッチ回路を備える。半導体記憶装置は、第2のビット線の一端に一端が接続された第2のスイッチ回路を備える。半導体記憶装置は、ワード線の電圧を制御するロウデコーダを備える。半導体記憶装置は、第1のスイッチ回路の他端に、書き込み電流を入出力するための第1の信号端子が接続された第1の書き込み回路を備える。半導体記憶装置は、 第2のスイッチ回路の他端に、書き込み電流を入出力するための第2の信号端子が接続された第2の書き込み回路を備える。半導体記憶装置は、ワード線に制御端子が接続された選択トランジスタを備える。半導体記憶装置は、第1のビット線と第2のビット線との間で選択トランジスタと直列に接続され、流れる電流に応じてその抵抗値が変化する抵抗変化素子と、を備える。

(もっと読む)

磁気抵抗効果素子、磁気ヘッドアセンブリ及び磁気記録装置

【課題】MR変化率を高くすることができる磁気抵抗効果素子、磁気ヘッドアセンブリ及び磁気記録装置を提供する。

【解決手段】実施形態に係る磁気抵抗効果素子は、積層体と、前記積層体の積層方向に電流を流すための一対の電極と、を備える。前記積層体は、第1の磁性層と、第2の磁性層と、前記第1の磁性層と前記第2の磁性層との間に配置されたスペーサ層と、を有する。そして、前記第1の磁性層、前記第2の磁性層及び前記スペーサ層の少なくとも1つの層が金属酸化物からなる酸化物層を含み、前記金属酸化物の結晶構造は、NaCl構造である。

(もっと読む)

半導体装置

【課題】制御チップと複数の被制御チップが積層されたタイプの半導体装置において、コマンド信号よりも層アドレス信号を早く伝送させる。

【解決手段】互いに異なる層情報を保持する複数の被制御チップCC0〜CC7と、被制御チップCC0〜CC7に対して層アドレス信号A13〜A15及びコマンド信号ICMDを共通に供給する制御チップIFとを備える。層アドレス信号A13〜A15を構成する各ビットは、複数の第1の貫通電極のうち、被制御チップごとに並列接続された少なくとも2本の貫通電極を経由して伝送され、コマンド信号ICMDを構成する各ビットは、出力切り替え回路及び入力切り替え回路によって選択された対応する1本の貫通電極を経由して伝送される。これにより、コマンド信号ICMDよりも先に層アドレス信号A13〜A15が各被制御チップに到達する。

(もっと読む)

メモリセルおよび方法

【課題】マルチビット磁気ランダムアクセスメモリセルの不揮発性メモリセルのための装置およびプログラム方法を提供する。

【解決手段】第1の磁気トンネル接合(MTJ)192は、磁気フィルタ208を有する第2のMTJ192に隣接する。第2のMTJ192がプログラムされることを防ぐために第1の磁束212を磁気フィルタ208が吸収しつつ、第1の磁束212を用いて第1のMTJ192が第1の論理状態にプログラムされる。

(もっと読む)

薄膜磁性体記憶装置

【課題】製造時ばらつきに対応して、データ読出時における高い信号マージンを確保可能な薄膜磁性体記憶装置を提供する。

【解決手段】ダミーメモリセルDCPは、2個のセルユニットCU0およびCU1を含む。各セルユニットCU0,CU1は、メモリセルと同様の構成を有し、ビット線BLと接地電圧Vssとの間に直列に結合された、トンネル磁気抵抗素子TMRおよびアクセストランジスタATRを有する。セルユニットCU0,CU1に対しては、異なる記憶データ“0”および“1”がそれぞれ書込まれる。データ読出時において、2個のセルユニットCU0,CU1が、読出参照電圧Vrefを伝達するためのビット線BLと接地電圧Vssとの間に並列に接続される。さらに、ダミーメモリセルDCPに対して、電流供給回路52からメモリセルに供給されるセンス電流Isの2倍、すなわち2・Isの一定電流が供給される。

(もっと読む)

半導体装置

【課題】正常な書込動作が実現できるセグメント書込み手法を用いた半導体装置を提供する。

【解決手段】第1および第2DLドライバ12a,12bは、それぞれ選択された1つのブロックのディジット線に磁化電流を流す。BLドライバ6は、データ信号の論理に応じた方向の書込電流を選択されたセグメント内の全ビット線に流して、選択されたブロックのメモリセルにデータ信号を書込む。セグメントデコーダ14は、外部から1個のセグメントのアドレスが入力されたときに、アドレスに対応する1個のセグメントを選択し、選択したセグメント第1DLドライバ12aへ接続し、外部から2個以上のセグメントのアドレスが入力されたときに、アドレスに対応する2個以上のセグメントを選択し、選択した2個のセグメントをそれぞれ第1DLドライバ12aと第2DLドライバ12bへ接続する。

(もっと読む)

半導体記憶装置

【課題】 チップ面積を増加することなく、フューズセルを実現する。

【解決手段】 実施形態による半導体記憶装置は、第1セルアレイ10−1内に配置された第1参照セルRCと、第1セルアレイ10−1内に配置され、第1参照セルRCが配置されたロウ又はカラムと同一のロウ又はカラムに並べられた複数の第1フューズセルFCと、を具備する。

(もっと読む)

不揮発性記憶装置

【課題】電源投入後、高速なセットアップが可能な不揮発性記憶装置を提供する。

【解決手段】不揮発性記憶装置は、データを不揮発的に記憶するメモリセルを有する第1および第2のメモリモジュール16−1、16−2と、第1および第2のメモリモジュールとそれぞれ接続されて、前記第1および第2のメモリモジュールを駆動するための外部電源を供給する第1および第2の外部電源線VL11、VL12とを備え、第1の外部電源線の電源容量C1は、前記第2の外部電源線の電源容量C2よりも小さい。

(もっと読む)

不揮発性半導体記憶装置

【課題】メモリセルのトランジスタの配置効率が高い不揮発性半導体記憶装置を提供する。

【解決手段】このMRAMでは、各メモリセルMCのアクセストランジスタを2つのトランジスタQA,QBに分割し、トランジスタQA,QBのゲートをそれぞれワード線WLA,WLBに接続し、奇数番のメモリブロックMBのワード線WLA,WLBを主ワード線MWLAに接続し、偶数番のメモリブロックMBのワード線WLA,WLBを主ワード線MWLBに接続する。したがって、メモリセルMCのトランジスタの配置効率を高めることができる。

(もっと読む)

1 - 20 / 81

[ Back to top ]