Fターム[4M119KK03]の内容

MRAM・スピンメモリ技術 (17,699) | 集積又は混載技術 (507) | 半導体素子との混載技術 (194) | メモリセル部と周辺回路部との関係 (70) | メモリセル部及び周辺回路部の同時形成 (28)

Fターム[4M119KK03]に分類される特許

1 - 20 / 28

半導体磁気記憶装置

【課題】磁気記憶素子を構成する層を、周辺回路部内で有効に活用する。

【解決手段】実施形態によれば、半導体磁気記憶装置は、セルトランジスタを含むセル部と、周辺トランジスタを含む周辺回路部とが形成された半導体基板を備える。さらに、前記装置は、前記セル部内に配置され、下部電極と、前記下部電極上に形成された電極間層と、前記電極間層上に形成された上部電極とを含む磁気記憶素子を備える。さらに、前記装置は、前記周辺回路部内に配置され、前記下部電極を形成している第1の層と、前記電極間層を形成している第2の層と、前記上部電極を形成している第3の層とを含む構造体を備える。さらに、前記装置は、前記第1の層に電気的に接続された第1及び第2のプラグを備える。さらに、前記第1の層は、前記第1のプラグと前記第2のプラグを電気的に接続する配線として機能する。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタの集積度が高い半導体装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体装置は、第1領域において上面に第1方向に延びる複数本のフィンが形成された半導体基板と、前記第1方向に対して交差した第2方向に延び、前記フィンを跨ぐ第1ゲート電極と、前記フィンと前記第1ゲート電極との間に設けられた第1ゲート絶縁膜と、前記第2領域において前記半導体基板上に設けられた第2ゲート電極と、前記半導体基板と前記第2ゲート電極との間に設けられた第2ゲート絶縁膜と、を備える。そして、前記第1ゲート電極の層構造は、前記第2ゲート電極の層構造とは異なる。

(もっと読む)

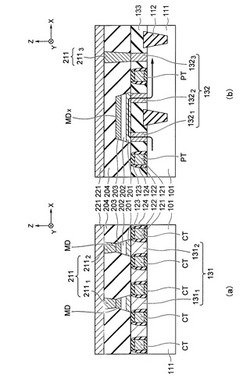

抵抗変化メモリ及びその製造方法

【課題】チップ面積の縮小を図る。

【解決手段】磁気ランダムアクセスメモリは、メモリセル部の素子領域10a上に形成された第1の拡散層17aと、第1の拡散層に接続された第1のコンタクトCB1と、第1のコンタクト上に形成された第1の下部電極層21aと、第1の下部電極層上に形成された第1の抵抗変化層22a及び第1の上部電極層23aと、周辺回路部において互いに異なる素子領域に形成された第2乃至第4の拡散層17d、17eと、第2乃至第4の拡散層に接続された第2乃至第4のコンタクトCS1、CS2と、第1の下部電極層、第1の抵抗変化層、第1の上部電極層と同じ高さに形成された第2の下部電極層21b、第2の抵抗変化層22b、第2の上部電極層23bとを具備する。第2の下部電極層は、第2及び第3のコンタクトを接続する第1のローカル配線L1として機能する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ロジック混載MRAMにおいて、LSIの多層配線形成プロセスがMRAMの特性変動を引き起こす不都合、また、MRAMの形成プロセスが多層配線の特性変動を引き起こす不都合を軽減すること。

【解決手段】多層配線層に含まれる配線層Aの中に、配線層Bに形成された第1の配線104bに接し、互いに絶縁している少なくとも2つの第1の磁化固定層50a及び50bと、2つの第1の磁化固定層50a及び50bと平面視で重なり、かつ、第1の磁化固定層50a及び50bと接続している磁化自由層10と、磁化自由層10の上に位置する非磁性層40と、非磁性層40の上に位置する第2の磁化固定層104aと、を有するMRAMが形成されている半導体装置。

(もっと読む)

半導体装置

【課題】隣接するビット線同士の短絡が抑制されており、かつ層間絶縁膜が平坦に研磨された半導体装置を提供する。

【解決手段】磁気抵抗素子MRDが複数配置されたメモリセル領域と、平面視においてメモリセル領域の周囲に配置された周辺回路領域とを備える。磁気抵抗素子MRDは、磁化固定層と磁化自由層とトンネル絶縁層とを含んでいる。磁気抵抗素子MRDの上方には、主表面に沿った方向に向けて延びる複数の第1の配線BLを有している。上記周辺回路領域には、第1の配線BLと同一レイヤにより構成される第2の配線BL2と平面視において重なるように、磁化自由層と同一材質の層、トンネル絶縁層と同一材質の層および磁化固定層と同一材質の層が積層された積層構造DMMが配置されている。積層構造DMMは、周辺回路領域にて平面視において隣接する1対の第2の配線BL2の両方と重ならない。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】MRAMにおいては、書き込み電流の低減やディスターブ回避を目的に、書き込みに使用する配線を強磁性体膜で覆うクラッド配線構造がよく用いられている。また、高信頼性製品の信頼性確保のためCu配線中に微量のAlを添加するCuAl配線が広く使用されている。MRAMも高信頼性製品に搭載される可能性が高く、信頼性は重要である。しかし、クラッド配線は、もともと配線抵抗が高いCuAl配線の配線抵抗を更に上昇させるというデメリットがあるため、両方の技術を同時に使用すると配線抵抗のスペックを満たさなくなる可能性が高い。

【解決手段】本願発明は、多層銅埋め込み配線を有する半導体装置において、MRAMメモリセルマトリクス領域を構成する複数の銅埋め込みクラッド配線の銅配線膜を比較的純粋な銅で構成し、これらの配線層よりも下層の銅埋め込み非クラッド配線の銅配線膜を、Alを添加したCuAl配線膜とするものである。

(もっと読む)

半導体装置、および、半導体装置の製造方法

【課題】磁壁移動型の磁気抵抗素子の微細化を実現する。

【解決手段】基板上に位置する第1の絶縁層24と、第1の絶縁層の24内部に位置し、互いに電気的に絶縁した一対の第1の磁化固定層20a、20bと、第1の絶縁層24上に位置し、平面視で一対の第1の磁化固定層20a、20bいずれとも重なり、かつ、一対の第1の磁化固定層20a、20bいずれとも電気的に接続している磁化自由層31と、磁化自由層31上に位置する第2の絶縁層33と、第2の絶縁層33に形成され、平面視で磁化自由層31と重なる孔と、当該孔の底面および側面に沿って形成された非磁性層41と、非磁性層41形成後の孔内に埋め込まれた第2の磁化固定層42と、を有し、第2の磁化固定層42は、平面視で一対の第1の磁化固定層20a、20bいずれとも重ならず、かつ、平面視で一対の第1の磁化固定層20a、20bの間に位置する半導体装置。

(もっと読む)

磁気記憶装置

【課題】書込み電流の増大や書込みの信用性の向上が図られた磁気記憶装置を提供する。

【解決手段】磁気記憶装置は、基板11と、基板11上に設けられたライト線WTと、ライト線WTに対して基板11の厚み方向に間隔をあけて配置され、ライト線WTの延在方向と交差する方向に延びるビット線BLと、ライト線WTおよびビット線BLの間に位置する磁気記憶素子MMとを備え、磁気記憶素子MMは、磁化方向が固定された固定層1と、外部磁界によって磁化方向が変化する記録層3とを含み、記録層3は合金膜を含み、合金膜はコバルトと鉄とホウ素とを含み、ホウ素は21at%より高い。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】上面にストラップ配線が形成された絶縁膜と、この絶縁膜の下面に形成された配線と間で剥離が生じることが抑制された半導体装置および半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置は、半導体基板SSと、半導体基板SS上に形成され、周辺配線P1および配線L2が形成された配線層LL1,LL2と、配線層LL2に形成され、配線L3を含む配線層LL3と、配線層LL3上に形成され、磁気記憶素子MRを含む配線層LL4とを備え、配線L1,L2上に形成された拡散防止膜NF1,NF2は、SiCN膜またはSiC膜から形成され、配線L3上に形成された拡散防止膜NF3は、SiNから形成される。

(もっと読む)

半導体装置および半導体装置アセンブリ

【課題】外部からの磁場を遮蔽する磁気シールド効果が高い半導体装置を提供する。

【解決手段】半導体基板SUBの主表面上に形成されたスイッチング素子TRを覆うように形成された層間絶縁膜III1と、平板状の引出配線LELと、引出配線LELとスイッチング素子TRとを接続する接続配線ICLと、磁化の向きが可変とされた磁化自由層MFLを含み、引出配線LEL上に形成された磁気抵抗素子TMRとを備える。磁化自由層MFLの磁化状態を変化させることが可能な配線DLと配線BLとを備えている。磁気抵抗素子TMRが複数並んだメモリセル領域において、磁気抵抗素子TMRの上部に配置された第1の高透磁率膜CLAD2が、上記メモリセル領域から、メモリセル領域以外の領域である周辺領域にまで延在している。

(もっと読む)

磁気記憶素子および磁気記憶装置

【課題】半選択状態になったデータの誤反転を抑制して信頼性の高い書き込み動作を行うことができる磁気記憶素子およびこれを用いた磁気記憶装置を提供する。

【解決手段】磁化容易軸91とそれに交差する磁化困難軸92とを有する記録層3と、磁化容易軸91の方向と交差する方向に磁界を形成するライト線WTと、記録層3の配置位置において磁化困難軸92の方向と交差する方向に磁界を形成するビット線BLとを備え、記録層3は、ライト線WTとビット線BLとの間に挟まれるように配置されており、ライト線WTおよびビット線BLと記録層3とが積層された積層方向からみた記録層3の平面形状は、積層方向からみてライト線WTが延びる方向に沿うライト線WTの仮想の第1の中心線AWに対して一方側に位置する一方の部分と他方側に位置する他方の部分とを有し、積層方向からみた一方の部分の面積S2が他方の部分の面積S1の1/3以下である。

(もっと読む)

不揮発性記憶装置およびその製造方法

【課題】3次元クロスポイント型の不揮発性記憶装置において、従来に比してメモリセルの面積を縮小することができる不揮発性記憶装置を提供する。

【解決手段】メモリセルMC制御用の制御素子に接続される下層配線25と、複数のワード線WLと複数のビット線BLとの交差位置に配置される複数のメモリセルMCを有するメモリセルアレイ層が、下層配線25が形成された第2の層間絶縁膜30上に複数積層されたメモリ層MLと、ワード線WLおよびビット線BLと下層配線25との間を接続するワード線およびビット線コンタクトWC,BCと、ワード線WLおよびビット線BLをワード線およびビット線コンタクトWC,BCと接続する引き出し配線部151と、を備え、引き出し配線部151は、ワード線WLとビット線BLと同じ最小寸法の配線で構成され、引き出し配線部151の上面および両側面でワード線およびビット線コンタクトWC,BCに接する。

(もっと読む)

半導体装置およびその製造方法

【課題】磁気抵抗素子の短絡不良等が軽減される半導体装置と、その製造方法とを提供する。

【解決手段】メモリセルが形成される層間絶縁膜33において、磁気抵抗素子51が形成されるメモリセル領域Mに位置する層間絶縁膜33の部分の上面の位置が、周辺領域Pに位置する層間絶縁膜33の部分の上面の位置よりも低く形成されている。磁気抵抗素子51を覆うように、層間絶縁膜40が形成されている。その層間絶縁膜40に、磁気抵抗素子に電気的に接続されるビット線41が形成されている。磁気抵抗素子51の直下にディジット線31が形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】製造プロセス中に磁性体膜の材料の拡散を防止しながら、高い磁気シールド効果を有するヘテロ構造磁気シールドを備えた半導体装置を提供する。

【解決手段】半導体装置10は、半導体基板20、半導体基板20の主面上に形成され、かつ多層配線層11Bを含む半導体素子12、および半導体素子12を被覆するヘテロ構造磁気シールド170を含む。ヘテロ構造磁気シールド170は、第一の磁気シールド積層構造16Aと磁気シールド積層構造16Aを覆う第二の磁気シールド積層構造16Bを含む。第一および第二の磁気シールド積層構造16Aおよび16Bは、いずれも、半導体素子12を被覆する磁性体からなる磁気シールド膜および半導体素子12と磁気シールド膜との間に介在し磁性体の拡散を防止するバッファ膜とを有する。

(もっと読む)

磁気記憶装置

【課題】書き込み特性の安定した磁気記憶装置を提供する。

【解決手段】第1非磁性膜2は記録層3上に設けられている。第1強磁性膜1dは、第1非磁性膜2上に設けられ、かつ第1の磁化M1dおよび第1の膜厚t1dを有する。第2非磁性膜1cは第1強磁性膜1d上に設けられている。第2強磁性膜1bは、第2非磁性膜1c上に設けられ、かつ第1強磁性膜1dと反平行結合し、かつ第2の磁化M1bおよび第2の膜厚t1bを有する。反強磁性膜1aは第2強磁性膜1b上に設けられている。第1の磁化M1dおよび第1の膜厚t1dの積と第2の磁化M1bおよび第2の膜厚t1bの積との和は、記録層の磁化M3aと記録層の膜厚t3aとの積よりも小さい。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体装置の動作不良を防止し、半導体装置の製造工程を簡略化する。

【解決手段】本発明の例に関わる半導体装置は、半導体基板1と、半導体基板1内に設けられる一対の不純物拡散層2A,2Bと、不純物拡散層2A,2B間の半導体基板上に設けられるゲート絶縁膜3と、ゲート絶縁膜3上に設けられるゲート電極4と、一対の不純物拡散層2A,2B上にそれぞれ設けられる2つのコンタクト5A,5Bとを具備し、ゲート電極4とコンタクト5A,5Bは、同じ材料から構成され、ゲート電極4上端およびコンタクト5A,5B上端は、半導体基板1表面からの高さが一致する。

(もっと読む)

半導体記憶装置の製造方法

【課題】エッチングにより離脱する窒化膜またはCap層の材質を、確実に検出可能な半導体記憶装置の製造方法を提供することを目的とする。

【解決手段】本発明に係る半導体記憶装置は、(a)下地層1,2,3,4上にTMR膜5、キャップ層6を順に積層する工程と、(b)TMR膜5、キャップ層6をパターニングして、それらの正規積層構造パターン13およびダミー積層構造パターン16を形成する工程とを備える。そして、(c)正規およびダミー積層構造パターン13,16を覆う窒化膜7を形成する工程と、窒化膜7上に酸化膜8を形成する工程と、(e)酸化膜8および窒化膜7をエッチングして、キャップ層6の上部を露出させる工程とを備える。工程(e)は、エッチングを行いながら、当該エッチングにより離脱した窒化膜7またはキャップ層6の材質を検出する。

(もっと読む)

半導体装置

【課題】多層配線に挟まれたある層の層間絶縁膜が厚薄各部分を有し、容易に製造することができる半導体装置を提供する。

【解決手段】本発明に係る半導体装置は、第1領域と第2領域を有する半導体基板と、第1領域の半導体基板上方に配置されたMTJと、MTJを覆うように配置され、第2領域上方よりも第1領域上方の膜厚が薄い絶縁膜と、絶縁膜中に配置され、MTJと電気的に接続された導電膜と、第1領域上方の絶縁膜上方に形成され、導電膜と電気的に接続されたビット線と、第2領域上方の絶縁膜上方に形成された配線と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】MTJ素子の磁性体材料の特性に悪影響を与えることなく、信頼性の高い上部配線を形成することができる半導体装置及びその製造方法を得る。

【解決手段】前処理として還元性のNH3やH2によるプラズマ処理を実施する。その後、MTJ素子に引張ストレスを印加する引張応力シリコン窒化膜55pをクラッド層53b及びクラッド層53bが形成されていない層間絶縁膜上に成膜する。続いて、MTJ素子に圧縮ストレスを印加する圧縮応力シリコン窒化膜55cを引張応力シリコン窒化膜55p上に成膜する。これらの引張応力シリコン窒化膜55p及び圧縮応力シリコン窒化膜55cの成膜条件は、平行平板型プラズマCVD装置を用いて、RFパワーは0.03〜0.4W/cm2の範囲で、成膜温度は200〜350℃の範囲にそれぞれ設定される。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、マスクを追加することなく、周辺ロジック部で形成されるクラッド配線構造の配線を1層に抑えた半導体装置及びその製造方法を提供することを目的とする。

【解決手段】本発明の1つの実施形態は、(a)クラッド配線構造を採用する第1配線が形成された層上の磁気メモリ部に磁気トンネル接合構造MTJを形成する工程と、(b)磁気メモリ部及び周辺ロジック部上に層間絶縁膜6を堆積し、磁気トンネル接合構造MTJ上の層間絶縁膜6にクラッド配線構造を採用する第2配線を形成する工程と、(c)第2配線の一部を選択的にエッチングすることで第2配線にリセス部42を形成する工程と、(d)リセス部42を利用してセルフアラインにて第2配線の上部にクラッド部41を形成する工程と、(e)クラッド部41を形成後に周辺ロジック部のロジック配線を形成する工程とを備える半導体装置を製造する方法である。

(もっと読む)

1 - 20 / 28

[ Back to top ]