Fターム[4M119KK04]の内容

MRAM・スピンメモリ技術 (17,699) | 集積又は混載技術 (507) | 半導体素子との混載技術 (194) | 混載メモリ、システムLSI (65)

Fターム[4M119KK04]に分類される特許

1 - 20 / 65

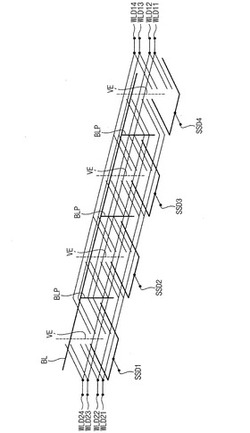

3次元半導体装置

【課題】増加された集積度を有し且つ高密度で高速の3次元(抵抗性)半導体(メモリ)装置を、最小限のマスク工程数で提供する。

【解決手段】チャンネル領域によって分離された第1及び第2不純物領域を含む基板、前記第1不純物領域に接続するビットライン、前記第2不純物領域に接続する垂直電極、前記基板と前記ビットラインとの間に配置される水平電極の積層体、及び、前記積層体と前記基板との間に配置される選択ラインを含む。この時,前記選択ラインは平面形状及び平面位置において、前記水平電極の各々と実質的に同一であり得る。

(もっと読む)

ビットライン接触面積確保のための半導体素子、その半導体素子を有するモジュール及びシステム

【課題】埋め込みゲートを有する半導体素子に関し、ビットラインコンタクトと活性領域の接触面積を増加させビットラインコンタクトの高抵抗性フェイルを防止する。

【解決手段】ビットラインコンタクト136が活性領域120の上部面だけではなく側面とも接触されることにより、ビットラインコンタクトと活性領域の接触面積を増加させビットラインコンタクトの高抵抗性フェイルを防止する。

(もっと読む)

半導体記憶装置

【課題】共通データバスを共有する複数のローカルメモリユニットが重複してデータを転送すること、あるいは、複数のローカルメモリユニットに対して重複してデータを転送することを抑制した半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、複数のメモリセルを含む複数のローカルメモリユニットLMU<0>〜LMU<7>を備える。共通データバスDBは、複数のローカルメモリユニットに共有され、複数のローカルメモリユニットからデータを転送し、あるいは、複数のローカルメモリユニットへデータを転送する。タイミングコントローラT/Cはローカルメモリユニットの単位で配置するのではなく、インターリーブ動作を行なう単位(ローカルメモリユニットLMU<0>〜LMU<7>のグループ)に対して1つ配置する。これにより読出しデータまたは書込みデータは、共通データバスDBにおいて衝突しない。

(もっと読む)

半導体装置

【課題】直流電源配線に電流が流れたか否かを検出可能な回路を備えた半導体装置を提供する。

【解決手段】半導体装置において、駆動回路BLDU,BLDD,BLBDU,BLBDDは、電流磁界またはスピン注入によってトンネル磁気抵抗素子TMR,TMRBを第1の磁化状態に初期設定するために、制御信号線BL,BLBに直流電流を流す。電源配線DLは、トンネル磁気抵抗素子TMR,TMRBに近接して設けられる。ここで、トンネル磁気抵抗素子TMR,TMRBは、電源配線DLに直流電流が流れるときに生じる電流磁界によって第2の磁化状態に変化する。センスアンプ10は、トンネル磁気抵抗素子TMR,TMRBが第1の磁化状態から第2の磁化状態に変化したか否かを判定するために、制御信号線BL,BLBを介してトンネル磁気抵抗素子TMR,TMRBに流れる電流を検出する。

(もっと読む)

磁気メモリ素子、磁気メモリ装置、スピントランジスタ、及び集積回路

【課題】 本発明の実施形態によれば、単方向電流で書き込みが可能であり、微細化が可能な磁気メモリ素子、磁気メモリ装置、スピントランジスタ、及び集積回路を提供することができる。

【解決手段】 磁気メモリ素子は、磁化が可変の第1の強磁性層と、第1のバンド及び第2のバンドを有する第2の強磁性層と、前記第1の強磁性層と前記第2の強磁性層との間に設けられた非磁性層と、を備える。

(もっと読む)

半導体記憶装置

【課題】4個のトランジスタと2個のMTJ素子からなり、電源を印加しないでも不揮発性メモリとして動作するSRAMからなる半導体記憶装置を提供する。

【解決手段】第1及び第2のインバータ2,4と第1及び第2の転送用MOSFET3,5とを含むメモリセル1からなるSRAMにおいて、第1及び第2のインバータ2,4はスピン注入型のMTJ素子6,8と駆動用MOSFET7,9とからなり、これらのインバータ2,4からフリップフロップ回路が構成され、第1及び第2のインバータ2,4の出力端子は、それぞれ第1及び第2の転送用MOSFET3,5を介してビットライン及びビットラインバーに接続され、第1及び第2の転送用MOSFET3,5のゲートは、同一のワードラインに接続される。従来のSRAMに比較してメモリセルの面積が小さく、高速で低消費電力の不揮発性メモリが得られる。

(もっと読む)

磁気トンネリング接合装置、メモリ、メモリシステム及び電子装置

【課題】磁気トンネリング接合装置を具備する半導体メモリ装置、メモリ、メモリシステム及び電子装置が提供される。

【解決手段】磁気トンネリング接合装置が提供される。この装置は磁性膜を含む第1構造体と、少なくとも2つの外因性垂直磁化構造体を含み、前記外因性垂直磁化構造体の各々は磁性膜及び前記磁性膜上の垂直磁化誘導膜を含む、第2構造体と、前記第1及び第2構造体の間のトンネルバリアと、を包含できる。前記第2構造体は追加的な外因性垂直磁化構造体をさらに含み、その各々が磁性膜及び前記磁性膜上の垂直磁化誘導膜を含んでもよい。

(もっと読む)

情報処理装置及び半導体記憶装置

【課題】製造コストの低減に対して有利な情報処理装置及び半導体記憶装置を提供する。

【解決手段】実施形態によれば、ホスト装置と、前記ホスト装置にバスを介して接続された半導体記憶装置とを備える情報処理装置であって、前記ホスト装置は、メインメモリを備え、前記半導体記憶装置は、第1の論物変換テーブル及びデータを格納する不揮発性半導体メモリと、前記第1の論物変換テーブルの一部である第2の論物変換テーブルを格納する記憶部と、前記第2の論物変換テーブルを参照し前記不揮発性半導体メモリにアクセスする制御部とを備え、前記第1の論物変換テーブルの少なくとも一部が前記メインメモリ上にコピーされ、前記第2の論物変換テーブルに前記制御部がアクセスする論理アドレス又は物理アドレスが登録されていない場合、前記メインメモリ上の第3の論物変換テーブルの一部が前記第2の論物変換テーブルにコピーされる。

(もっと読む)

信号処理回路

【課題】新たな構成の不揮発性の記憶回路を用いた信号処理回路を提供する。

【解決手段】信号処理回路は、電源電圧が選択的に供給され、第1の高電源電位が選択的に与えられる第1のノードを有する回路と、第1のノードの電位を保持する不揮発性の記憶回路とを有する。不揮発性の記憶回路は、チャネルが酸化物半導体層に形成されるトランジスタと、トランジスタがオフ状態となることによってフローティングとなる第2のノードとを有する。トランジスタはエンハンスメント型のnチャネル型のトランジスタである。トランジスタのゲートには、第2の高電源電位または接地電位が入力される。電源電圧が供給されないとき、トランジスタはゲートに接地電位が入力されてオフ状態を維持する。第2の高電源電位は、第1の高電源電位よりも高い。

(もっと読む)

半導体装置、及び半導体装置の制御方法。

【課題】簡便な半導体装置の評価試験を実現する。

【解決手段】半導体装置10は、それぞれ内部信号MAを生成する第1及び第2のコアチップCC0,CC1を備え、第1及び第2のコアチップCC0,CC1のそれぞれに、貫通電極を介して他方のコアチップとスパイラル接続された第2及び第3のノードN2,N3を設け、この第2及び第3のノードN2,N3を介して、観測対象の内部信号MAを外部に出力することを技術思想とするものである。こうして出力される複数の内部信号MAを外部のテスター等によって観測することで、各コアチップの評価試験を並列に行える。

(もっと読む)

半導体装置

【課題】メモリセルの平面視における面積を増加せずに、磁気抵抗素子の情報の読み書きに用いる電流値を低減しながら、読み書きエラーや磁気抵抗素子間の短絡が抑制された集積回路を有する半導体装置を提供する。

【解決手段】半導体基板の主表面上に配置された、電流の流れる向きに応じて磁化状態を変化させることが可能な、スピントルク書き込み方式の面内磁化型の磁気抵抗素子MRDと、磁気抵抗素子MRDと電気的に接続され、主表面に沿った方向に向けて延びる第1配線BLとを備える。上記磁気抵抗素子MRDは平面視におけるアスペクト比が1以外の値である。上記磁気抵抗素子MRDとスイッチング素子とが電気的に接続されたメモリセルMCが複数並んだメモリセル領域において、平面視における磁気抵抗素子MRDの長手方向に関して、隣接する複数の磁気抵抗素子MRDが、上記長手方向に沿って延在する同一直線上に乗らないように配置される。

(もっと読む)

半導体装置

【課題】隣接するビット線同士の短絡が抑制されており、かつ層間絶縁膜が平坦に研磨された半導体装置を提供する。

【解決手段】磁気抵抗素子MRDが複数配置されたメモリセル領域と、平面視においてメモリセル領域の周囲に配置された周辺回路領域とを備える。磁気抵抗素子MRDは、磁化固定層と磁化自由層とトンネル絶縁層とを含んでいる。磁気抵抗素子MRDの上方には、主表面に沿った方向に向けて延びる複数の第1の配線BLを有している。上記周辺回路領域には、第1の配線BLと同一レイヤにより構成される第2の配線BL2と平面視において重なるように、磁化自由層と同一材質の層、トンネル絶縁層と同一材質の層および磁化固定層と同一材質の層が積層された積層構造DMMが配置されている。積層構造DMMは、周辺回路領域にて平面視において隣接する1対の第2の配線BL2の両方と重ならない。

(もっと読む)

磁気デバイスおよびその製造方法

【課題】複数のトンネル接合素子の間隔を短縮すること。

【解決手段】上面に凹部26が形成された下地層24と、前記凹部の内面と前記凹部の両側の下地層上とに形成された下部電極28と、前記凹部の両側の前記下部電極上に形成され、トンネルバリア層と前記トンネルバリア層を上下に挟む磁化固定層および磁化自由層とを含む磁気トンネル接合層30と、前記磁気トンネル接合層上に形成され、前記凹部の上方において電気的に分離された複数の上部電極40と、を具備する磁気デバイス。

(もっと読む)

集積磁気薄膜増強回路素子を有する磁気抵抗ランダムアクセスメモリ(MRAM)

磁気抵抗素子および半導体メモリ

【課題】 書き込み電流のマージンとリテンションのマージンとを両方確保する。

【解決手段】 磁気抵抗素子は、第1固定層、第1トンネル絶縁膜および第1自由層が積層される第1強磁性トンネル接合素子と、第2固定層、第2トンネル絶縁膜および第2自由層が積層され、第1強磁性トンネル接合素子に直列に接続される第2強磁性トンネル接合素子とを有している。第1固定層、第1トンネル絶縁膜および第1自由層の積層方向は、第2固定層、第2トンネル絶縁膜および第2自由層の積層方向と逆である。第1トンネル絶縁膜の厚さは、第2トンネル絶縁膜の厚さと異なり、第1強磁性トンネル接合素子および第2強磁性トンネル接合素子は、共通のマスク材料を用いてエッチングにより形成される。これにより、第1自由層および第2自由層の横断面の面積および体積を互いにほぼ同じにでき、書き込み電流を共通に設定できる。

(もっと読む)

磁気抵抗素子、半導体メモリおよび磁気抵抗素子の製造方法

【課題】 エッチング時間を長くすることなく、トンネル絶縁膜の汚染を防止し、磁気抵抗素子の電気的特性の悪化を防止する。

【解決手段】 磁気抵抗素子は、半導体基板上に配置される固定層と、固定層上に配置されるトンネル絶縁膜と、トンネル絶縁膜上に配置され、Feを含む第1自由層と、第1自由層上に配置され、FeおよびTaを含む第2自由層と、第2自由層上に配置され、Ruを含むストッパー層とストッパー層上に配置されるハードマスクとを有している。第1自由層とストッパー層との間隔を第2自由層により大きくできるため、ストッパー層のRuがトンネル絶縁膜に付着することを防止でき、ストッパー層のRuが第1自由層の界面に現れることを防止できる。この結果、エッチング時間を長くすることなく、トンネル絶縁膜の汚染を防止でき、磁気抵抗素子の電気的特性の悪化を防止できる。

(もっと読む)

半導体装置

【課題】メモリ素子の信頼性と消費電流の抑制を両立させることができる半導体装置を提供する。

【解決手段】半導体装置は、複数の磁気メモリセルMCと、複数のディジット線DLと、ディジット線ドライブ回路28Bと、ビット線BL[0:95」とを備える。複数のビット線BL[0:95」は、たとえば12本ごとの複数の群に分割される。半導体装置は、複数のビット線の各々を少なくとも2段階の強度で駆動可能に構成されたビット線ドライブ回路22L,22Rとをさらに備える。ビット線ドライブ回路22L,22Rは、書込群に対しては、書込データに対応する極性の電流で2段階のうち強い強度でビット線を駆動し、非書込群に対しては、2段階のうち弱い強度で自分自身のデータに対応する極性のデータ保持電流を流す。

(もっと読む)

半導体装置

【課題】電源電圧の変動に起因した書込電流の変動を抑制する。

【解決手段】ドライブ回路25において、第1のMOSトランジスタPMは、第1および第2の電源ノード28,29間にデータ書込線DLと直列に設けられる。第2のMOSトランジスタPSは、第1のMOSトランジスタPMと並列に設けられる。第3および第4のMOSトランジスタPa,Pbは、互いに同じ電流電圧特性を有する。第1の素子Eaは、第1および第2の電源ノード28,29間に第3のMOSトランジスタPaと直列に接続される。第2の素子Ebは、第1および第2の電源ノード28,29間に第4のMOSトランジスタPbと直列に接続され、第1の素子Eaの電流電圧特性曲線と交差する電流電圧特性を有する。比較器30は、第1の素子Eaにかかる電圧と第2の素子Ebにかかる電圧とを比較し、比較結果に応じて第2のMOSトランジスタPSをオンまたはオフにする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】MRAMにおいては、書き込み電流の低減やディスターブ回避を目的に、書き込みに使用する配線を強磁性体膜で覆うクラッド配線構造がよく用いられている。また、高信頼性製品の信頼性確保のためCu配線中に微量のAlを添加するCuAl配線が広く使用されている。MRAMも高信頼性製品に搭載される可能性が高く、信頼性は重要である。しかし、クラッド配線は、もともと配線抵抗が高いCuAl配線の配線抵抗を更に上昇させるというデメリットがあるため、両方の技術を同時に使用すると配線抵抗のスペックを満たさなくなる可能性が高い。

【解決手段】本願発明は、多層銅埋め込み配線を有する半導体装置において、MRAMメモリセルマトリクス領域を構成する複数の銅埋め込みクラッド配線の銅配線膜を比較的純粋な銅で構成し、これらの配線層よりも下層の銅埋め込み非クラッド配線の銅配線膜を、Alを添加したCuAl配線膜とするものである。

(もっと読む)

不揮発性記憶装置

【課題】電源投入後、高速なセットアップが可能な不揮発性記憶装置を提供する。

【解決手段】不揮発性記憶装置は、データを不揮発的に記憶するメモリセルを有する第1および第2のメモリモジュール16−1、16−2と、第1および第2のメモリモジュールとそれぞれ接続されて、前記第1および第2のメモリモジュールを駆動するための外部電源を供給する第1および第2の外部電源線VL11、VL12とを備え、第1の外部電源線の電源容量C1は、前記第2の外部電源線の電源容量C2よりも小さい。

(もっと読む)

1 - 20 / 65

[ Back to top ]