Fターム[4M119KK12]の内容

MRAM・スピンメモリ技術 (17,699) | 集積又は混載技術 (507) | ダミーセル,ダミー配線 (76)

Fターム[4M119KK12]に分類される特許

1 - 20 / 76

半導体装置

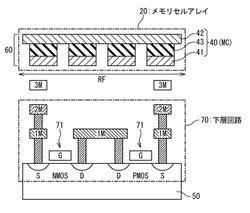

【課題】抵抗変化素子を備える半導体装置(半導体チップ)のチップ面積を削減すること。

【解決手段】半導体装置(1)は、半導体基板(50)上に形成されたトランジスタ(71)を含む下層回路(70)と、半導体基板(50)の上方の配線層(60)に形成されたメモリセルアレイ(20)と、を備える。メモリセルアレイ(20)の各メモリセル(MC)は、配線層(60)に形成された抵抗変化素子(40)を記憶素子として備る。メモリセルアレイ(20)は、メモリセル(MC)の直下に当該メモリセル(MC)との電気的接続用のビアが形成されていない第1領域(RF)を有している。下層回路(70)は、第1領域(RF)の少なくとも一部とオーバーラップするように配置されている。

(もっと読む)

磁気抵抗効果素子

【課題】磁気メモリの動作不良を抑制する。

【解決手段】本実施形態の磁気抵抗効果素子は、垂直磁気異方性を有し、磁化の向きが可変な記憶層と、垂直磁気異方性を有し、磁化の向きが不変な参照層と、記憶層と参照層との間の非磁性層11と、磁化の向きが不変なシフト調整層と、を含む。参照層は第1の磁化温度依存性LM1を有し、シフト調整層は参照層と異なる第2の磁化温度依存性LM2を有する。メモリ動作温度下において、参照層の漏れ磁場とシフト調整層の漏れ磁場とは互いにキャンセルされ、実装温度下において、参照層の漏れ磁場及びシフト調整層のうち一方に起因するシフト磁界が、記憶層の磁化に印加される。

(もっと読む)

磁気メモリ

【課題】磁気メモリの動作不良を抑制する。

【解決手段】本実施形態の磁気メモリは、第1領域内の第1の磁気抵抗効果素子1Aと、第2の領域の磁気抵抗効果素子1Xとを含む。第1の磁気抵抗効果素子1Aは、磁化の向きが可変な第1の記憶層10と、磁化の向きが不変な第1の参照層12と、非磁性層11と、第1のシフト調整層13と、を含む。第2の磁気抵抗効果素子1Xは、磁化の向きが可変な第2の記憶層10と、磁化の向きが不変な第2の参照層12と、第2の非磁性層11と、第2のシフト調整層13Xと、を含む。第2のシフト調整層13Xの膜厚t2は、第1のシフト調整層13の膜厚t1以下である。

(もっと読む)

3次元ダブルクロスポイントアレイを有する半導体メモリ素子及びその製造方法

【課題】単純な方式で集積度が向上し電気的特性が改善された3次元ダブルクロスポイントアレイを有する半導体メモリ素子及びその製造方法を提供する。

【解決手段】本発明の半導体メモリ素子は、互いに異なるレベルに配置され、2つの交差点を定義する第1、第2、及び第3導線と、2つの交差点の各々に配置される2つのメモリセルを備え、第1及び第2導線は互いに平行に延長され、第3導線は延長されて第1及び第2導線と交差し、第1及び第2導線は垂直断面で見た時に第3導線の長さに沿って交互に配列され、第3導線は第1及び第2導線から垂直に離隔される。

(もっと読む)

磁気記憶装置及び磁気記憶装置の製造方法

【課題】 基準素子の抵抗値のばらつきを抑制することが望まれている。

【解決手段】 基板上に磁気抵抗素子及び基準素子が形成されている。磁気抵抗素子は、トンネル絶縁層を自由磁化層と固定磁化層とで挟んだ構造を有し、自由磁化層の磁化方向によって低抵抗状態と高抵抗状態との間で抵抗が変化し、第1の方向に長い平面形状を有する。基準素子は、トンネル絶縁層を自由磁化層と固定磁化層とで挟んだ構造を有し、磁気抵抗素子の低抵抗状態の抵抗と高抵抗状態の抵抗との間の抵抗を有し、第1の方向と直交する第2の方向に長い平面形状を有する。

(もっと読む)

磁気メモリデバイスの駆動方法及び磁気メモリデバイス

【課題】基準素子におけるディスターバンスの発生を防止することができる磁気メモリデバイスを提供する。

【解決手段】基準セル28が、基準素子20を含む。基準素子は、固定磁化層21、絶縁層22、自由磁化層23を含み、自由磁化層の磁化方向は固定磁化層の磁化方向と反平行であり、メモリセル18の磁気抵抗素子10が平行状態のときの抵抗値と反平行状態のときの抵抗値との間の抵抗値を有する。基準素子に、基準素子の固定磁化層から自由磁化層に向かう読出電流を流し、磁気抵抗素子の抵抗値と、基準素子の抵抗値との大小関係に依存する物理量を検出することにより、情報の読出しを行う。

(もっと読む)

半導体記憶装置

【課題】データの読み出しマージンの改善を図ることが可能な半導体記憶装置を提供する。

【解決手段】制御回路は、複数の第1のメモリセルの全てに抵抗値が大きくなる同じ第1の論理を記憶させた状態で、選択トランジスタをオンして流れる読み出し電流が一番大きくなる第1のメモリセルを第1の参照セルとして第1のセルアレイから選定する。制御回路は、複数の第2のメモリセルの全てに抵抗値が大きくなる同じ第1の論理を記憶させた状態で、選択トランジスタをオンして流れる読み出し電流が一番大きくなる第2のメモリセルを第2の参照セルとして第2のセルアレイから選定する。第1の参照電流設定回路は、第1の参照セルの読み出し電流に第1の調整電流を加算して得られた電流を第1の参照電流として設定する。第2の参照電流設定回路は、第2の参照セルの読み出し電流に第2の調整電流を加算して得られた電流を第2の参照電流として設定する。

(もっと読む)

磁気メモリ及びその製造方法

【課題】磁気抵抗素子間での電気的特性のバラツキを低減する。

【解決手段】磁気メモリの製造方法は、半導体基板20上のセルアレイ部に磁気抵抗素子37を形成する工程と、半導体基板20上の周辺回路部に、磁気抵抗素子37と同じ積層構造を有しかつ磁気抵抗素子37と同じレベルに配置されたダミー素子68を形成する工程と、磁気抵抗素子37及びダミー素子68を一括して平坦化する工程と、ダミー素子68にレーザー光線を照射し、ダミー素子68を非磁性体化する工程と、平坦化された磁気抵抗素子37上に上部電極41を形成する工程とを含む。

(もっと読む)

磁気ランダムアクセスメモリ及びその動作方法

【課題】読み出し時の誤書き込みのリスクをより抑制し、かつ、より正確な読み出しを可能とする。

【解決手段】磁気ランダムアクセスメモリは、スピン注入により変更される自由強磁性層の磁化の向きでデータを書き込み可能な第1磁気抵抗素子を含むメモリセルと、スピン注入により変更される自由強磁性層の磁化の向きでリファレンス用データを記憶する複数の第2磁気抵抗素子を含み、メモリセルの読み出し動作時に用いられるリファレンスセルとを具備する。複数の第2磁気抵抗素子は、互いに直列に接続され、自由強磁性層の磁化の向きが互いに逆の向きで、固定強磁性層の磁界の向きが互いに同じ向きで、固定強磁性層同士又は自由強磁性層同士が電気的に接続されている。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】孤立パターンに銅の化合物が析出するのを抑制する半導体装置の製造方法と、半導体装置とを提供する。

【解決手段】半導体装置では、素子・基板層ESLの低誘電率膜LOW1、ファイン層FLの極低誘電率膜ELK1等およびセミグローバル層SGLの低誘電率膜LOW2等のそれぞれの開口部に形成されるアライメントマークAMおよび重ね合わせ検査マークKMが、半導体基板SUBに形成された所定の導電型の不純物領域IRに電気的に接続されて、アライメントマークAMおよび重ね合わせ検査マークKMが接地電位に固定されている。

(もっと読む)

半導体装置

【課題】隣接するビット線同士の短絡が抑制されており、かつ層間絶縁膜が平坦に研磨された半導体装置を提供する。

【解決手段】磁気抵抗素子MRDが複数配置されたメモリセル領域と、平面視においてメモリセル領域の周囲に配置された周辺回路領域とを備える。磁気抵抗素子MRDは、磁化固定層と磁化自由層とトンネル絶縁層とを含んでいる。磁気抵抗素子MRDの上方には、主表面に沿った方向に向けて延びる複数の第1の配線BLを有している。上記周辺回路領域には、第1の配線BLと同一レイヤにより構成される第2の配線BL2と平面視において重なるように、磁化自由層と同一材質の層、トンネル絶縁層と同一材質の層および磁化固定層と同一材質の層が積層された積層構造DMMが配置されている。積層構造DMMは、周辺回路領域にて平面視において隣接する1対の第2の配線BL2の両方と重ならない。

(もっと読む)

半導体記憶装置

【課題】 スピン注入磁化反転を用いた磁性体メモリにおいて、微細な磁気抵抗素子を用いると書き込み電流が低減できるが、読み出し時のデータ破壊を防止するために読み出し電流も小さくする必要があり、読み出し動作の遅延につながる。

【解決手段】 ワード線(WL)が選択された後に、センスアンプ(SA)が活性化されて第1ビット線(BLt0)が第1電位(VDD)に、第2ビット線(BLb0)が第2電位(VSS)に駆動され、その後、ソース線(SL0)が第1電位から第2電位に駆動されることにより、時分割で反平行状態と平行状態の再書き込み動作を行う。

(もっと読む)

半導体装置

【課題】メモリ素子の信頼性と消費電流の抑制を両立させることができる半導体装置を提供する。

【解決手段】半導体装置は、複数の磁気メモリセルMCと、複数のディジット線DLと、ディジット線ドライブ回路28Bと、ビット線BL[0:95」とを備える。複数のビット線BL[0:95」は、たとえば12本ごとの複数の群に分割される。半導体装置は、複数のビット線の各々を少なくとも2段階の強度で駆動可能に構成されたビット線ドライブ回路22L,22Rとをさらに備える。ビット線ドライブ回路22L,22Rは、書込群に対しては、書込データに対応する極性の電流で2段階のうち強い強度でビット線を駆動し、非書込群に対しては、2段階のうち弱い強度で自分自身のデータに対応する極性のデータ保持電流を流す。

(もっと読む)

薄膜磁性体記憶装置

【課題】高集積化に適したメモリセル配置、特に折り返し型ビット線構成に適したメモリセル配置を有する薄膜磁性体記憶装置を提供する。

【解決手段】メモリアレイにおいて、1個のメモリセルMCと対応する繰り返し単位140aが連続的に配置されて、メモリセルMCが行列状に配置される。隣接するメモリセル列間で、繰り返し単位140aは、1/2ピッチ(ハーフピッチ)分だけずらして配置される。ビット線BL1およびBL2は同一のビット線対を構成し、ビット線BL2はデータ読出時において、ビット線BL1の相補線/BL1として動作する。選択されたリードワード線RWLに対応して、1本おきのビット線にメモリセルが接続されるので、セルサイズを増加させることなく折返し型ビット線構成に基づくデータ読出に適したメモリセル配置を実行できる。

(もっと読む)

薄膜磁性体記憶装置

【課題】製造時ばらつきに対応して、データ読出時における高い信号マージンを確保可能な薄膜磁性体記憶装置を提供する。

【解決手段】ダミーメモリセルDCPは、2個のセルユニットCU0およびCU1を含む。各セルユニットCU0,CU1は、メモリセルと同様の構成を有し、ビット線BLと接地電圧Vssとの間に直列に結合された、トンネル磁気抵抗素子TMRおよびアクセストランジスタATRを有する。セルユニットCU0,CU1に対しては、異なる記憶データ“0”および“1”がそれぞれ書込まれる。データ読出時において、2個のセルユニットCU0,CU1が、読出参照電圧Vrefを伝達するためのビット線BLと接地電圧Vssとの間に並列に接続される。さらに、ダミーメモリセルDCPに対して、電流供給回路52からメモリセルに供給されるセンス電流Isの2倍、すなわち2・Isの一定電流が供給される。

(もっと読む)

半導体記憶装置

【課題】 チップ面積を増加することなく、フューズセルを実現する。

【解決手段】 実施形態による半導体記憶装置は、第1セルアレイ10−1内に配置された第1参照セルRCと、第1セルアレイ10−1内に配置され、第1参照セルRCが配置されたロウ又はカラムと同一のロウ又はカラムに並べられた複数の第1フューズセルFCと、を具備する。

(もっと読む)

不揮発性半導体記憶装置

【課題】メモリセルのトランジスタの配置効率が高い不揮発性半導体記憶装置を提供する。

【解決手段】このMRAMでは、各メモリセルMCのアクセストランジスタを2つのトランジスタQA,QBに分割し、トランジスタQA,QBのゲートをそれぞれワード線WLA,WLBに接続し、奇数番のメモリブロックMBのワード線WLA,WLBを主ワード線MWLAに接続し、偶数番のメモリブロックMBのワード線WLA,WLBを主ワード線MWLBに接続する。したがって、メモリセルMCのトランジスタの配置効率を高めることができる。

(もっと読む)

半導体集積回路装置

【課題】設計工数をほとんど掛けないで、CMP対策及び短時間光アニール対策の両対策に最適化されたダミーパターンを有する半導体集積回路装置を提供すること。

【解決手段】基板上に、メモリマクロ領域10及び機能回路領域20を有する半導体集積回路装置1において、機能回路領域20間、及び、メモリマクロ領域10と機能回路領域20との間に配置されるとともにダミーパターン41を含むダミーパターン領域40を備え、ダミーパターン41は、前記メモリセルアレイ領域におけるメモリセルパターン11の拡散層12、13及びゲート電極14と同等のパターンであり、ダミーパターン領域40におけるダミー拡散層42、43及びダミーゲート電極44の面積率は、メモリセルアレイ領域における拡散層12、13及びゲート電極14の面積率と同等以上である。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】上面にストラップ配線が形成された絶縁膜と、この絶縁膜の下面に形成された配線と間で剥離が生じることが抑制された半導体装置および半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置は、半導体基板SSと、半導体基板SS上に形成され、周辺配線P1および配線L2が形成された配線層LL1,LL2と、配線層LL2に形成され、配線L3を含む配線層LL3と、配線層LL3上に形成され、磁気記憶素子MRを含む配線層LL4とを備え、配線L1,L2上に形成された拡散防止膜NF1,NF2は、SiCN膜またはSiC膜から形成され、配線L3上に形成された拡散防止膜NF3は、SiNから形成される。

(もっと読む)

抵抗変化メモリ

【課題】メモリセルアレイの面積を縮小する。

【解決手段】抵抗変化メモリ10は、第1の方向に延在する複数のビット線BLと、第2の方向に延在する複数のワード線WLと、複数のメモリセルMCを備えたメモリセルアレイ11とを含む。各メモリセルMCは、可変抵抗素子21と選択トランジスタ22とを有し、可変抵抗素子21の第1の端子は第1のビット線に接続され、可変抵抗素子21の第2の端子は選択トランジスタ22のドレインに接続され、選択トランジスタ22のソースは第2のビット線に接続され、選択トランジスタ22のゲートはワード線に接続される。第1の方向に順に並んだ第1乃至第4の可変抵抗素子のレイアウトにおいて、第1及び第2の可変抵抗素子は1本のワード線を挟み、第2及び第3の可変抵抗素子は2本のワード線を挟み、第3及び第4の可変抵抗素子は1本のワード線を挟む。

(もっと読む)

1 - 20 / 76

[ Back to top ]