Fターム[5B011DC01]の内容

Fターム[5B011DC01]の下位に属するFターム

構成制御レジスタ (10)

Fターム[5B011DC01]に分類される特許

21 - 40 / 65

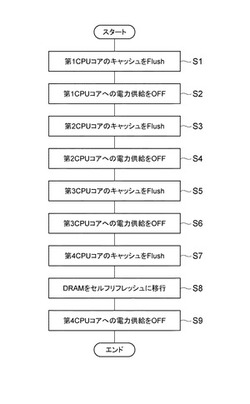

マルチプロセッサシステム

【課題】キャッシュ状態のバックアップ時の電力消費を低減するマルチプロセッサシステムを提供することを課題とする。

【解決手段】キャッシュをそれぞれ備える複数のプロセッサを有し、システム停止時に各プロセッサのキャッシュの状態を外部記憶装置に順次保存するマルチプロセッサシステムであって、複数のプロセッサへの給電を管理する給電管理手段を備え、給電管理手段は、システム停止時に、複数のプロセッサの任意のプロセッサのキャッシュの状態の外部記憶装置への保存が完了する毎に、任意のプロセッサの次にプロセッサのキャッシュの状態を保存するプロセッサのキャッシュの状態の外部記憶装置への保存が完了する前に、任意のプロセッサへの給電を停止することを特徴とする。

(もっと読む)

半導体装置

【課題】LSI内部に不揮発性記憶素子が不要で、電源ICを制御するファームウェア、電源ICとLSI間の通信が不要で、LSI側のピンを削減でき、開発、検証コストを抑えつつ、最適な電源電圧供給を実現することが可能な半導体装置を提供する。

【解決手段】遅延情報に応じた電源電圧を発生する電源電圧発生回路(電源IC)13と、電源IC13から電源電圧が供給される集積回路(LSI)12と、を有し、LSI12は、電源IC13から電源電圧が供給されて動作するときの遅延情報をモニタする遅延情報モニタ121を含み、電源IC13は、遅延情報モニタ121による遅延情報に関連する遅延情報を保持可能な遅延情報レジスタ131と、遅延情報レジスタ131に保持された遅延情報に応じた電源電圧を発生してLSI12に供給する電圧制御回路133と、を含む。

(もっと読む)

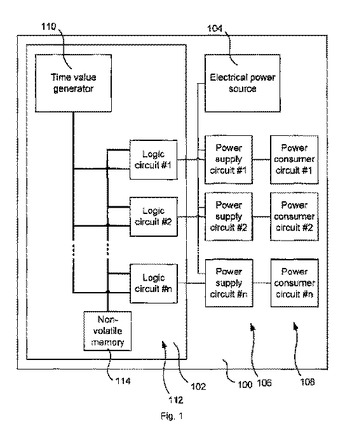

電源始動機構、電源回路の起動を制御する装置及び方法

複数の電源回路の起動を所定のタイミングで制御する電源始動順序付け機構が開示される。機構は、時間値信号を供給するように構成された時間値発生器と、電源回路ごとに設けられ、時間値信号を受信し且つ受信された時間値信号から対応する電源回路に起動信号をそれぞれ供給するように構成された論理回路とを備え、各論理回路は、各電源回路の始動タイミング値と関連付けられるため、関連付けられた始動タイミング値が受信された時間値信号と一致した場合に起動信号が供給される。そのような機構を備える装置及び複数の電源回路の起動を制御する方法も開示される。  (もっと読む)

(もっと読む)

情報処理装置、正当性検証方法及びプログラム

【課題】ハイバネーションによる起動であっても、ソフトウェアの正当性を正しく検証可能な情報処理技術を提供する。

【解決手段】TPM登録処理では、BIOS20は、ハイバネーションイメージを生成する際に、これとコンテキスト情報とを用いてハッシュ値を計算してPCR53へ登録する。TPM5は、通常の起動時のためのPCR51〜PCR53のハッシュ値の組み合わせと、ハイバネーションによる起動時のためのPCR51,PCR53のハッシュ値の組み合わせと、暗号鍵とを含むブロブを生成する。正当性検証処理では、BIOS20は自身のハッシュ値を計算しこれをPCR51へ登録し、ハイバネーションイメージ及びコンテキスト情報のハッシュ値を計算してPCR53に登録する。TPM5は、ブロブと、PCR51,PCR53に各々登録されているハッシュ値とを用いて、ブロブに含まれる暗号鍵の取り出しを許可するか否かを判断する。

(もっと読む)

半導体集積回路、省電力制御方法、省電力制御プログラム及び記録媒体

【課題】本発明は、省電力モード処理の処理時間の短縮化を図った半導体集積回路、省電力制御方法、省電力制御プログラム及び記録媒体に関する。

【解決手段】ASIC2は、省エネモードへの移行時に、省エネモード時に電源の供給が停止される機能モジュール11、12のレジスタのパラメータ及びPCIeコントローラ13のレジスタのパラメータを、ASIC2内のパラメータDMAC18によって、省エネモード時においても記憶内容を保持する不揮発性メモリ17に転送して書き込み、省エネ復帰要因検知モジュール15が省エネモードからの復帰要因を検知すると、パラメータDMAC18によって不揮発性メモリ17のパラメータを機能モジュール11、12及びPCIeコントローラ13のレジスタに転送して書き戻す。

(もっと読む)

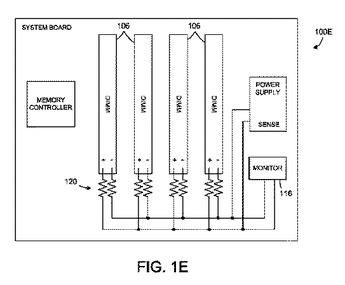

電圧センス監視インターフェースを備えたメモリモジュール

メモリデバイス及びシステムは、可変負荷にわたる電圧許容誤差に対処するための電圧センスラインを含む。該メモリデバイス及びシステムは、メモリモジュール上の回路構成に結合された第1の複数ピンと、該メモリモジュール上の電力レールに結合された第2の複数ピンとを有したメモリモジュールコネクタを備える。該第2の複数ピンは、外部から該メモリモジュールへの該電力レールの監視を可能にする。  (もっと読む)

(もっと読む)

省電力記憶装置とこれを備えた情報処理装置、記憶装置の省電力制御方法及びプログラム

【課題】故障等の障害のあるメモリにおける無駄な電力消費を排除し、装置全体として消費電力を大幅に低減する。

【解決手段】複数のRAM(メモリ)2−0−2−00〜2−0−2−10と、書き込みデータ/読み出しデータの分配/編集を行うデータ分配回路2−0−1と、上位装置からのリクエストに応じてRAM制御信号(メモリ制御信号)を生成し、各RAM2−0−2−00〜2−0−2−10に送出するRAM制御信号生成回路2−0−0と、を備え、RAM制御信号生成回路2−0−0が、故障したRAMを個別に省電力制御する省電力制御回路11−0〜11−10を備える。

(もっと読む)

リアルタイムクロック、およびリアルタイムクロックのデータ記録方法

【課題】記憶されたイベントデータの信頼性を向上させることのできるリアルタイムクロックを提供する。

【解決手段】上記課題を解決するためのリアルタイムクロック10は、イベント検出信号が外部から入力されたことを検出するイベント検出回路20と、発振回路16から出力された信号に基づいて前記時刻データを生成する計時回路18と、メモリ40と、イベント検出回路20により前記イベント検出信号の入力を検出した場合、リアルタイムクロック10の動作状態を示す付加データと、計時回路18により生成された前記時刻データとを有するイベントデータをメモリ40に記録する制御回路42と、を備えたことを特徴とする。

(もっと読む)

半導体集積回路装置

【課題】外部装置側の電源電圧の低下に伴う処理を安定に行う。

【解決手段】外部の電源に接続する電源端子11と、電源端子11における電源電圧の絶対値が所定の値以上であるか否かを検出する電圧検出回路12と、電源電圧の絶対値が所定の値未満である場合にその旨の情報を保持するレジスタ13と、レジスタ13に保持された情報を外部から読み出し可能とする出力端子15と、を備える。

(もっと読む)

画像形成装置、プログラム、及び方法

【課題】 外部アプリケーションを任意の媒体や領域にインストールした場合に外部アプリケーションの起動を選択的に行い、多種多様な機能を提供すること。

【解決手段】 画像形成処理に関するシステム側の処理を行うサービスモジュールを有し、当該サービスモジュールとは別にアプリケーションを搭載可能に構成された画像形成装置において、アプリケーションを格納した少なくとも1つの場所を示す起動選択情報を参照し、当該起動選択情報に従って前記少なくとも1つの場所からアプリケーションを起動するアプリケーション起動手段を備えた。

(もっと読む)

半導体集積回路装置

【課題】チップ形状についての制約が大きく内部電源配線抵抗を低抵抗化する視点から最適なレイアウトができない場合でも、RAM回路ブロックの性能が悪化しないこと。

【解決手段】本発明の半導体集積回路装置は、複数のRAM(Random Access Memory)回路ブロック(RAM1〜RAMn)に分割されたRAM回路と、内部電源回路(10)と、を具備している。内部電源回路(10)は、複数のRAM回路ブロック(RAM1〜RAMn)のうちの選択RAM回路ブロックが選択されたとき、選択RAM回路ブロックの配置場所に応じた電圧を出力電圧(VINT1’)として選択RAM回路ブロックに供給する。

(もっと読む)

マイクロコンピュータ及びマイクロコンピュータの外部レジスタデータ処理方法

【課題】低消費電力モードに移行した場合の消費電流の検査を、より簡単にできるマイクロコンピュータを提供する。

【解決手段】CPU2は、スリープモードに移行する直前に、レジスタ4のデータをメモリ5に退避させ、スリープ/ウェイクアップ制御部6は、スリープモードに移行するとレジスタ4をリセットして初期化する。そして、CPU2は、スリープモードから通常動作モードに移行した直後に、メモリ5に退避させたデータをレジスタ4に復帰させる。

(もっと読む)

計算機システムおよび計算機システムのメモリ管理方法

【課題】 ハードディスクやフラッシュメモリが存在しないシステムにおいても適用可能なメモリ管理技術を提供する。

【解決手段】 複数のメモリバンクから構成される主記憶装置を有し、前記主記憶装置上のメモリ領域の割り当ておよび解放を管理する計算機システムにおいて、サスペンド時に、メモリ領域の割り当ておよび解放の状況に基づいて特定のメモリバンクにデータをコピーして集め、特定のメモリに該データが入りきらない場合は、使用頻度の低いページを圧縮して格納し、そのメモリバンク以外のメモリバンクに対してその節電のための制御を行うメモリ節電手段を具備することを特徴とする計算機システム。

(もっと読む)

メモリコントローラ

【課題】 DDRタイプのメモリ素子を使用して、高いパフォーマンスと低消費電力化を両立する。

【解決手段】高速動作が要求されない場合においては、DLL回路に供給するリファレンスクロック信号を固定したまま、メモリモジュールに供給するクロック信号の周波数を低くすることによって、システム全体の低消費電力化を達成する。高速動作が要求される場合においては、DLL回路に供給するリファレンスクロック信号と同じ周波数のクロック信号をメモリモジュールに供給することで、高いパフォーマンスを達成する。

(もっと読む)

半導体デバイスおよび複数の相互接続デバイスを有するシステムの電力消費を低減するための方法

システムは、メモリコントローラと通信する直列接続された複数のメモリデバイスを備える。ID番号によって指定されたメモリデバイスは、通常の電力消費レベルでの動作を実行する。指定されていないデバイスは、少ない電力消費で信号転送動作を実行する。指定されたメモリデバイスは、内部クロック発生器をイネーブルし、動作に必要な全クロックを生成する。指定されていないメモリデバイスは、次のメモリデバイスにコマンドを転送するための部分動作用のクロックを生成する。他の実施例ではメモリデバイスは、IDが一致しない場合、次のメモリデバイスに入力コマンドを転送しない。他の実施例ではメモリデバイスは、IDが一致している場合、コマンドの内容を静的な出力に置換しコマンドを伝送する。このような部分クロックの発生、コマンドの非転送及びコマンド内容の置換により、システムは少ない電力消費で動作する。  (もっと読む)

(もっと読む)

内部レジスタ情報記録装置および画像処理装置

【課題】別途CPUを設けることなく装置に異常が発生した際にシステムがどのように動作していたのかを示す履歴情報を生成する。

【解決手段】CPU101は、画像処理装置1の動作モードを通常動作モードと省エネモードの間で双方に切り換えるにあたり、予め各ユニットが有する内部レジスタに書き込まれている情報をBack Up SRAM105に書き込む。その結果、仮に画像処理装置1に異常が生じても、その直前の動作状況を示すレジスタ情報がBack Up SRAM105に保存されているため、その情報を読み出し異常の原因解析に役立てることができる。

(もっと読む)

フィールド機器

【課題】電力を供給する伝送線路に接続され、演算処理を実行し外部機器と通信を行うフィールド機器において、伝送線路から供給される電流と演算処理に対する動作クロック周波数を可変して、低消費電力用または高速演算処理用を1種類の構成で実現するフィールド機器を提供すること。

【解決手段】電力を供給する伝送線路に接続され、演算処理を実行し外部機器と通信を行うフィールド機器において、前記伝送線路から供給される電流と前記演算処理に対する動作クロック周波数を、少なくとも2段階に可変するための設定データを出力する設定部と、前記設定データに基づき前記伝送線路から供給される電流を可変する電流可変部と、前記設定データに基づき前記演算処理に対する動作クロック周波数を可変する周波数可変部を備えた、ことを特徴とするもの。

(もっと読む)

システムオンチップ

【課題】システムオンチップがスリープモードであっても低電力が実現できるリテンション入出力装置を含むシステムオンチップを提供する。

【解決手段】ノーマルNモード時入出力状態を決定する第1入出力制御信号、スリープSモード時入出力状態を決定する第2入出力制御信号、ノーマル値、及びスリープ値を生成する制御部、第1、第2入出力制御信号、ノーマル値、スリープ値を格納する第1〜第4レジスタ、第1、第2入出力制御信号の何れかを選択する第1選択器、ノーマル値に応答し外部への送信信号を生成する内部ロジック回路、第4レジスタ出力と内部ロジック回路出力の何れかを選択する第2選択器、第1、第2選択器を制御する電力制御部、NモードからSモード転換時、第1、第2選択器の出力を格納するリテンション入出力装置とを有し、NモードからSモード転換時、リテンション入出力装置の入出力状態は、第1選択器の出力により保持される。

(もっと読む)

半導体集積回路

【課題】低消費電力状態の解除に伴う誤動作を解消する。

【解決手段】動作電源の供給と遮断が制御される内部回路と、動作モードに応じて記内部回路に対する動作電源の供給と遮断を制御する電源制御回路(30)とを有する。電源制御回路は、記憶回路(35,36)及び電源制御シーケンス回路(39)を有する。記憶回路は動作電源の供給と遮断を切換え指示する切換え指示データと動作電源の遮断及び解除の動作モードを決める低消費電力モードデータを入力して保持する。電源制御シーケンス回路は、前記記憶回路が保持する切換え指示データと低消費電力モードデータを参照して動作電源の遮断と供給の遷移制御を行い、低消費電力モードデータに応ずる動作電源の供給遮断状態において前記切換え指示データにより動作電源の供給遮断状態を解除するとき、動作電源の供給を受ける内部回路の動作が保証されるまで前記低消費電力モードデータの新たな参照を抑制する。

(もっと読む)

オーディオファイルの再生に適応したコンピュータシステム

【課題】オーディオファイルの再生に適応したコンピュータシステムを提供する。

【解決手段】システムCPUと、メモリと、圧縮されたオーディオデータを含む少なくとも1つのドライブと、入力オーディオ装置と、少なくとも前記システムCPUと前記メモリとを制御することに適応した1番目のオペレーティングシステムと、2番目のオペレーティングシステムとを具備し、前記2番目のオペレーティングシステムが、前記システムCPUに前記圧縮されたデータを復元させると共に、前記圧縮されたデータを前記メモリへ記憶させるように構成されると共に、音声録音アプリケーションの間、前記利用者がアナログ音声データを前記入力オーディオ装置に入力することを可能にするように構成されることを特徴とする。

(もっと読む)

21 - 40 / 65

[ Back to top ]