Fターム[5B011DC06]の内容

Fターム[5B011DC06]に分類される特許

1 - 20 / 117

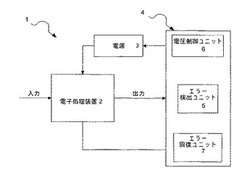

電圧制御

【課題】電子処理装置への電源電圧を最も効率の良い電力点で動作し、処理装置の出力の正確性を犠牲にすることなく、発生するエラーを修正することが可能な電圧制御方法を提供する。

【解決手段】プロセッサ又はメモリ要素を有する電子処理装置2への電源電圧を制御し電子処理装置の出力を受信する装置であって、当該装置は、電子処理装置の出力におけるエラーを検出するエラー検出手段5と、電子処理装置の出力において検出されたエラーの分析に基づいて、電子処理装置への電源電圧を適応的に変化させる手段6とを備える。装置は更に、電子処理装置の出力における検出されたエラーを修正する手段7を備える。

(もっと読む)

データ処理装置

【課題】高電源電圧で動作する場合に不要な待ち時間を抑制して高速な復帰が可能なデータ処理装置を提供する。

【解決手段】データ処理装置は、演算処理部と協働して動作する周辺部と、第1モードから第2モードへの切り替えの際に起動タイミングを制御するための管理部とを含む。周辺部は、第1モードの際に電源供給が制限されるモジュールと、第1モードから第2モードへの切り替えの際に、モジュールの少なくとも一部の復帰を検知して、検知信号を出力するための復帰検知回路と、電源供給の電圧が低い場合に合わせてモジュール全体が復帰するまで検知信号の管理部への出力を遅延させるための遅延回路とを含む。遅延回路の遅延時間は、電源供給の電圧に従い遅延回路に流れる動作電流に起因して、電源供給の電圧が低い場合よりも電源電圧が高い場合の方が短くなるように調整される。

(もっと読む)

電子機器及び電子機器システム

【課題】USB規格に準拠しつつ供給可能な電力を増加することができる電子機器及び電子機器システムの提供。

【解決手段】電子機器100は、USB3.0ホストコネクタ140を介して接続される外部デバイスへ電力を供給するDCDCコンバータ131〜133と、USB3.0ホストコネクタ140の所定の端子を介して、接続された外部デバイスを判定するデバイス判定部124とを備える。接続された外部デバイスがUSB互換デバイス200と判定された場合、このUSB互換デバイス200が所望する電圧の値を取得し、取得した電圧の値の応じて、必要なDCDCコンバータ131〜133を動作させることより、USB互換デバイス200への電力供給を行う。

(もっと読む)

電子機器の電源回路

【課題】汎用性の高い電子機器の消費電力低減回路を提供する。

【解決手段】この電子機器の電源回路30は、携帯機の振動に伴ってローレベルの電圧を出力する振動センサ31を備えている。振動センサ31から出力されるローレベルの電圧がクロックモジュール32の入力端子32aに入力されると、クロックモジュール32は、出力端子32bからハイインピーダンスの割り込み出力を行うとともに、計時動作を開始する。また、クロックモジュール32は、計時動作を通じて計時された時間が規定時間に達することをもって、出力端子32bのローレベルの電圧の割り込み出力を行う。そして、クロックモジュール32の割り込み出力に基づいてMOSトランジスタFET1がオン/オフされることで、電子部品15の不要な電力消費を低減する。

(もっと読む)

通信装置及びその制御方法、並びに、コンピュータプログラム

【課題】メインシステムとサブシステムとから構成されるマルチプロセッサ/マルチコアシステムにおいて、省電力モード時にオフされるメモリが共有メモリである場合にも、安全に省電力/通常モードに移行する。

【解決手段】第1のプロセッサと、第2のプロセッサと、前記第1のプロセッサと前記第2のプロセッサとがアクセスする第1のメモリと、前記第2のプロセッサがアクセスする第2のメモリとを有し、前記第2のプロセッサは、前記第1のプロセッサからの指示に従って前記第1のメモリから前記第2のメモリにアクセス先を切替えると共に、省電力状態に移行する。

(もっと読む)

情報処理システムおよび情報処理システムにおける電源およびクロックの制御方法

【課題】消費電力を低減可能な情報処理システム、および情報処理システムにおける電源およびクロックの制御方法を提供する。

【解決手段】切り替え制御部85は、「アクセス待機」状態では、待機時間WT1がアクセス検出待ち時間AWT以上である場合(WT1≧AWT)、「クロック供給停止」状態に遷移する。「クロック供給停止」状態では、状態依存クロック制御信号CSSを非アクティブレベルに設定することにより、サブシステムバス40へのシステムクロックの供給を停止させる。この後、待機時間WT2がクロック停止安定時間CSST以上となった場合(CSST≦WT2)、「電源供給停止状態」に遷移する。「電源供給停止状態」では、状態依存電源制御信号PSSを非アクティブレベルに設定することにより、サブシステムバス40の非インタフェース部への電源の供給を停止させる。

(もっと読む)

車載電子制御装置

【課題】スタンバイ開路スイッチを内蔵したマイクロプロセッサに対する簡易な定電圧電源回路を提供する。

【解決手段】電源リレーの出力接点102aを介して車載バッテリ101から給電される第2の

定電圧電源回路20Sに対し、車載バッテリ101から直接給電される第4の定電圧電源回路40Dを直列抵抗41を介して並列接続してマイクロプロセッサ120Aの駆動電源端子に接続する。出力接点102aが閉路している時は、マイクロプロセッサは第2の定電圧電源回路20Sの出力電圧によって動作し、第4の定電圧電源回路の出力電流は、直列抵抗41によって所定値以下に制限される。電源スイッチ103が開路された運転停止時には、マイクロプロセッサには第4の定電圧電源回路40Dから微小なスタンバイ電流が供給される。

(もっと読む)

プロセッサの温度制御インタフェース

【課題】アプリケーションに適当な制御及び/又は同期化性能を提供することを目的とする。

【解決手段】プロセッサの温度制御インタフェース技術である。一実施例において、プロセッサは双方向インタフェースと、前記双方向インタフェースで内部の高温を示す第1の信号をアサートする出力ロジックとを含む。内部の高温が示された場合、又は前記双方向インタフェースで外部信号が受信された場合のいずれかの場合に、抑圧ロジックがプロセッサの動作を抑圧する。

(もっと読む)

半導体装置及び携帯情報端末

【課題】CPU起動前にAFE初期較正を実行可能にすることで、AFE初期較正をユーザにより設定することなく行う手段を半導体装置に提供する。

【解決手段】フラッシュメモリー制御部FMC中の初期較正制御部CCがAFEの初期較正の起点となる。MCUの初期較正が終了すると、初期較正制御部CCは初期較正データをフラッシュメモリーFMに要求し取得する。この際のフラッシュメモリーFMに設定される初期較正データはバスコントローラ102を超えてAFE通信モジュールACMに入力される。初期較正制御部CCは、AFE専用信号線SLaを介して、この初期較正データのラッチをAFE通信モジュールACMに指示する。

(もっと読む)

周波数および電圧のスケーリング・アーキテクチャ

【課題】マイクロプロセッサを複数のクロック・ドメインに分割し、それらの消費する電力を制御する技術を提供する。

【解決手段】マイクロプロセッサの少なくとも1つのクロック・ドメインの周波数および動作電圧をスケールするための装置および方法である。プロセッサの各クロック・ドメインのクロック信号周波数および動作電圧は、第1および第2時間間隔に対するエネルギー遅延二乗積の比を最小にするクロック信号周波数および動作電圧のペアが選択される。

(もっと読む)

電子回路、その制御方法及び画像形成装置

【課題】内部メモリを有する電子回路において、待機状態での動作要求時の処理効率および省電力化の向上を図れる電子回路を提供する。

【解決手段】電子回路31は、通常モードにおいて外部メモリ34とアクセス可能な制御部41と、外部メモリより消費電力の少ない内部メモリ44と、ネットワークI/F67と、省電力モードにおいて、ネットワークI/F67から内部メモリ44へのアクセスを可能とする第2アクセス経路G2,F2と、経路切替部65とを含む。経路切替部65は、通常モードから省電力モードへの切替時に、制御部41の制御に応じて、外部メモリ34への第1アクセス経路G1を第2アクセス経路G2,F2に切替えることによって、通常モードにおいて外部メモリ用のアドレスがマッピングされていたアドレス空間を、内部メモリ用のアドレス空間に切替る。

(もっと読む)

半導体装置及びデータ処理システム

【課題】中央処理装置が設定した低消費電力状態の解除に伴う電力消費と処理時間を短縮することができ、且つ、中央処理装置が既に設定した低消費電力状態の強制解除と復帰との関係の制御を容易に行うことができる半導体装置を提供する。

【解決手段】中央処理装置(41)自らに対して、そして被制御回路(12,22)に対して、電源及びクロックの停止と供給を制御する低消費電力のための制御機構に、所定の被制御回路から出力される電源及びクロックの停止を要求する信号(400)が要求する期間だけ、別の被制御回路に対して既に設定されている電源及びクロックの供給停止を強制解除する、強制解除制御回路(70)を採用し、強制解除に中央処理装置を介在させることを要さず、また、所定の被制御回路からの要求が終われば元の低消費電力状態に復帰されるようにする。

(もっと読む)

電源装置およびそれを用いた電子機器

【課題】マイクロプロセッサに供給すべき電源電圧を柔軟に設定する。

【解決手段】マイクロプロセッサ10に対して電源電圧Vddを供給する電源装置100において、システムコントローラ20は、マイクロプロセッサ10から出力される電圧指示信号Dcnfにもとづき、マイクロプロセッサ10に供給すべき電源電圧Vddを設定し、設定した電源電圧に対応した電圧設定信号Dsetを出力する。レギュレータ回路12は、システムコントローラ20から出力される電圧設定信号Dsetにもとづき、システムコントローラ20において設定された電源電圧Vddを生成し、マイクロプロセッサ10に供給する。システムコントローラ20は、マイクロプロセッサ10の使用時間、温度、演算量などの状態を取得し、取得した状態を電源電圧Vddの設定に反映させる。

(もっと読む)

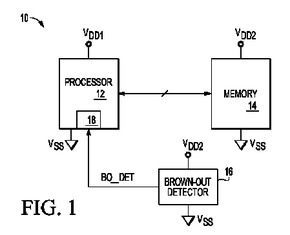

ブラウンアウト検出回路を有するデータ処理システム

ブラウンアウト検出回路(16)は、第1抵抗素子(38)と、第1トランジスタ(46)と、第2トランジスタ(50)と、比較器(40)とを備える。第1抵抗素子(38)が、第1電源電圧端子および第2端子に接続される第1端子を有する。第1トランジスタ(46)は、第1導電性タイプであり、第1抵抗素子(38)の第2端子に接続される第1電流電極と、制御電極と、第2電流電極とを有する。第2トランジスタ(50)は、第2導電性タイプであり、第1トランジスタ(46)の第2電流電極に接続される第1電流電極と、制御電極と、第2電源電圧端子に接続される第2電流電極とを有する。比較器(40)は、第1抵抗素子(38)の第1端子に接続される第1入力端子と、第1抵抗素子(38)の第2端子に接続される第2入力端子と、ブラウンアウト検出信号を供給するための出力端子とを有する。  (もっと読む)

(もっと読む)

半導体集積回路及び電源制御方法

【課題】スリープ機能実行時でもデバッグを実行することができる半導体集積回路及び電源制御方法を提供すること

【解決手段】本発明にかかる半導体集積回路1は、デバッグを行うデバッグモード及びデバッグを行わないノンデバッグモードのいずれか一方のモードにより動作する。半導体集積回路1は、いずれか一方のモードで動作している際に、回路の動作を停止するスリープ状態へ移行する動作回路20を有する。さらに、スリープ状態へ移行した場合、動作回路20がノンデバッグモードであれば、動作回路20へ電源供給を停止し、動作回路20がデバッグモードであれば、動作回路20へ電源供給を実行する電源制御部3を有する。

(もっと読む)

画像形成装置及びその制御方法

【課題】コスト増加を招くことなく分散制御システムを適用するとともに、省電力モードからの復帰処理の高速化と安全性を向上させた画像形成装置を提供する。

【解決手段】本画像形成装置によれば、各CPUは、省電力モード遷移時に初期化処理に必要な情報の一部を自身の不揮発メモリに保持し、それ以外の情報については上位層のCPUに保存を依頼する。さらに、再起動時おいて、各CPUは、自身の不揮発メモリに記憶した情報を使用して再起動し、他のCPUとの通信接続が完了すると、下位層のCPUから依頼された保持データを当該CPUに提供する。

(もっと読む)

保証された定常状態期限で中央処理装置電力を制御するためのシステムおよび方法

中央処理装置を動的に制御する方法が、開示される。この方法は、CPUがいつ定常状態に入るかを判定すること、CPUが定常状態に入ると、CPUに関する最適な周波数を計算すること、定常状態CPU利用率を保証すること、および定常状態CPU利用期限を保証することを含むことが可能である。 (もっと読む)

半導体集積回路、半導体集積回路の制御方法及びその制御プログラム

【課題】複数のドメインに供給される電源電圧が互いに同じ値となる場合において、ドメイン間で信号の送受信を正確に行うことを目的とする。

【解決手段】開示の装置は、それぞれ異なる電源から電源電圧が供給されるとともに互いに信号の送受信を行う複数のドメインと、ドメイン毎に設けられ、ドメインの動作状態を制御する動作制御部と、を有する。ドメインは、電流値の変更を伴う動作状態の変更を要求する動作変更要求を動作制御部に送信する。動作制御部は、動作変更要求をドメインより受信すると、動作変更要求に係る動作変更によるドメイン全体の電流変化率を求め、当該電流変化率が所定値以下となっている場合に、動作変更要求をドメインに対し許可する。

(もっと読む)

装置、方法、システム

【課題】 本発明は、実行命令を生成する装置、システム、及び方法を提供する。

【解決手段】 本発明の実施例は、実行命令を生成する装置、システム、及び方法を提供する。いくつかの説明のための実施例は、所定の実行可能なフォーマットの実行命令を、メモリーアドレスを表すメモリーアクセス命令のメモリーアドレスデータに基づき生成する段階を有する。他の実施例も説明及び請求される。本発明のいくつかの説明のための実施例は、受信したメモリーアクセス命令のアドレスデータに基づき所定の実行可能なフォーマットの実行命令を生成する装置、システム、及び/又は方法を有する。本発明のいくつかの説明のための実施例では、メモリーアドレス命令は、少なくとも部分的に実行命令に変換されて良い。

(もっと読む)

ウォッチドッグタイマ

【課題】マイクロコンピュータのスタンバイ時にウォッチドッグタイマを停止させても、高いセキュリティ機能を維持できるようにし、スタンバイ時の消費電流を低減させる。

【解決手段】本発明に係るウォッチドッグタイマ2は、クロック信号をカウントするカウンタ11と、マイクロコンピュータ1をスタンバイ状態にする指示信号としてのスタンバイ要求信号、及びマイクロコンピュータ1がスタンバイ状態にあることを示すスタンバイ・ステータス信号の論理和からなるインヒビット信号により、カウンタ11を制御する手段12とを備える。

(もっと読む)

1 - 20 / 117

[ Back to top ]