Fターム[5B011EA08]の内容

Fターム[5B011EA08]に分類される特許

1 - 20 / 346

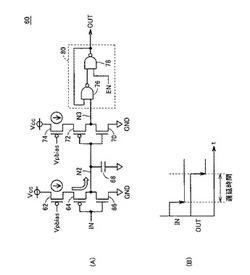

データ処理装置

【課題】高電源電圧で動作する場合に不要な待ち時間を抑制して高速な復帰が可能なデータ処理装置を提供する。

【解決手段】データ処理装置は、演算処理部と協働して動作する周辺部と、第1モードから第2モードへの切り替えの際に起動タイミングを制御するための管理部とを含む。周辺部は、第1モードの際に電源供給が制限されるモジュールと、第1モードから第2モードへの切り替えの際に、モジュールの少なくとも一部の復帰を検知して、検知信号を出力するための復帰検知回路と、電源供給の電圧が低い場合に合わせてモジュール全体が復帰するまで検知信号の管理部への出力を遅延させるための遅延回路とを含む。遅延回路の遅延時間は、電源供給の電圧に従い遅延回路に流れる動作電流に起因して、電源供給の電圧が低い場合よりも電源電圧が高い場合の方が短くなるように調整される。

(もっと読む)

電圧制御

【課題】電子処理装置への電源電圧を最も効率の良い電力点で動作し、処理装置の出力の正確性を犠牲にすることなく、発生するエラーを修正することが可能な電圧制御方法を提供する。

【解決手段】プロセッサ又はメモリ要素を有する電子処理装置2への電源電圧を制御し電子処理装置の出力を受信する装置であって、当該装置は、電子処理装置の出力におけるエラーを検出するエラー検出手段5と、電子処理装置の出力において検出されたエラーの分析に基づいて、電子処理装置への電源電圧を適応的に変化させる手段6とを備える。装置は更に、電子処理装置の出力における検出されたエラーを修正する手段7を備える。

(もっと読む)

プロセッサ動作電圧の自動動的制御

【課題】プロセッサシステムは、動作電圧とコア/バス周波数との組み合わせによってはプロセッサの損傷あるいはプロセッサの動作の信頼性低下を引き起こすことを防止する。

【解決手段】1つのプロセッサの動作電圧を動的に調整する一方で、前記プロセッサが前記プロセッサの前記コア/バス周波数比との関係において有害である1つの動作電圧状態に1人のユーザによって置かれることを防止するための手法。より具体的には、プロセッサの動作電圧をプロセッサのバスおよび/あるいはコアクロック周波数の1つの関数として制御するための1つの手法に関する。

(もっと読む)

半導体装置

【課題】外部電源の電圧に応じて、より適切な動作モードや動作周波数を自動的に設定することが可能な半導体装置を提供する。

【解決手段】ある実施の形態に従う半導体装置は、プロセッサと、プロセッサによるアクセスが可能な不揮発性メモリと、少なくともプロセッサおよび不揮発性メモリを駆動するための外部電源の電圧を検出する電圧検出部とを含む。プロセッサは、命令群を実行することで、電圧検出部によって検出された電圧に応じて、プロセッサおよび不揮発性メモリの少なくとも一方についての動作モードおよび/または動作周波数を設定する。

(もっと読む)

マルチメディア処理電力管理のためのパワーゲーティング

【課題】マルチメディア処理環境内での電力節約及び性能改善に対応する。

【解決手段】マルチメディア処理環境内でパワーゲーティングを実施するための回路は、相互に別々に動作する様々な構成要素を含み得るマルチメディア表示プロセッサのための効果的な電力管理に対応する。この方式において回路は、マルチメディア処理環境内での電力節約及び性能改善に対応することができる。態様によっては、ヘッドスイッチまたはフットスイッチ回路が、例えば、論理構成要素がアクティブモードにあるかそれとも非アクティブモードにあるかなど、個々の論理構成要素の動作モードに応じて、マルチメディア表示プロセッサの異なる論理構成要素を、電源レールと選択的に接続及び切断するように実施され得る。

(もっと読む)

電源制御装置、電源制御装置の制御方法、およびプログラム

【課題】多様な信号規格の処理に対応する半導体集積回路において、様々な周期性の違いに伴いタイミングと時間幅が変わるアイドル状態に対応した電源制御を適用し、消費電力を低減する。

【解決手段】処理状態と待機状態とを周期的に繰り返して処理を行う半導体集積回路の電源ドメインを制御する電源制御装置であって、待機状態の発生期間および発生間隔を含む周期的特徴情報を取得する周期情報取得部103と、電源ドメインが待機状態における待機電圧から半導体集積回路が動作可能となる電圧へ復帰するまでに要する復帰時間と対応付けられた待機電圧候補から、発生期間よりも復帰時間が短くなる待機電圧を電源制御情報として設定する電源制御情報設定部104と、電源制御情報に従って発生期間における電源ドメインの待機電圧を制御する電源制御部105とを備える。

(もっと読む)

情報処理装置及び省電力モードの管理方法

【課題】コストの増大をもたらすことなく、高速に省電力モードから復帰することができる情報処理装置を提供する。

【解決手段】省電力モードへの移行に際しては、揮発性メモリ33にロードされたプログラムを省電力モードにおいても保持し続けるように揮発性メモリ33が制御され、かつ、省電力モード中であることを示す論理値がサブマイコン21の入出力ポートに設定される。起動時においては、プロセッサ32は、入出力ポートに省電力モード中であることを示す論理値が設定されているか否かを判断し、設定されている場合には、省電力モードからの復帰と認識して、揮発性メモリ33に保持されたプログラムを実行し、一方、設定されていない場合には、プロセッサ32は、通常の起動と認識して、不揮発性メモリ34に保持されたプログラムを揮発性メモリ33にロードし、ロードされたプログラムを実行する。

(もっと読む)

半導体装置

【課題】寿命が長い半導体装置を提供する。

【解決手段】このLSIは、2つのCPU1,2と、CPU1,2のうちのいずれか1つのCPUを示す論理レベルのデータ信号が書き込まれた記憶回路4と、リセット信号REが非活性化レベルにされてLSIのリセットが解除された場合、記憶回路4の記憶データの論理レベルに対応するCPUのみに電源電圧を供給するとともに、記憶回路4の記憶データを現在の論理レベルと異なる論理レベルのデータ信号に書き換える制御回路3,5とを備える。したがって、故障の検知や、厳密なタイミング制御を必要とせずに、CPUの長寿命化を図ることができる。

(もっと読む)

プロセッサシステム及び半導体集積装置

【課題】処理速度の低下を最低限に抑えかつ従来技術に比較して消費電流の変動を抑える。

【解決手段】プロセッサシステム1は、プログラムメモリ2に格納された複数の命令コードを任意の順序で連続して実行する。テーブルメモリ53は、各命令コードと各命令コードの実行時の消費電流量との関係を示す消費電流量テーブルを格納する。電流変動抑制回路51は、消費電流量テーブルを参照して、連続する2つの命令コードの実行時の消費電流量の差の大きさが所定のしきい値以下になるように、上記連続する2つの命令コードのうちの一方の命令コードの実行時にプロセッサシステム1に流す補正消費電流を算出し、上記算出された補正消費電流量の補正消費電流をプロセッサシステム1に流すように、補正消費電流発生回路54を制御する。

(もっと読む)

電子機器の保守装置、方法、及びプログラム

【課題】電子機器の通常動作を妨げることなく、CPUの経時劣化を保障し、電子機器の性能を維持することができるようにする。

【解決手段】保守装置1は、CPU11に内蔵されるセンサ回路12からCPU11の劣化に応じて変化する劣化情報をCPU11の通常動作時に取得する劣化情報取得部2と、劣化情報に基づいてCPU11の劣化の進行度を示す劣化レベルを判定する劣化レベル判定部3と、劣化レベルの増大に伴いCPU11に印加される電源電圧を増加させるように電源13を制御する電源制御部4とを備える。

(もっと読む)

車載用電源装置

【課題】マイコン電圧配線に接続されるコンデンサを小型化する。

【解決手段】車載用電源装置は、車載電源であるバッテリ200と、リレー201と、入力側コンデンサ203と、シリーズレギュレータ回路10と、出力側コンデンサ300とを備え、マイコン900に接続されている。シリーズレギュレータ回路10は、Nチャネル型MOSFET100と、FETの出力制御回路であるゲート電圧調整回路101と、ゲート電圧保持コンデンサ102を備え、ゲート電圧調整回路101によりコンデンサ−GND電圧(ゲート電圧)102Bを調整することにより、入力側コンデンサ電圧203Bを出力側コンデンサ電圧300Bに変換し、マイコンにマイコン電流900Aを供給する。

(もっと読む)

CPU電力配送システム

【課題】中央処理ユニット(CPU)のような集積回路コンポーネントにおいて、複数の電圧調整器モジュール(VRM)により、複数のCPUコア、キャッシュおよびI/Oコンポーネントに別個の電源電圧を差し向ける、電力配送システムを提供する。

【解決手段】CPUダイおよび該CPUダイに接合された電圧調整器ダイを三次元実装レイアウトして、各電圧調整器モジュール(VRM)が、CPUダイ内の各コンポーネントに調整された電圧を供給する。

(もっと読む)

半導体集積回路、半導体装置およびリモートコントローラ

【課題】マイクロコンピュータがストップ状態であり、キャパシタによって電源電圧がマイクロコンピュータに供給されている場合、マイクロコンピュータのストップ状態を維持する。

【解決手段】検出回路(3)は、外部キャパシタ(C1)を放電させる外部キャパシタ放電回路(30A)と、電源電圧を保持する内部キャパシタ(C2)と、内部キャパシタを放電させる内部キャパシタ放電回路(30)と、比較器(32)と、出力回路(33)とを有する。比較器は、放電後の外部キャパシタの第1電圧(VC1)を、放電後の内部キャパシタの第2電圧(VC2)と比較する。比較の結果、出力回路は、第1電圧が第2電圧よりも低い場合、マイクロコンピュータが外部キャパシタから電源電圧の供給を受けていることを示す検出信号(S2)を出力する。割り込み回路(4)は、その検出信号を受けた場合、割り込み信号(SI)を出力しない。

(もっと読む)

マイクロコンピュータ

【課題】リソースでの無駄な消費電力を削減することができるマイクロコンピュータを提供することを目的とする。

【解決手段】外部から電源を供給されるマイクロコンピュータにおいて,それぞれの所定の機能を有し,外部から供給される前記電源の起動時に電源が供給されない複数のリソースと,前記複数のリソースにバスを介して接続され,前記リソースに前記バスを介してアクセス信号を供給する制御ユニットと,前記複数のリソースにそれぞれ設けられ,電源起動信号に応答して外部から供給される前記電源から対応するリソースにリソース内電源を供給する複数のリソース内電源供給部と,前記複数のリソースにそれぞれ設けられ,前記バスを介して供給されるアクセス信号が対応するリソース宛か否かを検知し,前記アクセス信号が対応するリソース宛の場合に前記電源起動信号を対応するリソース内電源供給部に出力できる電源制御部とを有する。

(もっと読む)

情報処理システムおよび情報処理システムにおける電源およびクロックの制御方法

【課題】消費電力を低減可能な情報処理システム、および情報処理システムにおける電源およびクロックの制御方法を提供する。

【解決手段】切り替え制御部85は、「アクセス待機」状態では、待機時間WT1がアクセス検出待ち時間AWT以上である場合(WT1≧AWT)、「クロック供給停止」状態に遷移する。「クロック供給停止」状態では、状態依存クロック制御信号CSSを非アクティブレベルに設定することにより、サブシステムバス40へのシステムクロックの供給を停止させる。この後、待機時間WT2がクロック停止安定時間CSST以上となった場合(CSST≦WT2)、「電源供給停止状態」に遷移する。「電源供給停止状態」では、状態依存電源制御信号PSSを非アクティブレベルに設定することにより、サブシステムバス40の非インタフェース部への電源の供給を停止させる。

(もっと読む)

電力制御方法、電子装置、プログラム及びプログラムの生成方法

【課題】メモリによる消費電力を削減する。

【解決手段】プロセッサ2で実行されるプログラム中の関数が割り当てられ、通常状態と省電力状態の電力制御状態をもつ複数のメモリ領域3a,3bのうち、メモリ領域3aに配置される関数faの実行時、メモリ領域3bに配置される関数fbが呼び出される直前に、メモリ領域3aを省電力状態、メモリ領域3bを通常状態とするように、プロセッサ2が複数のメモリ領域3a,3bの電力制御状態を制御する。

(もっと読む)

電子機器及びその制御方法、プログラム

【課題】 低温からの起動を迅速に行い、すばやく正常動作可能とし、かつ、加熱中に半導体がラッチアップ、暴走等の保証外の異常動作を防ぐ電子機器及びその制御方法、プログラムを提供する。

【解決手段】 当該電子機器を制御するための、動作保証温度範囲を有する電子部品と、電子部品へ電源を供給する電源供給部と、電子部品を加熱するための加熱部と、電子部品の温度を検出する温度検出部とを備える。検出される温度に従って、電子部品を加熱するとともに、電子部品への電源供給のON/OFFを行う。

(もっと読む)

選択可能な副精度に対して、低減された電力要求を有する浮動小数点プロセッサ

【課題】所定の精度を有する浮動小数点プロセッサにより、必要以上の電力を消費せずに浮動小数点演算を実行する。

【解決手段】1つ以上の浮動小数点数に関して、浮動小数点演算に対する副精度が選択される。副精度の選択は、1つ以上の浮動小数点数のそれぞれに対して、1つ以上の過剰ビットをもたらす。さもなければ1つ以上の過剰ビットを記憶または処理するために使用される、浮動小数点プロセッサ中の1つ以上のコンポーネントから、電力を取り除くことができ、浮動小数点演算は、1つ以上のコンポーネントから電力を取り除いた状態で実行される。

(もっと読む)

半導体集積回路、その制御方法、及び電子機器

【課題】動作周波数の変更を行う場合に当該半導体集積回路に供給されるべき供給電圧を低く抑えることのできる半導体集積回路を提供する。

【解決手段】電源回路13から供給される供給電圧により動作し、動作周波数を初期周波数から目標周波数に変更する半導体集積回路10であって、当該動作周波数を変更する際に、供給電圧を目標周波数に応じて決定される目標電圧に変更するよう電源回路13に要求し、初期周波数から前記目標周波数への変更を、複数回に分けて段階的に行う半導体集積回路10である。

(もっと読む)

回路、電子機器、及び画像処理装置

【課題】電子機器の省電力制御における回路規模をより小さくする一方法を提供する。

【解決手段】メモリーコントローラー及びメモリーPHYにより制御されるSDRAMと接続し、通常モード及び省電力モードで動作可能なSoCは、省電力モードにおいて電源オフされるブロックA及び電源オフされないブロックBを含む。ブロックAには、調停回路が含まれる。ブロックBには、メモリーコントローラーと、メモリーPHYと、前記調停回路及び前記メモリーコントローラーの間に設けられ、省電力モード中に前記調停回路からの出力信号を所定のレベルに固定する信号レベル保持セルが含まれる。

(もっと読む)

1 - 20 / 346

[ Back to top ]