Fターム[5B015QQ02]の内容

Fターム[5B015QQ02]に分類される特許

1 - 20 / 31

二重フローティングゲート構造を有するトランジスタを備えた不揮発性メモリ

【課題】CMOS製造プロセスに用いることのできる材料を用いかつノイズマージンの広い不揮発性メモリを提供する。

【解決手段】本実施形態の不揮発性メモリによれば、第1および第2のPチャネルトランジスタはそれぞれ第1の半導体領域上に設けられ、第1の半導体領域上に、第1の絶縁膜と、第1のフローティングゲート、第2の絶縁膜、第2のフローティングゲート、第3の絶縁膜、および第1の制御ゲートが、この順序で積層された構造を有し、前記第1および第2のNチャネルトランジスタはそれぞれ第2の半導体領域上に設けられ、前記第2の半導体領域上に、第4の絶縁膜、第3のフローティングゲート、第5の絶縁膜、第4のフローティングゲート、第6の絶縁膜、および第2の制御ゲートがこの順序で積層された積層構造を有している。

(もっと読む)

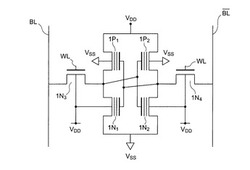

スイッチトランジスタを有しない差動センス増幅器

【課題】半導体メモリのセンス増幅器は、回路全体の面積を増やし、製造コストを押し上げるため、センス増幅器に使用される面積を最小限に抑える必要がある。

【解決方法】本発明の差動センス増幅器は、第1のビットライン(BL)に接続された出力および第1のビットラインに対して相補的な第2のビットライン(/BL)に接続された入力を有する第1のCMOSインバータと、第2のビットライン(/BL)に接続された出力および第1のビットライン(BL)に接続された入力を有する第2のCMOSインバータとを備え、それぞれのCMOSインバータはプルアップトランジスタ(M21、M22)および前記プルダウントランジスタ(M31、M32)を備え、プルアップトランジスタ(M21、M22)またはプルダウントランジスタ(M31、M32)のソースは、トランジスタのソースと電圧源との間に中間トランジスタを置くことなく、プルアップ電圧源またはプルダウン電圧源に電気的に結合され、接続されることを特徴とする。

(もっと読む)

不揮発性コンフィギュレーションメモリ

【課題】低消費電力及び小面積の不揮発性コンフィギュレーションメモリを提案する。

【解決手段】実施形態の不揮発性コンフィギュレーションメモリは、ゲートに出力ノードD12が接続され、ソースに第1の電圧が印加され、ドレインに出力ノードD11が接続されるトランジスタM11と、ゲートに出力ノードD11が接続され、ソースに第1の電圧が印加され、ドレインに出力ノードD12が接続されるトランジスタM12と、制御ゲートにワード線WL11が接続され、ソースに第1の電圧よりも低い第2の電圧が印加され、ドレインに出力ノードD11が接続され、記憶層に不揮発的に記憶されるデータにより閾値が変化するトランジスタF11と、制御ゲートにワード線WL12が接続され、ソースに第2の電圧が印加され、ドレインに出力ノードがD12接続され、記憶層に不揮発的に記憶されるデータにより閾値が変化するトランジスタF12とを備える。

(もっと読む)

半導体装置

【課題】MOSトランジスタのしきい値電圧のばらつきに係らず、低電源電圧下においても安定かつ高速なデータ読出、スタンバイ電流の低減およびリテンション特性の向上を可能とする半導体装置を提供する。

【解決手段】半導体装置は、SRAMセルからなるメモリセルMCが行列状に配列されるメモリセルアレイおよび周辺回路を含むSRAMブロックと、FGTブロックと、SRAMブロックとFGTブロックとを電気的に接続するための接続ブロックとから構成される。FGTブロックは、FGT(フローティングゲートトランジスタ)50と、SRAMセルを構成するMOSトランジスタのしきい値電圧のばらつきに応じて、FGT50のしきい値電圧をチューニングするためのプログラム回路とを有する。FGT50は、SRAMブロックのスタンバイ時、ダイオード接続され、SRAM_VSS線と電気的に接続される。

(もっと読む)

半導体装置およびそれを用いた半導体集積回路

【課題】バックゲートを有するMOSを、回路の動作特性に応じて使い分け、幅広い温度範囲にて高速かつ低電力なLSIを実現する。

【解決手段】薄膜埋め込み酸化膜層を持つFD−SOIを使用し、薄膜埋め込み酸化膜層の下層半導体領域をバックゲートとし、論理回路ブロックにおいてブロック中の負荷の軽い論理回路にはバックゲートの電圧をブロック活性化に合わせてブロック外から制御する。このバックゲート駆動信号を発生する回路、及び回路ブロック出力部など負荷の重い論理回路には、ゲートとバックゲートとを接続したトランジスタを用い、そのゲート入力信号でバックゲートを直接制御する。

(もっと読む)

SRAMメモリセル

【課題】現存のデバイスの欠点を取り除き、さらにSRAM型メモリセルの体積を減少させる。

【解決手段】SRAM型メモリセルであって、絶縁層によってベース基板から隔離された半導体材料の薄膜を含む絶縁基板上の半導体と、2個のアクセストランジスタT1,T4と、2個の伝導トランジスタT2,T5と、2個の充電トランジスタT3,T6とを含み、メモリセルは、トランジスタT1−T6のそれぞれが、チャネルの下方でベース基板内に形成されたバックコントロールゲートBG1,BG2を有し、トランジスタの敷居電圧を調整するようにバイアスをかけられ、第1のバックゲートラインはアクセストランジスタT1,T4に接続し、第2のバックゲートラインは伝導トランジスタT2,T5および充電トランジスタT3,T6に接続し、各々の電位はセル制御動作の型に応じて調整される。

(もっと読む)

半導体装置、センスアンプ回路、半導体装置の制御方法及びセンスアンプ回路の制御方法

【課題】ダブルゲートトランジスタを用いた機能回路のバックゲート電圧を適切に制御して良好な特性を実現可能な半導体装置等及びその制御方法を提供する。

【解決手段】本発明の半導体装置は、ダブルゲートトランジスタを含む機能回路と、ダブルゲート構造の基準トランジスタ20、30を含む電圧制御回路を備えている。基準トランジスタ20、30には、第1ゲート電極に参照電圧Vrp、Vrnが印加され、第2ゲート電極の電位はドレイン電流Ip、Inが参照電流Irp、Irnと一致するように制御され、その電位が制御電圧VBGP、VBGNとして出力される。制御電圧VBGP、VBGNを機能回路のダブルゲートトランジスタの第2ゲート電極に印加することで機能回路に所望の特性が付与される。

(もっと読む)

半導体集積回路

【課題】ワード線の活性化電圧を、半導体集積回路の製造ばらつきや動作環境の変化に応じた適切な電圧に設定する。

【解決手段】マトリクス状に配置された複数のメモリセル(10A〜10D)と、複数のメモリセル(10A〜10D)の各行にそれぞれ対応する複数のワード線(WL1、WL2)と、複数のワード線(WL1、WL2)をそれぞれ駆動する複数のワード線ドライバ(12A、12B)を有するメモリマクロ(10)において、半導体集積回路(1)は、ワード線(WL1、WL2)が活性状態のときの、ワード線(WL1、WL2)の電圧を、Pchトランジスタ(31A)およびNchトランジスタ(31B)の閾値電圧特性によって異なる設定とする。

(もっと読む)

半導体装置

【課題】メモリが混載されたシステムLSIのリーク電流を低減し、スタンバイ状態の消費電力を低減する。

【解決手段】システムLSI中のロジック回路には電源スイッチを設け、スタンバイ時にはそのスイッチを遮断してリーク電流を低減する。同時にSRAM回路では、基板バイアスを制御することと、リードアンプあるいはライトアンプへの電源スイッチを設け、且つそのスイッチを遮断してリーク電流を低減する。

(もっと読む)

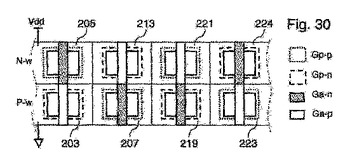

明白に異なる閾値電圧を有するトランジスタを持つSOIから製造する集積回路

本発明は、埋め込まれた絶縁材料面によって半導体基板層から隔てられた活性半導体層を含む集積回路に関する。この集積回路は、同じ型の第1および第2のトランジスタ(205、213)と、第1および第2のトランジスタの真下に配置された第1および第2の接地面とを有し、第1のトランジスタの接地面のドーピングは、第1のトランジスタのソースのドーピングと反対のドーピングであり、第1の閾値電圧を有する。第2のトランジスタの接地面のドーピングは、第2のトランジスタのソースのドーピングと同一のドーピングであり、第2の閾値電圧を有する。第1の閾値電圧は、第1のトランジスタのソースと接地面との間に印加される電位差に依存し、第2の閾値電圧は、第2のトランジスタのソースと接地面との間に印加される電位差に依存する。  (もっと読む)

(もっと読む)

センス増幅器回路、およびセンス増幅器回路を有するメモリ

【課題】低電圧SRAMおよびレジスタファイルのためのセンス増幅器スキームを提供する。

【解決手段】SRAMのためのセンス増幅器スキームが開示される。本願の実施例のうちの一つによると、センス増幅器回路は、ビット線と、センス増幅器出力と、電源供給電圧を有する電源供給ノードと、NMOSトランジスタを含むキーパ回路と、ノイズ閾値制御回路とを含む。キーパ回路は、十分な電流を供給してビット線のリーク電流を補償する大きさであり、ビット線の電圧レベルを維持し、ノイズ閾値制御回路は、センス増幅器出力のトリップ点を低くする。

(もっと読む)

半導体集積記憶回路及びラッチ回路のトリミング方法

【課題】複数あるラッチ回路全てのしきい値電圧のばらつきを一括してトリミングすることが可能な半導体集積記憶回路及びそれを用いたトリミング方法を提供する。

【解決手段】この半導体集積記憶回路は、第1、第2のインバータを第1及び第2のノードにおいてクロスカップル接続させて形成されるラッチ回路と、その第1のノードと第2のノードにホットキャリアを発生させる為のホットキャリア発生電圧を与える電圧印加回路とを含む。また、ラッチ回路から出力された増幅信号を反転させた反転信号を生成するために形成される反転回路を備える。

(もっと読む)

半導体記憶装置、及びそれを用いたトリミング方法

【課題】複数あるメモリセル全ての閾値電圧のばらつきを一括してトリミングする。

【解決手段】この半導体記憶装置は、第1インバータINV1と第2インバータINV2とをクロスカップル接続させて形成されるメモリセル20と、第1電圧が供給される電源端子21と、第2電圧を制御する第2電圧制御部28とを備える。メモリセル20のオフセット情報を読み出す場合には、電源端子21に印加される電圧と第2電源端子22に印加される電圧とを等しくした後、第1電源端子21に印加される電圧を第1電位に、第2電源端子22に印加される電圧を前記第2電位に復帰させる。インバータを構成するトランジスタにストレスを発生させる場合、第1電源端子21と第2電源端子22との間の電位差を、第1電位と第2電位との間の差よりも大きくする。

(もっと読む)

二重絶縁ゲート電界トランジスタを用いたMOSトランジスタ回路およびそれを用いたCMOSトランジスタ回路、SRAMセル回路、CMOS−SRAMセル回路、集積回路

【課題】単位回路の、高速動作と未使用時(注を入れる)または定常時または待機時における消費電力の減少を両立させた二重絶縁ゲート電界トランジスタを用いたMOSトランジスタ回路およびそれを用いたCMOSトランジスタ回路、SRAMセル回路、CMOS−SRAMセル回路、集積回路を提供することである。

【解決手段】四端子二重絶縁ゲート電界効果トランジスタからなるMOSトランジスタ回路において、前記四端子二重絶縁ゲート電界効果トランジスタの一方のゲートを入力端子とし、他方のゲートに抵抗の一方の端を接続し、ソースを第一の電源に接続し、ドレインを出力端子とすると供に負荷素子を通して第二の電源に接続し、前記抵抗の他端を一定電位の第三の電源に接続したことを特徴とする。

(もっと読む)

メモリセル

【課題】シングルイベントアップセットへの耐性を求めて改良されたメモリセルを提供する。

【解決手段】

一方のインバータ161の出力と、他方のインバータ162のPMOSおよびNMOSトランジスタのゲートとの間に別個のトランジスタ163,164が配置され、これらのトランジスタ163,164は別個に制御可能である。インバータ162のNMOSトランジスタのゲートまでの経路にNMOSトランジスタが配置され、インバータ162のPMOSトランジスタのゲートまでの経路にPMOSトランジスタが配置される。

(もっと読む)

半導体記憶装置

【課題】簡単な構成で大きな動作マージンを確保できかつ動作特性を向上した半導体記憶装置を提供する。

【解決手段】メモリセル内のラッチ部に含まれるトランジスタ(N1)のしきい値電圧(Vth)を動的に制御して、そのトランジスタの動作特性を動的に制御し、データの書き込み特性を向上させる。しきい値電圧を制御するために、トランジスタ(N1)のボディにバイアス信号を印加する。このバイアス信号としてビット線(WBL)の信号を使用する。データ書き込み時において事前にビット線(WBL)により伝達される書き込みデータの信号に基づき、メモリセル内のトランジスタ(N1)のボディにバイアスを印加し、トランジスタ(N1)のしきい値(Vth)を低下させる。

(もっと読む)

半導体記憶装置及び半導体装置

【課題】バリッドビットにおける無効化処理において、電源投入時に無効化処理を行うことができる半導体記憶装置を提供する。

【解決手段】第1のトランジスタと、第2のトランジスタと、を有する第1のインバータ回路と、入力部が前記第1のインバータ回路の出力部に接続され、出力部が前記第1のインバータの入力部に接続され、第3のトランジスタと、第4のトランジスタと、を有する第2のインバータ回路と、を含む初期化用メモリセルを有し、第3のトランジスタのしきい値電圧の絶対値は、第1のトランジスタのしきい値電圧の絶対値より低い構成とする。

(もっと読む)

プログラマブルROM

【課題】回路複雑化やコスト増なく、SRAMをプログラマブルROMとして使用する。

【解決手段】本発明の例に係るプログラマブルROMは、第1及び第2電源端子の間に直列に接続される第1電界効果トランジスタP1及び第2電界効果トランジスタN1と、ゲートがワード線WLに接続され、第1ビット線BLと第1及び第2電界効果トランジスタP1,N1のドレインとの間のデータ転送に使用される第3電界効果トランジスタN3と、第1及び第2電源端子の間に直列に接続される第4電界効果トランジスタP2及び第5電界効果トランジスタN2と、ゲートがワード線WLに接続され、第2ビット線bBLと第4及び第5電界効果トランジスタP2,N2のドレインとの間のデータ転送に使用される第6電界効果トランジスタN4とを備える。第1及び第4電界効果トランジスタP1,P2の閾値は、互いに異なり、その大小関係は、ROMデータに応じて決定される。

(もっと読む)

デプレションモードMOSFET回路および応用

【課題】デプレションモードMOSFET回路を用いた集積回路(IC)設計を提供する。

【解決手段】静電放電保護回路(ESD)、非反転ラッチおよびバッファ、ならびに1から3トランジスタスタティックランダムアクセスメモリセルを含むデプレションモードで動作するMOSFETを用いた正論理回路、システム、および方法。これらの新しい回路は、エンハンスメントモードMOSFET技術を補完し、相補金属酸化膜半導体(CMOS)集積回路(IC)製品の実現を改善することを目的としている。

(もっと読む)

半導体不揮発性メモリ回路および装置

【課題】余分なインターフェース回路等を必要とせず、記憶情報を光学的に設定して電気的に書き込むことができる不揮発性メモリ回路および装置を提供する。

【解決手段】第1のインバータ21および第2のインバータ22からなるフリップフロップ20と、前記フリップフロップの非反転出力端子Cと接地線GNDとの間に接続された第1のMIS型トランジスタ11と、前記フリップフロップの反転出力端子C_と前記接地線との間に接続された第2のMIS型トランジスタ12と、前記第1のMIS型トランジスタおよび第2のMIS型トランジスタのゲートに接続された書込ワード線WLWとを備えた不揮発性メモリ回路であって、前記フリップフロップの前記非反転出力端子と前記接地線との間に接続された第1のフォトダイオード41と、前記フリップフロップの前記反転出力端子と前記接地線との間に接続された第2のフォトダイオード42とを有する。

(もっと読む)

1 - 20 / 31

[ Back to top ]