Fターム[5B018GA02]の内容

記憶装置の信頼性向上技術 (13,264) | 目的 (2,614) | エラー訂正 (431)

Fターム[5B018GA02]に分類される特許

201 - 220 / 431

半導体記憶装置

【課題】高速での読み出し処理が可能な半導体記憶装置1を実現する

【解決手段】NAND型フラッシュメモリを有する半導体メモリ部3の回路の異常を検知する検知回路12と、対数尤度比λを用いて軟判定復号する誤り訂正符号により符号化されたデータの復号処理を行う誤り訂正回路15とを有し、検知回路12の情報に基づいて、データから生成される対数尤度比初期値λ0が修正される。

(もっと読む)

情報処理装置、該装置用のROMイメージ生成装置、および転送装置

【課題】メインプログラムをNAND型フラッシュメモリに格納する情報処理装置において、ブートストラッププログラムをNOR型フラッシュメモリに格納すると、システムのコストが高くなる。

【解決手段】電源投入後、転送装置14は、第1の記憶装置11に格納された、第1の誤り検査符号114付きのブートストラッププログラム111を検出し、誤り検出/訂正処理を施して第2の記憶装置12に転送する。転送が正常に完了した場合、CPU10は、第2の記憶装置12上のブートストラッププログラム111を実行することにより、第2の誤り検査符号115付きのメインプログラム112に誤り検出/訂正処理を施して第3の記憶装置13に転送し、第3の記憶装置13上のメインプログラム112に分岐する。これにより、NOR型フラッシュメモリを使用せずに、システムブートを行える。

(もっと読む)

不揮発性メモリ管理装置

【課題】不揮発性メモリ装置への付加回路を少なくしてメモリ装置の信頼性を部分的に高めることを可能とする。

【解決手段】アドレス/モード記憶部110を設け、アドレスにより決定される管理モードによりデータバッファ200と不揮発性メモリ30との間で入出力されるデータ部分のデータ長を変更できるように制御することで、読み出されたデータに付加されるECCコードで訂正可能なデータの割合を増加させることができて、指定した領域に記憶されたデータの信頼性を向上させる。

(もっと読む)

メモリ装置及びメモリ制御方法

【課題】汎用のDIMM製品を利用でき、チップ故障を含めてデータの訂正ができ、高速・高信頼性を実現する。

【解決手段】ECC(誤り訂正符号)として任意のバイト数を指定する手段を有し、データと誤り訂正符号は、メモリ上で同一ワード上に存在する。

(もっと読む)

マイクロプロセッサ

【課題】マイクロプログラムの読出し時にSEUを生じた場合においても対処できるマイクプロセッサを得る。

【解決手段】マイクロプログラム格納ROM1に格納されるマイクロ命令にパリティを付加する。パリティチェック回路5は、マイクロ命令レジスタ4に格納されたマイクロ命令のパリティチェックを行い、エラー検出時はパリティエラー検出信号を送出する。マイクロ命令実行部6は、パリティチェック回路5からパリティエラー検出信号が送出された場合は、例えば、マイクロプロセッサの実行を停止させる。

(もっと読む)

不揮発性半導体記憶部を含む記憶システム

【課題】決められた時間内にリフレッシュを行うことで、定期的にデータの誤りを復元するだけでなく、アプリケーションプログラム実行中に致命的な不良が起こらないように、緊急リフレッシュを行うことができる。

【解決手段】不揮発性半導体記憶部を含む記憶システムは、データの再書込み可能な不揮発性メモリセル群からなる記憶領域を有する情報記憶部と、情報記憶部の記憶領域から読出されるデータのエラーを検出し、エラーを訂正して出力する誤り検出訂正回路と、検出されたデータのエラーを計数する誤り個数カウンタと、情報記憶部からのデータ読出しを計数する読出回数カウンタと、読出されるデータの誤り個数に応じて、データを訂正し、再書込みを行い、更に、データの誤り個数カウンタの計数値と読出回数カウンタの計数値をリセットするリフレッシュ制御手段とを備える。

(もっと読む)

メモリ装置、及び、その制御方法

【課題】不揮発性メモリセルを含むメモリ装置にて、メモリセル領域の増大を伴うことなく、データの信頼性を向上させることができるメモリ装置を提供する。

【解決手段】メモリ装置は、不揮発性メモリセル103と、2つの揮発性メモリセル104、105を有する。書込み制御部102は、不揮発性メモリセル103及び揮発性メモリセル104、105にデータ書込む。揮発性メモリセル104、105には、不揮発性メモリセル103が保持するデータと同じデータが書き込まれる。データ管理部106は、不揮発性メモリセル103、揮発性メモリセル104、105が保持するデータを比較し、整合が取れているか否かを判断する。整合が取れていないと判断すると、不整合となるデータを保持するメモリセルに、本来メモリセルが保持すべきデータを書き込むように、書込み制御部102に指示する。

(もっと読む)

メモリシステム

【課題】不揮発性半導体記憶素子を用いて構成されるメモリシステムにおいて、記憶デー

タの信頼性の低下を抑止すること。

【解決手段】クラスタ以下の単位で書き込み/読み出しを行うDRAMと、ページ単位で

書き込み/読み出しを行うNANDと、が具備される。データ管理部は、NANDにある

ページ単位毎の読み出しデータを読み出した際、読み出しエラーが起こった場合には、記

憶バッファに格納されている誤り訂正の結果に基づいて当該読み出しデータに対するエラ

ー訂正の成功/失敗を判断し、エラー訂正が成功した場合には、記憶バッファに格納され

ている当該読み出しデータに対する訂正データを書き込み、エラー訂正が失敗した場合に

は、エラー訂正処理を行っていない当該読み出しデータそのものを書き込む。

(もっと読む)

アドレスエラー検出装置、アドレスエラー検出方法

【課題】メモリ回路のアドレスデコード部で発生する障害を高確率で検出できる小面積のアドレスエラー検出装置およびアドレスエラー検出方法を提供する。

【解決手段】Xデコーダ103の出力から複数ビットの冗長符号を生成するX符号化器105と、Yデコーダ104の出力から前記冗長符号と同じビット数の冗長符号を出力するY符号化器106と、X符号化器105の出力10とY符号化器106の出力11を各ビット排他的論理和するXOR回路107と、XOR回路107の出力12とアドレス信号1を入力し、誤り検出を行う誤り検出器108と、を備える。X符号化器105とY符号化器106、およびXOR回路107によって、アドレス信号をハミング符号化した冗長部12を生成する。誤り検出器108では、元のアドレス信号と生成された冗長符号に対して検査行列の掛け算を行い、エラーが発生したか否かを検出し、エラー出力3を得る。

(もっと読む)

半導体記憶装置、その制御方法、および誤り訂正システム

【課題】誤り訂正能力を損なうことなく消費電力及び回路規模を低減することが可能な半導体記憶装置、その制御方法、および誤り訂正システムを提供することを目的とする。

【解決手段】SSD100のECC回路40は、読み出しデータに対して、第1誤り訂正符号(ハミング符号)を用いて第1誤り訂正し、この第1誤り訂正結果を、第2誤り訂正符号(BHC符号)を用いてさらに第2誤り訂正し、さらに、第2誤り訂正結果を、第3誤り訂正符号(RS符号)を用いて第3誤り訂正する。

(もっと読む)

情報処理装置および不揮発性半導体メモリドライブ

本願発明の情報処理装置は、情報の書込みおよび情報の読出しが可能な複数の記憶領域を有する不揮発性半導体メモリと、記憶領域に記憶された情報についてセクタ毎に誤り訂正を行う第1の誤り訂正処理と記憶領域に記憶された情報についてクラスタ毎に誤り訂正を行う第2の誤り訂正処理とを実行制御し、この第1の誤り訂正処理および第2の誤り訂正処理によっては訂正できないエラーが発生した場合、当該エラーを含む情報と当該情報に含まれるエラーを訂正するための誤り訂正符号とをホスト装置に送信して誤り訂正を依頼する制御部とを備えたSSDを有する。  (もっと読む)

(もっと読む)

不良メモリを検出する電子機器、不良メモリ検出方法およびそのためのプログラム

【課題】メモリエラー統計機能を有するハードウェアを使って得られたメモリエラーの種別を用いてメモリエラー発生回数を正確に計数し不良メモリを検出する。

【解決手段】CPU11とメモリ12とエラー訂正機能を有するメモリコントローラ13とを備えた不良メモリ検出装置1は、CPU11からメモリ12に書込まれたデータに基づき検出したメモリエラーの発生回数Nを計数するカウンタ140と、メモリエラーの発生回数Nが>T(Tは所定回数)のとき、訂正可能な種別によるメモリエラーの発生回数Nのカウンタ140による計数を禁止し、メモリエラーの発生の有無を判定し、メモリエラーの発生が無いと判定されたとき、カウンタ140による計数の禁止を解除してメモリエラーの発生回数を再び計数し、メモリの不良を判定する処理部150とを有する。

(もっと読む)

制御装置

【課題】ECCメモリに記憶されたデータの誤り訂正がされないまま蓄積されることを防止できる制御装置を提供することである。

【解決手段】通常動作でアクセスされる通常動作時領域12および通常動作でアクセスされない非通常動作時領域13とを有したECCメモリ11と、通常動作時にECCメモリ11の通常動作時領域12を使用して制御演算処理を行う制御タスク処理手段14と、定周期でECCメモリ11の全体領域を記憶する定周期メモリ修正タスク処理手段15とを備える。

(もっと読む)

半導体メモリコントローラおよび半導体メモリ

【課題】 リードライトの信頼性の高い半導体メモリコントローラおよび前記半導体メモリコントローラを有する半導体メモリを提供する。

【解決手段】 メモリ部に記憶するデータを、N(ただし、Nは偶数)ビット幅のバスを介して、メモリ部へ出力する半導体メモリコントローラであって、データの2重化処理を行い、それぞれのデータを、N/2ビット幅にて、同時にメモリ部の2箇所に出力し、メモリ部の2箇所に記憶する。

(もっと読む)

PLC用の部品実装基板

【課題】 バックアップ機能付きのIOメモリ仕様とECC機能付きのIOメモリ仕様とに低コストに対応可能としたPLC用の部品実装基板を提供すること。

【解決手段】 ASIC(4)に対するモード指定の選択、第1及び第2のメモリ装着部に対して装着されるべきSRAM(5,6)種別の選択、第1及び第2のメモリ装着部に対するバッテリバックアップ有無の選択、及び第2モード指定時のメモリ割付ルールの取り決めにより、バックアップ機能付きのIOメモリ仕様とECC機能付きのIOメモリ仕様とに対応可能とした。

(もっと読む)

情報処理装置及びその制御方法

【課題】データの信頼性を確保しつつ、メモリアクセス時間及びコストを低減させる情報処理装置を提供する。

【解決手段】本情報処理装置は、同一の情報を複数のメモリに書き込む際に、少なくとも1つのメモリに書き込まれるデータが書き込み中のノイズの影響を受けないように、各書き込み開始タイミングをずらす。一方、本情報処理装置は、複数のメモリから当該データを読み込んだ際に、各データを比較して、正常なデータを推定する。

(もっと読む)

分散格納方法および装置

【課題】バックアップやデータ格納を複数の外部センタに高いセキュリティを維持した状態で分散アウトソーシングできるようにする。

【解決手段】オリジナルデータをネットワークを介して接続された2以上の分散された格納装置(バックアップサイト)に分散格納する際に、データを所定ビット毎に読み出して、読み出されたデータを所定の論理で2以上の分割データに分割し、前記分割データ毎に前記2以上の格納装置に転送する。所定の論理とは、前記データを分割する際に、当該データを所定のまとまり毎にローテイト分割する。このローテイト分割は、所定のデータのまとまり毎にパリティを設定し、当該パリティの数値によってローテイト方向を変更する。このように、それぞれストレージを持った複数のサーバに細かい単位で分割してデータを保存することにより、各サーバ内のストレージを参照しても単体では解読不可能なシステムが実現する。

(もっと読む)

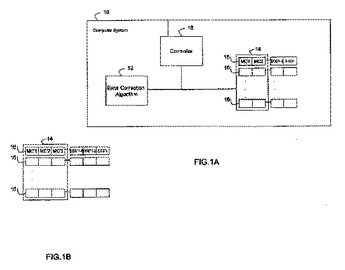

メモリアレイにおけるエラー訂正

メモリアレイでエラーを訂正するコンピュータシステムは、エラー訂正アルゴリズムとメモリとを含む。エラー訂正アルゴリズムは、標準サイズを有する訂正可能なメモリセルグループで第1のビット誤り率までエラーを訂正できる。メモリは、第1のメモリセルグループに対応する情報を有する第1のECCビットセットを格納し、かつ第2のメモリセルグループに対応する情報を有する第2のECCビットセットを格納するべく機能し、第1のメモリセルグループは標準サイズより大きい第1のサイズを有し、第2のメモリセルグループは前記第1のサイズより小さい第2のサイズを有し、かつ前記第1のグループの一部分をなす。エラー訂正アルゴリズムは、第1のECCビットセットに基づく第1のグループの訂正に失敗した場合に、第2のECCビットセットに基づき第2のグループでエラーを訂正するべく機能する。  (もっと読む)

(もっと読む)

レートコンパチブルパンクチャドコードをサポートするメモリコントローラ

装置および方法により、レートコンパチブル畳み込みコード(RPCC)などの、レートコンパチブルコードに従って、不揮発性ソリッドステートメモリデバイス(100)にデータが格納される。このようなメモリデバイス(100)の一例は、フラッシュメモリデバイス(100)である。データを、まず、エラー訂正および検出のためにブロックエンコードすることができる(112)。ブロックコード化されたデータを、さらに畳み込みエンコードすることができる(114)。畳み込みコードされたデータを、パンクチャリングし(116)、メモリデバイス(100)に格納することができる。パンクチャリングにより、データを格納するために使用されるメモリ量が減少する。状況に応じて、パンクチャリング量は、パンクチャリングが行われない量から比較的高いパンクチャリング量まで変化して、さらなるエラー訂正量の提供および使用されるメモリ量を変化させることができる。データをメモリデバイス(100)から読み出すとき、パンクチャドデータをデコードすることができる(120、122)。  (もっと読む)

(もっと読む)

フォールトトレラント不揮発性集積回路メモリ

NANDフラッシュなどの、複数の不揮発性集積回路メモリデバイス(306)中に、畳込み符号化を用いてデータを記憶するような装置および方法が開示される。畳込み符号(108/1 10)に対する比較的高い符号化率は、ほんのわずかしか余分なメモリ空間を消費しない。ある実施形態では、畳込み符号(108/1 10)は、特定のメモリデバイスの一ページに集められているよりむしろ、複数のメモリデバイス(106)の部分に分配される。ある実施形態では、m/nの符号化率が用いられ、畳込み符号はn個のメモリデバイス(106)にわたって記憶される。  (もっと読む)

(もっと読む)

201 - 220 / 431

[ Back to top ]