Fターム[5B018GA02]の内容

記憶装置の信頼性向上技術 (13,264) | 目的 (2,614) | エラー訂正 (431)

Fターム[5B018GA02]に分類される特許

121 - 140 / 431

電子機器

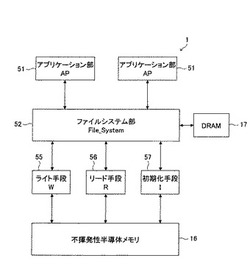

【課題】電子機器では、フラッシュメモリなどの不揮発性半導体メモリを電子機器の記憶部として実用可能にすることが求められている。

【解決手段】電子機器1は、データ書込み処理において既に書込まれたデータに対する上書きが禁止されている不揮発性半導体メモリ16を有し、実データおよび当該実データに対応した管理データを記憶する第1記憶部53と、データ書込み処理において任意の値へのデータ上書きが可能な第2記憶部54と、第1記憶部53に対するデータアクセスを制御する制御部52とを有する。制御部52は、第1記憶部53に記憶されている管理データを、第2記憶部54にコピーし、第2記憶部54に記憶されている管理データを参照して、第1記憶部53の実データにアクセスする。

(もっと読む)

不揮発性メモリおよびメモリシステム

【課題】退避したデータと同じアドレスに読み出しが発生した場合には、退避した訂正済みデータを出力することが可能な不揮発性メモリおよびメモリシステムを提供する。

【解決手段】メモリ領域210へのアクセスを制御する制御部220を有し、制御部220は、データ領域から読み出したデータの誤りを検出して訂正機能を有する誤り検出訂正機能と、指定されたアドレスのデータおよびECCをメモリ領域から読み出し、誤りを検出した場合には、そのアドレスと訂正済みデータを保持する退避領域227と、退避領域に保持しているアドレスと訂正済みデータが有効であるか無効であるかを示す有効無効提示部と、を含み、新たなアドレスと訂正済みデータが退避領域に登録された場合には、有効無効提示部を有効に設定し、退避領域に保持されているデータが不要になった場合には、有効無効提示部を無効に設定する。

(もっと読む)

メモリカード及びデータ処理装置並びにメモリカードの制御方法及び設定方法

【課題】メモリカードにおけるメモリカードの誤り訂正処理に起因する問題を解決するメモリカード及びメモリカードに対する制御方法等を提供する。

【解決手段】メモリカードは、データ処理装置との間でコマンドやデータの送受信を行うホストインタフェース(2)と、データを格納する不揮発性メモリ(7)と、メモリカードの動作を制御するコントローラ(3)と、所定の管理情報を格納する記憶手段(32)とを備える。管理情報は、不揮発性メモリからのデータの読み出し時に誤り訂正機能を実行するか否かを指定するための誤り訂正設定情報を含む。コントローラは、データ読み出し動作時に、誤り訂正設定情報を参照し、誤り訂正設定情報が誤り訂正機能の停止を示す場合は、読み出したデータに対して誤り訂正を行わないように、また、誤り訂正設定情報が誤り訂正機能の作動を示す場合は、読み出したデータに対して誤り訂正を行うように、読み出し動作を制御する。

(もっと読む)

エラー検出・訂正符号生成回路及びその制御方法

【課題】 簡易な構成でエラー検出・訂正符号付きデータを生成することが課題である。

【解決手段】 各バイトがnビットを有するmバイトの情報部分とmバイトの情報部分に設けられるmビットのエラー検出用ビットの冗長部分とを含むエラー検出用ビット付きデータのmバイトの情報部分の排他的論理和演算を行い、エラー検出・訂正符号付きデータの冗長部分のうち、log2(n+1)ビットの一の部分を生成し、生成した一の部分とエラー検出用ビットとを入力してmビットの他の部分を生成する。

(もっと読む)

メモリ装置

【課題】NAND型フラッシュメモリとRAMとの間で高速にデータ転送を行うことができるメモリ装置を提供すること。

【解決手段】本発明は、複数の実データを記憶するための実データエリアと複数のスペアデータを記憶するためのスペアデータエリアを含む不揮発性メモリ701と、

複数の実データを記憶するための実データエリア712と複数のスペアデータを記憶するためのスペアデータエリア713を含む揮発性メモリ711と、不揮発性メモリ701及び揮発性メモリ711の間のデータ転送を行うコントローラ721とを有するメモリ装置である。

(もっと読む)

キャッシュシステム

【課題】エラー訂正データの書き戻しのために特別なサイクルを消費せず、特別な記憶素子などを追加せず、CPUの割り込み機能を必要とせず、キャッシュ制御回路のみで訂正データの書き戻しを実現する。

【解決手段】Dirty判定処理を行うブロックに、訂正可能エラー発生条件を追加条件として新たに設けた。これにより、本来発生するライトバック動作に付随して訂正データの主記憶への書き戻しが可能になった。

(もっと読む)

不安定メモリセル散布を検出するメモリ・システム及びその検出方法

【課題】不安定なスレショルド電圧を有したメモリセルが多く存在するページを検出する不安定メモリセル散布を検出するメモリ・システム及びその検出方法を提供する。

【解決手段】本発明のメモリ・システムは、SSD及びメモリ・コントローラを具備し、SSDは複数個のメモリセルを含み、メモリ・コントローラは、SSDにデータを記録して記録されたデータを読み取る機能を遂行し、SSDに標準読み取り電圧及び標準読み取り電圧と一定の電圧準位の差がある修正読み取り電圧を印加し、標準読み取り電圧及び修正読み取り電圧を利用してSSDに保存されたデータの散布を分析し、SSDに保存されたデータの有効性如何を判断して該SSDに保存されたデータを矯正する機能を遂行する。

(もっと読む)

メモリシステムおよびメモリシステムの制御方法

【課題】処理速度の速いメモリシステムおよびメモリシステムの制御方法を提供する。

【解決手段】複数のセクタデータからなるフレームデータを記憶するメモリカード10と、メモリカード10とフレームデータを送受信するホスト2とを有し、メモリカード10が、セクタデータ単位で、硬判定符号によるBCH復号処理を行うECC1デコーダ30と、フレームデータ単位でLDPC符号によるLDPC復号処理を行うECC2デコーダ40と、BCH復号処理における誤りデータ有無の情報を記憶するセクタエラーフラグ部44と、セクタエラーフラグ部44の情報に基づき、LDPC復号処理における誤りデータの無いセクタデータの信頼度を増加する制御を行うECC制御部21と、を具備する。

(もっと読む)

データ蓄積装置及びデータ書込み/読出し方法

【課題】メモリチップが故障した場合であっても、データを復元することが可能なデータ蓄積装置及びデータ書込み/読出し方法を提供する。

【解決手段】誤り検出部13−1〜13−4は、RAID制御部12からの書込みデータに対して1ページ単位で誤り検出符号を付加する。そして、メモリユニットは、誤り検出符号が付加された書込みデータを1ページ単位で半導体メモリに書き込む。また、誤り検出部13−1〜13−4は、読出し時には、メモリユニット14−1〜14−4からの読出しデータにデータ誤りがあるか否かを、誤り検出符号に基づいて行う。RAID制御部12は、データ誤りが検出された場合、誤りが検出された読出しデータを、他の読出しデータに基づいて復元する。

(もっと読む)

メモリ制御装置

【課題】メモリに格納されるデータの信頼性を向上させるようにメモリを制御するメモリ制御装置を提供すること。

【解決手段】ブロック領域判定部31は、MRAMに対するアクセスが、MRAMの複数の領域のどの領域に対するアクセスであるかを判定する。アクセス頻度カウンタ更新部32は、ブロック領域判定部31によって判定された領域情報に基づいて、複数の領域ごとにアクセスされなかった頻度をカウントする。リフレッシュ領域判定部33は、アクセス頻度カウンタ更新部32によって複数の領域ごとにカウントされたアクセスされなかった頻度に応じて、リフレッシュが必要な領域を判定する。したがって、データの訂正が不可能となる前に誤ったデータを訂正して書き戻すことができ、MRAMに格納されるデータの信頼性を向上させることが可能となる。

(もっと読む)

プロセッサ

【課題】アドレス比較回路等を不要にしてフォワーディング回路の規模を小さくして、半導体チップ上のフォワーディング回路の占める面積の小さいプロセッサを提供する。

【解決手段】プロセッサ1は、ALU11と、ロード/ストアユニット13と、タイマ13aと、ECC計算器13bと、複数のECCレジスタ13cと、を有する。ロード/ストアユニット13は、主メモリ14にデータを書き込む時に、書き込みデータとタイマ13aのカウント値とを主メモリ14に書き込むと共に、その書き込みデータについてのECCが正しくないことを示すECC状態フラグデータを主メモリ14にセットし、そのセット後、ECC計算器13bに書き込みデータについてのECCを計算させ、ECCが計算して得られた後、その計算して得られたECC主メモリ14に書き込むと共に、ECC状態フラグデータをリセットする。

(もっと読む)

不揮発性ランダムアクセスメモリおよび不揮発性メモリシステム

【課題】ランダムアクセス可能でありながら電源を切った後もデータ保持可能で、アプリケーションに応じたECCの付加が可能な不揮発性ランダムアクセスメモリおよび不揮発性メモリシステムを提供する。

【解決手段】NVRAM21は、ランダムアクセス可能で、データ領域と、エラー訂正(ECC)コードを保存するためのECC領域の2つの領域を含む不揮発性記憶領域211と、データ領域にアクセスする際に使用するデータサイズをデータ領域単位サイズとして外部から設定するための不揮発性記憶領域設定機能を実現する不揮発性記憶領域制御部212と、を有し、不揮発性記憶領域制御部212は、設定されたデータ領域単位サイズに従ってデータ領域とECC領域を管理し、データ領域単位サイズごとに、上記不揮発性記憶領域制御部が設定したECC領域単位サイズのECC領域を割り当てる機能を含む。

(もっと読む)

電子機器及びプログラム

【課題】落下や水没等の様な特殊な状態になったことを検出して内部のデータをバックアップする機能を備えているとともに、バックアップされたデータが漏洩されることを防止し得るようにする。

【解決手段】特殊状態検出部13は、携帯電話装置1の落下や水没等の特殊状態を検出して検出信号を中央制御部2に送出する。中央制御部2は検出信号を受けてアプリ情報記憶部11に記憶されている情報をバックアップメモリ12にバックアップさせたり、無線通信部4を介してネットワーク上のサーバなどにバックアップさせたりする。その後、携帯電話装置1に異常があるかを判断し、異常が無い場合にはバックアップメモリ12やサーバなどにバックアップされたバックアップデータを削除して、バックアップデータが漏洩するのを防止する。

(もっと読む)

データ処理装置

【課題】動作速度を向上させることが可能なECC機能付きSRAMを搭載したデータ処理装置を提供すること。

【解決手段】データRAM12は、バスクロック20に同期してデータが書き込まれる。ECC部13は、データRAM12に書き込まれるデータに基づいてECCコードを生成する。クロック微調整回路17は、バスクロック20を遅延して出力する。そして、ECCRAM15は、クロック微調整回路17によってバスクロックを遅延したECCRAMクロックに同期して、ECC部13によって生成されたECCコードが書き込まれる。したがって、ECCRAM15にECCコードを書き込むタイミングをデータRAM12にデータを書き込むタイミングよりも遅らすことができ、ECC機能付きSRAMの動作速度を向上させることができる。

(もっと読む)

メモリ記憶装置

【課題】ホスト装置が不揮発性メモリから記憶情報を読出さずに不揮発性メモリのデータ保持に対する信頼性を向上させる。

【解決手段】本発明に係るメモリ記憶装置は不揮発性メモリ(2)とメモリコントローラを有する。メモリコントローラは、ホストインタフェース回路(10)、メモリインタフェース回路(12)及び制御回路(11,13,14)を有する。制御回路は第1〜3処理を制御可能である。第1処理は書込みデータにエラー訂正コードを付加したデータをメモリインタフェース回路から書込み制御情報と共に出力する。第2処理は読出し制御情報に従いエラー検出・訂正したデータをホストインタフェース回路から出力する。第3処理は読出し制御情報に従いエラー検出・訂正したデータを書込み制御情報と共に出力する。メモリコントローラは、第3処理において、エラー発生回数が所定回数を超えたときエラー訂正された読出しデータの記憶領域を変更する。

(もっと読む)

不揮発性記憶装置および不揮発性メモリコントローラ

【課題】全消去検出回路の出力と書き込みマークの有無に基づいて書き込み状態を制御回路によって判定することによって、正確に書き込み途中の電源遮断等の異常を検出することのできる信頼性の高い不揮発性記憶装置及びその書き込み判定方法を提供する。

【解決手段】不揮発性メモリから書き込み単位のデータを読み出す際に、全消去検出部によって読み出しデータが消去済みであるかどうかを判定すると共に、デスクランブル処理部によりデスクランブルされさらに誤り検出訂正部によって誤り訂正を行った後のデータの書き込み済みフラグ領域がフラグ書き込み済みであるかどうかを判別し、スクランブルパターン発生部によって生成される前記書き込み済みフラグ領域に対応するスクランブルパターンが、前記所定のビットパターンを消去済みの状態とは異なる状態にスクランブルする。

(もっと読む)

半導体記憶装置およびその制御方法

【課題】誤り訂正能力を損なうことなく消費電力および回路規模が抑制された半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、複数の第1データ内の誤りをそれぞれ検出するための複数の検出符号を生成する複数の検出符号生成部41乃至48と、各第1データとこれに対応する検出符号とから第1単位データが構成され、複数の第1単位データ内の誤りをそれぞれ訂正するための複数の第1訂正符号を生成する複数の第1訂正符号生成部61乃至68と、前記複数の第1単位データから第2単位データが構成され、この第2単位データ内の誤りを訂正するための第2訂正符号を生成する第2訂正符号生成部8と、第2単位データ、複数の第1訂正符号、及び第2訂正符号を不揮発に格納する半導体メモリ2とを含む。

(もっと読む)

メモリ制御装置および携帯端末装置

【課題】不揮発性メモリ内のデータの正常化を効果的に図ることができるメモリ制御装置を提供する。

【解決手段】携帯電話機は、NAND型のEEPROM201と、EEPROM201からデータの読み出すメモリコントローラ301と、読み出したデータに対してエラー訂正処理を行うECC回路302と、ECC回路302によりエラー訂正がなされた物理ブロック201a内の全データを正常なデータに書き換える書換え処理部100aとを備えている。

(もっと読む)

ストレージサブシステム

【課題】 データの更新に伴う処理を、キャッシュメモリを制御対象とする制御部と不揮発性半導体メモリを制御対象とするメモリコントローラに分散して行うこと。

【解決手段】 フラッシュメモリ44のデータを更新するときに、主プロセッサ18は、XORライトコマンド100を生成してフラッシュメモリコントローラ42に転送し、フラッシュメモリコントローラ42のマイクロプロセッサ48は、XORライトコマンド100を解析して、フラッシュメモリ44のユーザ領域74のページ72から旧パリティ96を読み出し、読み出した旧パリティ96と、旧データである「b」のデータ78および新データである「d」のデータ78を用いて排他的論理和演算を行って新パリティ98を生成し、生成した新パリティ98をパリティ格納用フラッシュメモリ44の更新領域76のページ72に格納する。

(もっと読む)

管理型不揮発性メモリのための低レイテンシ読み取り動作

メモリシステムにおいて、ホストコントローラは、不揮発性メモリ(NVM)パッケージ(例えば、NAND装置)に結合される。ホストコントローラは、低レイテンシの読み取り動作を要求する読み取りコマンドをNVMパッケージへ送信する。読み取りコマンドに応答して、NVMパッケージのコントローラは、データを検索し、そしてデータを修正のためにECCエンジンへ送信する。読み取りコマンドに続いて、ホストコントローラは、読み取り状態要求コマンドをNVMパッケージのコントローラへ送信する。その読み取り状態要求に応答して、コントローラは、幾つかの又は全てのデータをホストコントローラへの転送に利用できることを指示する状態レポートをホストコントローラへ送信する。このレポートに応答して、ホストコントローラは、データを転送する。未修正のデータがホストコントローラへ転送されたことを指示するためにアンダーラン状態を決定することができる。 (もっと読む)

121 - 140 / 431

[ Back to top ]