Fターム[5B018GA02]の内容

記憶装置の信頼性向上技術 (13,264) | 目的 (2,614) | エラー訂正 (431)

Fターム[5B018GA02]に分類される特許

61 - 80 / 431

サーバ装置、メモリ装置

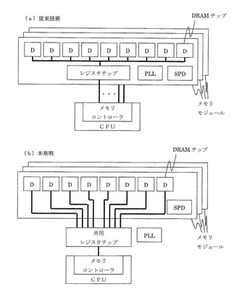

【課題】レジスタチップを搭載するためのコストを抑えつつ、メモリモジュールとメモリコントローラの間の通信を安定化させることのできる技術を提供する。

【解決手段】本発明に係るサーバ装置は、複数のメモリモジュールに対する命令を格納する共用レジスタを備える。メモリコントローラは、複数のメモリモジュールに対する命令を共用レジスタに格納し、共用レジスタは、メモリコントローラから受け取った命令を複数のメモリモジュールに対して並列出力する。

(もっと読む)

NANDフラッシュ・メモリにおける確率論的多層エラー訂正のためのシステム、方法、およびコンピュータ・プログラム

【課題】メモリからデータを検索するためのシステム、方法、およびコンピュータ・プログラムを提供する。

【解決手段】メモリからデータを検索するためのシステムを含むNANDフラッシュ・メモリにおけるエラー訂正。このシステムは、メモリと通信するデコーダを含む。デコーダは、メモリにおけるページ上に記憶されたコードワードを受信することを含む方法を実行するためのものであり、コードワードは、データおよびこのデータに応じて発生された第1の層のチェック・シンボルを含む。この方法は更に、コードワードが第1の層のチェック・シンボルを用いて訂正することができないエラーを含むと判定することを含み、これに応じて、第2の層のチェック・シンボルを受信する。第2の層のチェック・シンボルは、データの受信に応じて、更にコードワードを含むページよりも前に書き込まれたメモリにおける他のページの内容に応じて発生させる。第2の層のチェック・シンボルに応じてコードワードを訂正する。訂正したコードワードを出力する。

(もっと読む)

アクセス制御装置、誤り訂正制御方法およびストレージ装置

【課題】データの信頼性を高くすることを課題とする。

【解決手段】NAND−Flashメモリコントローラ10は、NAND−Flashメモリ20に記憶されたデータの消去に要した時間を計測し、計測された時間に応じて、誤り訂正符号のデータサイズを決定する。そして、NAND−Flashメモリコントローラ10は、決定されたデータサイズの誤り訂正符号を生成し、生成された誤り訂正符号をNAND−Flashメモリ20に書き込むように制御する。

(もっと読む)

データ記憶装置、メモリ制御装置及びメモリ制御方法

【課題】有効なデータが準備できないチャネルがある場合でも、ライト処理効率の低下を招くことなく、確実に誤り訂正符号データを生成できるデータ記憶装置を提供することにある。

【解決手段】実施形態によれば、データ記憶装置は、ライトコントローラと、誤り訂正コントローラと、データコントローラとを具備する。ライトコントローラは、複数チャネルの各不揮発性メモリにデータを並列に書き込む。誤り訂正コントローラは、前記ライトコントローラによる書き込み動作の前に、前記各チャネル毎に準備されるデータを使用して誤り訂正符号データを生成する。データコントローラは、不揮発性メモリの書き込み対象のデータが準備されないチャネルに対して、当該不揮発性メモリの初期値データを前記誤り訂正コントローラの生成処理に使用するデータとして準備する。

(もっと読む)

フラッシュメモリ装置及びそれの読み出す方法

【課題】エラー訂正に所要される性能損失は最少化しながら、エラー訂正の効率は増進させ得るフラッシュメモリ装置及びそれの読み出すための方法が提供される。

【解決手段】本発明のフラッシュメモリの読み出す方法は、ソフト判定読出しコマンドとアドレスとに応答して対応されるフラッシュメモリセルから複数の読出し動作を遂行する段階と、前記複数の読出し結果からハード判定データと、1つ又はその以上の信頼性データビットを決定する段階と、連続的に発生した複数のソフト判定出力コマンドに応答して、前記ハード判定データと、前記信頼性データの各ビットを最上位ビットから最下位ビット順に順次的に出力する段階と、を含み、前記順次的に出力された前記ハード判定データと前記信頼性データの各ビットとはエラー訂正回路に提供されて前記ハード判定データを適用したエラー訂正動作と、前記信頼性データの各ビットを利用する複数のエラー訂正動作に段階的に適用され、前記ソフト判定出力コマンドは前記複数のエラー訂正動作結果にしたがって選択的に発生し得る。

(もっと読む)

同時読み出し及び書き込みメモリ動作を実行する方法及び装置

【課題】特定のデータパーティションに書き込む動作が、同じデータパーティションから読み出す動作の完了まで一時停止(サスペンド)される必要はないメモリデバイスを提供する。

【解決手段】メモリデバイス300のデータパーティション310においてリード・ホワイル・ライト方式の動作を同時に実行する技術は、メモリの個々のデータパーティションのコンテンツに少なくとも部分的に基づいてECCを計算することを含み、メモリのメモリアレイの個々のメモリパーティションの特定の1つの第1の部分の特定のコンテンツを、前記個々のメモリパーティションの前記特定の1つの第2の部分に書き込む間に、読み出すことを具備し、前記読み出すことは、前記個々のメモリパーティションのコンテンツに少なくとも部分的に基づいた誤り訂正符号(ECC)に少なくとも部分的に基づいた前記第1の部分の前記特定の部分を決定する。

(もっと読む)

ミラー化データ・ストレージ・システムにおけるエラーを検出するための方法、コンピュータ・プログラム及びシステム

【課題】ミラー化データ・ストレージ・システムにおいてエラーを検出するための方法及びシステムを提供する。

【解決手段】ミラー化データ・ストレージ・システムは、第1のエラー検出及び訂正コード(ECC)アルゴリズムを適用する第1のミラー化システム及び第2のECCアルゴリズムを適用する第2のミラー化システムを備える。本方法は、第1及び第2のミラー化システムの各々における回復済みデータを読み取り、4つの計算済みECC値を生成するように第1及び第2のECCアルゴリズムの両方を適用することにより、第1及び第2のミラー化システムの各々における回復済みデータを処理する。本方法は、計算済みECC値を使用して、第1及び第2のミラー化システムの正しい回復済みデータを決定する。

(もっと読む)

キャッシュメモリシステム

【課題】よりソフトエラーの影響を抑えることのできるキャッシュメモリシステムを提供する。

【解決手段】キャッシュメモリをライトスルー方式で動作させると共に、キャッシュミス発生時の動作を、キャッシュメモリに対応するデータが無い場合か、データがあってもエラーが発生している場合に行なうようにする。そして、キャッシュメモリに、以前にソフトエラーが発生したことを示すビットを立てておき、このビットが”1”のときに、再び、エラーが発生した場合には、ハードウェアのエラーが発生していると判断して、CPUに割り込みをかけるようにする。このビットは、ソフトエラーが発生すると考えられる頻度よりも十分短い時間間隔でリセットされるようにする

(もっと読む)

不揮発性半導体メモリ装置とデータ誤り訂正方法

【課題】誤り訂正回路の大きさを抑制する誤り訂正方法と誤り訂正装置を実現する。

【解決手段】

誤り訂正単位210は誤りビットの個数が少ないページ内の一領域であり、誤り訂正単位220は誤りビットの個数が多いページ内の一領域である。誤り訂正単位210は、ユーザデータ領域211と第1冗長領域212と第2冗長領域213とを含んでいる。また、誤り訂正単位220は、ユーザデータ領域221と第1冗長領域222と第2冗長領域223とを含んでいる。そして、ユーザデータ領域211及び221にある誤りを訂正するための第1組の冗長ビットは第1冗長領域212及び222にそれぞれ記憶される。誤りビットの個数が多いページ内のユーザデータ領域221にある誤りを訂正するための第2組の冗長ビットは、誤りビットの個数が少ないページ内の第2冗長領域213及び誤りビットの個数が多いページ内の第2冗長領域223に分散されて記憶される。

(もっと読む)

メモリ制御装置、記憶装置、及びメモリ制御方法

【課題】多チャネルによるリード/ライトを適切なタイミングで行いパフォーマンスを向上できる。

【解決手段】チャネル毎のキューは、記憶媒体に対するデータの書込命令を保持する。第1の制御手段は、複数のチャネルのキューに書込命令が保持され、複数のチャネルを同期させた上で書込命令の処理が可能になるまでの間に、記憶媒体に対するデータの読出命令を受け付けた場合に、当該読出命令によるデータの読み出し処理を、書込命令より優先して行わせ、複数のチャネルで書込命令の処理が可能になった場合に、複数のチャネルを同期させた上で書込命令によるデータの書き込み処理を行わせる。生成手段は、書込命令による処理を行う際、複数のチャネルで書き込まれるデータに基づいて、複数のチャネルで書き込まれたデータの誤りを検出および訂正するためのエラー訂正符号を生成する。第2の制御手段は、エラー訂正符号を、記憶媒体に書き込む処理を行う。

(もっと読む)

半導体メモリ装置および半導体メモリシステム

【課題】製品寿命の長いメモリカード2を提供する。

【解決手段】実施形態のメモリカード2は、SLC領域22Aと、MLC領域22Bと、を有するメモリ部22と、MLC領域22Bに記憶されたデータの誤りを訂正する誤り訂正部20と、誤り訂正部20が誤りを検出したデータを記憶していた多値メモセルの位置情報をSLC領域22Aに記憶し前記位置情報にもとづき消失訂正を行う消失訂正部21と、を具備する。

(もっと読む)

半導体装置

【課題】消費電力を低減出来る半導体装置を提供すること。

【解決手段】実施形態に係る半導体装置1は、データを保持可能なNAND型フラッシュメモリ22と、データについての誤りを検出・訂正する誤り訂正部38と、データ毎に、使用される誤り訂正方式についての情報を有するテーブル35、36とを具備する。誤り訂正部は、前記テーブル内の前記情報に従って、適用する誤り訂正方式を前記データ毎に選択する。

(もっと読む)

情報処理装置、情報処理方法

【課題】ロックステップ方式の情報処理装置におけるいずれかの系にメモリエラーが発生した場合にも、ロックステップを外すことなく安定して動作する。

【解決手段】プロセッサと、誤り検出・訂正機能を有するメモリとが含まれる複数系のCPUモジュールがクロック同期して同一の処理を行うロックステップ方式の情報処理装置の、CPUモジュールが、自系のメモリから誤りが検出された場合に生成される第1の訂正情報を記憶し、生成された第1の訂正情報を他系のCPUモジュールに送信し、他系のCPUモジュールのメモリが誤りを検出した場合に送信される第2の訂正情報を受信し、他系のCPUモジュールから第2の訂正情報を受信した遅延に応じて、記憶部に記憶されている第1の訂正情報を読み出し、第2の訂正情報と第1の訂正情報とを同期してエラー訂正処理を行う。

(もっと読む)

電子機器、制御方法及びプログラム

【課題】BIOSデータがOS起動中に破壊されてしまっても、そのBIOSデータを復元することが可能な電子機器を提供する。

【解決手段】 本実施形態の電子機器(100)は、電源(15)が投入された際に、データを記憶する第1の記憶手段(12)に格納されているBIOSデータを、第1の記憶手段(12)とは異なる第2の記憶手段(13)にコピーし、OSを終了する際に、第1の記憶手段(12)に格納されているBIOSデータと、第2の記憶手段(13)にコピーしたBIOSデータと、を比較し、双方のBIOSデータが異なる場合は、第2の記憶手段(13)にコピーしたBIOSデータを、第1の記憶手段(12)にコピーする。

(もっと読む)

メモリシステム

【課題】データの信頼性を向上させた多値記憶セルを用いたメモリシステムを提供する。

【解決手段】メモリシステムは、ワード線、並びに、前記ワード線で選択され、異なる複数の物理量レベルによってデータを記憶する複数のメモリセルを有するセルアレイと、外部から入力された第1のデータを保持するレジスタと、前記レジスタに保持された第1のデータを第2のデータに変換してこの第2のデータを前記レジスタの第1のデータを保持する領域に上書きし、更に、前記レジスタに保持された第2のデータを前記メモリセルに記録する第3のデータに変換してこの第3のデータを前記レジスタの第2のデータを保持する領域に上書きするデータ変換部とを備えたことを特徴とする。

(もっと読む)

半導体記憶装置およびメモリ制御装置

【課題】符号化率の低下を防ぐことができる半導体記憶装置を得ること。

【解決手段】2つ以上のセル周辺回路と、前記セル周辺回路ごとに、前記セル周辺回路により読み出し、書き込みのうち少なくとも一方を制御される2つ以上の記憶セルと、を備える半導体メモリ、を備える。さらに、同一の前記セル周辺回路により制御される前記記憶セルに保持されるデータで、誤り訂正符号を生成する単位である1シンボルを形成するよう指示する制御部と、前記制御部の指示に基づいて形成したシンボルに対する誤り訂正符号を生成する符号化部と、を備えるメモリ制御部、を備える。

(もっと読む)

メモリシステム

【課題】データの信頼性が高い多値記憶セルを用いたメモリシステムを提供する。

【解決手段】メモリシステムは、p(pは3以上の素数)以上の物理量レベルを持つセルユニットからなるセルアレイと、バイナリ表現の入力データを、pの剰余体であるZpの要素で表現された書き込みコードに変換するコード生成部と、Zpの各要素をそれぞれ異なる前記物理量レベルに対応させて前記セルユニットに前記書き込みコードを書き込むコード書き込み部とを備え、前記入力データをp−1個の前記セルユニットに記録する場合において、これらp−1個の前記セルユニットのうち、前記入力データが0の場合と、1ビットのみが1の場合で、同一の物理量レベルに書き込まれるセルユニットはないことを特徴とする。

(もっと読む)

データ修復装置

【課題】同一のデータが書き込まれた全ての領域に破壊された部分が存在する場合においても、破壊されたデータを修復すること。

【解決手段】CPU1は、全ての領域R0〜RNの同一オフセットアドレスのワードデータを1ワード分だけフラッシュROM6から読み出し、ワードデータが同じならば次の1ワード分のワードデータを読み出し、ワードデータが1個でも異なるならば、全ての領域R0〜RNのワードデータをマージすることでワードデータを再構築する。

(もっと読む)

プログラマブル論理回路のエラー訂正回路

【課題】コンフィギュレーションメモリのエラーの検出から修正、復旧までをプログラマブル論理回路に影響を与えることなくエラーを隠蔽した状態で動的に行うことが可能なプログラマブル論理回路のエラー訂正回路を提供する。

【解決手段】エラー訂正回路11は、プログラマブル論理回路の回路構成または配線構成を示す構成データおよびこの構成データの誤り検出符号化データが、ベースメモリMから読み出されて格納されるコンフィギュレーションメモリ12と、構成データと誤り検出符号化データとからエラー発生を検出するエラー検知部131、エラーが発生する前の構成データを保持する代替記憶部134、エラー通知により構成データを代替記憶部134が保持した構成データに切り替えるマルチプレクサ部133と、ベースメモリMから構成データを読み出し、コンフィギュレーションメモリ12に書き込み再構成する再構成制御部14とを備えた。

(もっと読む)

メモリコントローラ、メモリコントローラを備えるフラッシュメモリシステム、並びにフラッシュメモリの制御方法

【課題】復号化回路を備えたメモリコントローラにおいて、シンドロームを算出する処理から誤り位置多項式を導出する処理への処理の引継ぎの円滑化と、誤り位置多項式を導出する処理の効率化を図る。

【解決手段】データ保持回路内の領域、シンドローム保持回路内の領域及び係数保持回路内の領域は、相互に対応関係が定められており、データ保持回路内の第1の領域に保持されたデータに基づいて算出されたシンドロームは、当該第1の領域に対応するシンドローム保持回路内の領域である第2の領域に保持され、当該第2の領域に保持されたシンドロームに基づいて算出された係数は、当該第2の領域に対応する係数保持回路内の領域である第3の領域に保持され、当該第3の領域に保持された係数に基づいて、当該第1の領域に保持されたデータのビットエラーが訂正される。

(もっと読む)

61 - 80 / 431

[ Back to top ]