Fターム[5B018GA02]の内容

記憶装置の信頼性向上技術 (13,264) | 目的 (2,614) | エラー訂正 (431)

Fターム[5B018GA02]に分類される特許

141 - 160 / 431

コンピュータ装置及びコンピュータシステムのためのメモリシステム

【課題】寿命が長く、信頼性が高く、安価なメモリシステムを提供する。

【解決手段】メモリシステム300は、複数のコンピュータ装置と接続されるコントローラ310と、該コントローラと接続される複数のマルチレベルセル(MLC)装置320と、コントローラ310及び複数のMLC装置320と接続されるシングルレベルセル(SLC)装置330とを備えている。コントローラ310の制御下で、データは複数のMLC装置に分割して記憶され、SLC装置330はデータのパリティチェックためのパリティ装置として機能する。

(もっと読む)

ソフトエラー検出回路を備える制御装置

【課題】スリープモード中にレジスタ等にソフトエラーが生じても、異常動作を回避する。

【解決手段】マイコン2の動作に重要な意味をもつ情報が格納される保持回路16と、保持回路17とは、多重化された格納回路を提供する。これら保持回路16、17には、同じ情報が書き込まれ、格納される。マイコン2がスリープモード中に、ソフトエラーなど何らかの理由により保持回路16、17に不一致が生じることがある。この場合、EXORゲート18、ANDゲート15、およびORゲート12を介して、ウェイクアップ信号がマイコン2に与えられる。マイコン2は、臨時的に通常モードに復帰し、保持回路16、17を再設定する。この結果、保持回路16、17のソフトエラーによるマイコン2の異常動作を回避することができる。

(もっと読む)

半導体装置及び電子機器

【課題】動作時間を短縮しつつ、半導体記憶装置のデータを修正する半導体装置及び電子機器を提供すること。

【解決手段】選択回路8は、CPU2及び誤り訂正回路5と、第1及び第2メモリMe1,Me2との間に配置される。選択回路8は、アドレスデータDaに基づいて、CPU2に指定された一方の第1又は第2メモリMe1,Me2に対応するメモリ書き込みデータDwmを第1又は第2メモリ書き込みデータDwm1,Dwm2として出力し、CPU2に指定されていない他方の第1又は第2メモリMe1,Me2に対応する訂正メモリデータDmtを第1又は第2メモリ書き込みデータDwm1,Dwm2として出力する。

(もっと読む)

半導体記憶装置

【課題】大容量の不揮発性メモリのアクセス時間とランダム・アクセス・メモリのアクセス時間との整合を図り、大容量不揮発のメモリを含む半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、フラッシュメモリと、クロック同期型DRAMと、前記フラッシュメモリ及び前記クロック同期型DRAMに結合され、前記クロック同期型DRAM及び前記フラッシュメモリに対するアクセスを制御するための制御回路と、前記制御回路に結合された複数の入出力端子とを含む。前記入出力端子を介した前記フラッシュメモリに対するアクセスは、前記クロック同期型DRAMを経由して行う。

(もっと読む)

誤り検出訂正器、メモリコントローラおよび半導体記憶装置

【課題】復号処理効率のよい誤り検出訂正器16を提供する。

【解決手段】誤りページアドレスおよび誤り位置多項式の係数σと、誤り位置を示す誤りビットアドレスとを対応付けて記憶するECCキャッシュ部21と、シンドローム算出部18Aが検出した誤りページアドレスおよび多項式算出部18Bが算出した誤り位置多項式の係数σとECCキャッシュ部21に記憶されている誤りページアドレスおよび誤り位置多項式の係数σとを比較し一致するかどうか判断する比較部22と、比較部22が一致すると判断した場合に、ECCキャッシュ部21に記憶されている誤りビットアドレスの位置を誤り位置として特定する第1の誤り位置特定部23と、を具備する。

(もっと読む)

データ処理装置

【課題】不揮発性半導体メモリを用いるデータ処理装置において、低消費電力と高データ信頼性の両方を実現すること。

【解決手段】データ処理装置は、不揮発性半導体メモリと付加ビット制御回路とを備える。不揮発性半導体メモリには、データ本体あるいはその反転データと付加ビットとを含む記憶データが格納される。付加ビット制御回路は、モード指定信号に応じて、モード間で付加ビットを変える。より詳細には、付加ビット制御回路は、低消費電力モード用の付加ビットを生成するデータ反転制御回路と、高信頼性モード用の付加ビットを生成するエラー検出制御回路と、を含む。低消費電力モードでは、データ反転制御回路が機能し、反転フラグを付加ビットとして生成する。一方、高信頼性モードでは、エラー検出制御回路が機能し、エラー検出コードを付加ビットとして生成する。

(もっと読む)

DRAMバッファ管理装置および方法

【課題】別途のデバイスを追加することなく、DRAMバッファにエラー訂正コードを適用することのできるDRAMバッファ管理装置および方法を提供すること。

【解決手段】DRAMバッファ管理装置およびDRAMバッファ管理方法が開示される。当該DRAMバッファ管理装置およびDRAMバッファ管理方法においては、DRAMバッファに記録されるデータに対するエラー訂正コードを生成し、前記データおよび前記ECCを前記DRAMバッファに記録する。  (もっと読む)

(もっと読む)

メモリ装置

【目的】読出データに対する誤り検出及び誤り訂正機能を備えたメモリ装置において、その装置規模を小規模化させることが可能なメモリ装置を提供することを目的とする。

【構成】メモリアレイから読み出されたデータに対して誤り検出を行う誤り検出回路及びこの誤り検出結果に基づき上記読み出されたデータ中の誤りビットを訂正する誤り訂正回路の内の誤り検出回路を、上記メモリアレイが構築されているメモリチップに搭載し、誤り訂正回路は、このメモリチップに対するデータの読み出し制御を担うメモリ制御チップ側に搭載する。

(もっと読む)

ディスクドライブ装置及び不揮発性メモリ制御方法

【課題】エラーが発生した不揮発性メモリを即座に使用中止せずに、不揮発性メモリの信頼性(エラー履歴)に合わせてデータの読み書きを制御することで、使用可能なメモリ容量の減少を最小限にすることができるディスクドライブ装置を提供する。

【解決手段】ディスクドライブ装置10は、不揮発性メモリディスク12を構成する所定のメモリ単位毎にエラー発生回数を記憶するメモリ111aと、エラー発生回数毎に予め設定された複数個のメモリ単位に対して同じデータを重複して書き込むデータ制御部114と、同じデータが重複して書き込まれた複数個のメモリ単位から複数個のデータを読み込み、複数個の読み込みデータに対して多数決判定を行い、最も数が多い読み込みデータを最尤値として決定する読み込みデータ処理部112とを備える。

(もっと読む)

データ記憶システムの設定方法

【課題】外部インターフェースから見た不良ビット発生率を、さらに減少させることができるデータ記憶システムの設定方法を提供すること。

【解決手段】複数個のメモリセルブロックを有し、これらメモリセルブロックのいくつかに接続されるページを含む非スペア領域(1n)と、予めデータがある値に揃った複数個のスペアメモリセルブロックを有し、これらスペアメモリセルブロックのいくつかに接続されるページを含むスペア領域(1s)と、非スペア領域(1n)内のページからデータを読み出したときに、少なくとも2ビットのデータ誤りを検出し、読み出したページにおける誤りビットの数を読み出したページ毎に判定する判定回路(5、6、100)とを具備する。判定回路(100)による判定結果が2ビット以上の場合に、読み出したページの内容を誤り訂正し、スペア領域(1s)内のページに書き込む。

(もっと読む)

不揮発性半導体記憶装置

【課題】本発明は、小型化、低価格化が可能で、起動時間、アクセス時間が短い大容量の半導体記憶装置を提供することを目的とする。

【解決手段】不揮発性半導体メモリに格納されるデータの誤り検出・訂正を行う誤り訂正回路と、複数のバッファを備え、誤り訂正回路による誤り検出・訂正後のデータの複数のバッファのうち、一つからホストへのインターフェイス制御回路を通じた転送と、誤り訂正回路による誤り検出・訂正のための他のデータの前記不揮発性半導体メモリから前記複数のバッファのうちの他の一つへの転送とを平行に行う。

(もっと読む)

伝送装置及びリンク切れ修復方法

【課題】 複数のセグメント間を連結するポインタに生じたビットエラーを正しい値に復元し、チェーンメモリーのリンク切れを修復することができる伝送装置及びリンク切れ修復方法を提供する。

【解決手段】 伝送装置100は、エラーポインタのビットパターン及び反転パターンの排他的論理和を演算し、真のポインタを含むポインタ候補を算出するポインタ予測部50を備えている。また、ポインタ候補が示すポインタ格納領域11aに格納された前ポインタとエラーポインタが格納されたポインタ格納領域11aのアドレスとの一致の有無を判定するポインタ検証部70を備えている。また、ポインタ検証部70による判定結果に基づき、エラーポインタを、一致した前ポインタが格納されるポインタ格納領域11aのアドレスであるポインタ候補に変換するポインタ復元部80を備えているものである。

(もっと読む)

外部記憶装置およびそのメモリアクセス制御方法

【課題】セクタデータを連続してアクセスする外部記憶装置において、単一のエラー訂正手段によりエラー検出・訂正を行いながらメモリアクセスを高速化する。

【解決手段】ホスト2がライトするセクタデータは一時ライトバッファ7に格納される。マイクロプロセッサ8は、ライトバッファに格納されたセクタデータが奇数番目のセクタデータの場合には第1のメモリ4に、偶数番目のセクタデータの場合には第2のメモリ5に格納する。ホスト2がセクタデータをリードするときには、データ切換手段11において、第1のメモリから読み出したN番目のセクタデータをシステムバスに対し出力すると同時に、第2のメモリから読み出したN+1番目のセクタデータ(ホストコンピュータが次にリードするセクタデータ)をエラー訂正手段に対し出力する。これにより、N+1番目のセクタデータに対するエラー検出およびエラー訂正に要する時間を見かけ上短縮する。

(もっと読む)

不揮発性メモリにおけるデータ・エラー回復

エラー訂正コード(ECC)ユニットが、ソリッド・ステートの不揮発性メモリ装置における、補正可能でないエラーを見つけると、エラーを位置特定し、補正する試行における処理を使用し得る。前述の処理はまず、エラーが含まれている可能性が高い「低確信度」メモリ・セルを識別し、次いで、種々の基準に基づいて、前述のセルにおいて正しい可能性がより高いデータがどれであるかを求め得る。次いで、新たなデータをECCユニットによって検査して、何れかの残りのエラーをECCユニットが補正するために十分正しい旨を検証し得る。  (もっと読む)

(もっと読む)

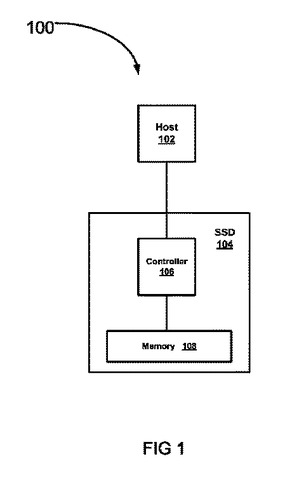

ソリッドステートディスクにおける改良された誤り訂正

いくつかの実施例では、ソリッドステートディスクは、不揮発性メモリとコントローラとを有する。コントローラは、不揮発性メモリに格納されているデータに対してECCを実行し、ECCがデータを訂正できない場合、データに対してパリティ処理を実行する。他の実施例が開示及び請求される。  (もっと読む)

(もっと読む)

メモリコントローラおよびメモリ管理方法

【課題】メモリに記録されるデータの種類に応じて要求される信頼度を考慮し、様々な誤り訂正符合(ECC)方式を用いることによって、効率的なメモリ管理が可能なメモリコントローラおよびメモリ管理方法を提供すること。

【解決手段】データの種類に応じて選定された要求信頼水準に基づいて前記データに対する誤り訂正符合情報を生成し、前記ECC情報に基づいて前記データに対するECCコードを演算した後、前記ECCコードをメモリに記録するメモリコントローラが開示される。  (もっと読む)

(もっと読む)

不揮発性記憶デバイスを有する記憶装置

【課題】データ読み出しに破壊読み出しを伴う不揮発性記憶デバイスに記憶されているデータに、不意な電源遮断に起因するようなエラー部分が残されていても、特別のハードウェア構成を必要とすることなく、そのエラー部分を高速で復旧できるようにする。

【解決手段】FeRAM11の記憶領域には、ユーザーデータ領域111及びブロックアドレス領域112が確保される。ブロックアドレス領域112は、ユーザーデータ領域111からのデータ読み出しに際し、読み出されるべきデータが格納されているアドレスを示すアドレスデータを格納するのに用いられる。MPU16は、ブロックアドレス領域112に格納されているアドレスデータの示す、ユーザーデータ領域111の記憶位置に格納されているデータのエラーを検出し、エラーが検出された場合、当該エラーが検出されたデータを訂正して、当該訂正されたデータをユーザーデータ領域111に書き戻す。

(もっと読む)

管理型不揮発性メモリのアドレスマッピングのためのアーキテクチャー

ここに開示するアーキテクチャーは、アドレスマッピングを使用して、ホストインターフェイスにおけるブロックアドレスを不揮発性メモリ(NVM)装置の内部ブロックアドレスへマップする。ブロックアドレスは、そのブロックアドレスで識別される同時アドレス可能なユニット(CAU)を選択するための内部チップセレクトへとマップされる。ここに開示するアーキテクチャーは、読み取り、書き込み、消去及び状態取得オペレーションのための一般的なNVMコマンドをサポートする。又、このアーキテクチャーは、複数のCAUアーキテクチャーをレバレッジする読み取り及び書き込みオペレーションをサポートするための拡張コマンドセットもサポートする。 (もっと読む)

カウントデータ記録装置ならびにカウントデータ記録方法およびプログラム

【課題】メモリの利用効率がよく、破損したカウントデータを修復可能なカウントデータ記録装置を提供する。

【解決手段】N個(Nは、4以上の整数)の記憶領域と、カウントデータを記憶領域に書き込むデータ書込部と、カウントデータを読み出すデータ読出部と、カウントデータの破損を検出して該破損を修復するデータ修復部とを有し、データ書込部は、M個(Mは、3以上N未満の整数)の記憶領域を小ループ範囲に定め、該小ループの範囲の記憶領域を順に使用してカウントデータを記録し、該小ループ範囲の最後尾の記憶領域を使用してカウントデータを記録すると、該小ループ範囲を、所定の順に沿って後方へずらして小ループ範囲を変更する、ようにして、カウントデータを記憶部に記録し、データ修復部は、カウントデータをソートした被ソートカウントデータ列と該データ列の差分値列とに基づいて破損を修復するカウントデータ記録装置。

(もっと読む)

キャッシュメモリ制御回路、キャッシュメモリ装置、及びキャッシュメモリ制御方法

【課題】キャッシュメモリへの書込不良を正確に検出すると共に、データリカバリに伴うペナルティ期間を短縮することが可能なキャッシュメモリ制御回路を提供する。

【解決手段】キャシュメモリ制御回路33を、連続して入力され得るデータの最大個数(="4")分のキャッシュメモリ32_1〜32_4各々に対応して設けられ、各々が対応するキャッシュメモリに一のデータを書き込むと共に、前記対応するキャッシュメモリから読み出したデータが前記一のデータと一致するか否かを判定し、両データが一致しないと判定した場合に前記一のデータを前記対応するキャッシュメモリに再び書き込む4個のリカバリ部331_1〜331_4と、リカバリ部331_1〜331_4を順次制御し、連続して入力されたデータD0〜D3各々を互いに異なるキャッシュメモリに書き込ませる書込制御部332と、で構成する。

(もっと読む)

141 - 160 / 431

[ Back to top ]