Fターム[5B018GA02]の内容

記憶装置の信頼性向上技術 (13,264) | 目的 (2,614) | エラー訂正 (431)

Fターム[5B018GA02]に分類される特許

21 - 40 / 431

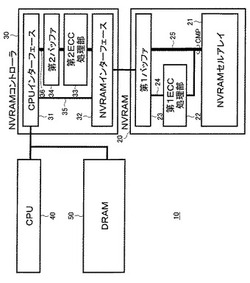

不揮発性メモリ、メモリコントローラ、不揮発性メモリのアクセス方法、およびプログラム

【課題】メモリセルとしてバイト単位のアクセスが可能であり、求められるアクセスに対して最適な単位でECC処理を行うことが可能な不揮発性メモリ、メモリコントローラ、不揮発性メモリのアクセス方法、およびプログラムを提供する。

【解決手段】ワード単位でアクセス可能で固定レイテンシでアクセス可能な第1アクセスモードと可変レイテンシでアクセス可能な第2アクセスモードによりアクセス可能な不揮発性メモリセルアレイを少なくとも含む不揮発性メモリセルデバイスと、第1アクセス経路に配置され、第1アクセスモード時にメモリセルアレイから出力されたデータに対してECCを適用した誤り検出処理および訂正処理を行う第1ECC処理部と、第2アクセス経路に配置され、第2アクセスモード時にメモリセルアレイから出力されたデータに対してECCを適用した誤り検出処理および訂正処理を行う第2ECC処理部とを有する。

(もっと読む)

マルチチャネルを有するメモリ装置及び同装置における誤り訂正チャネル決定を含む書き込み制御方法

【課題】誤り訂正チャネルを適用していながら、データ読み出しの並列度を向上できるようにする。

【解決手段】実施形態によれば、誤り訂正チャネル決定手段は、論理ブロックを構成する複数の論理ページがページ単位に複数のチャネルを介してメモリに書き込まれる際に、複数のチャネルのそれぞれに誤り訂正チャネルが割り当てられる論理ページの数が均等になるように、ページ単位に誤り訂正チャネルが割り当てられるチャネルを決定する。コマンドリスト生成手段は、誤り訂正チャネルが割り当てられるチャネルの決定に基づいて、複数のチャネルのうちの誤り訂正チャネルを除くチャネル群を介して、対応する論理ページを並列に書き込むためのライトコマンド群のリストを生成する。コマンドリスト投入手段は、ライトコマンド群のリストをメモリインタフェースに投入する。

(もっと読む)

メモリコントローラ、半導体メモリ装置、および復号方法

【課題】、実装メモリ容量が小さく回路規模の小さいメモリコントローラ3を提供する

【解決手段】メモリコントローラ3は、LDPC符号により符号化されたフレーム単位のデータを、単位行列からなるブロックと、単位行列の各行が順にシフトしている複数のブロックと、からなる検査行列をもとに、部分並列処理により復号を行い、メモリ部5から読み出したデータの閾値判定情報を記憶するバッファ24と、閾値判定情報をLLRに変換するLLR変換部16と、ブロックのサイズ以下のイタレーション単位で、LLRをもとに、列処理および行処理を繰り返し行うイタレーション処理のときに算出される確率情報βを、記憶するLMEM12と、イタレーション単位のイタレーション処理が完了する度に、LMEM12に記憶される確率情報βを、バッファ24に転送するCPUコア10と、を具備する。

(もっと読む)

半導体装置

【課題】データの信頼性の向上を低コストで実現可能な半導体装置を提供する。

【解決手段】例えば、相補メモリを備えた半導体装置において、書き込み時に、(N+1)ビットの正極(Posi)データに対してパリティービットを生成し、(N+1)ビットの負極(Nega)データに対してパリティービットを生成する。読み出し時には、正極側および負極側のそれぞれに対してパリティーチェックを行うと共に、正極データと負極データを各ビット番号毎に比較する。ここで、正極データと負極データが同一データとなっているビット番号が存在した場合、正極側のパリティーチェック結果が異常であれば正極データの当該ビット番号を誤データとして特定でき、逆に負極側のパリティーチェック結果が異常であれば負極データの当該ビット番号を誤データとして特定できる。

(もっと読む)

メモリコントローラ及びメモリコントローラの動作方法

【課題】メモリ装置を制御するメモリシステムのコントローラが提供される。

【解決手段】本発明のコントローラはコントローラによって受信された読出しベクトルのエラー位置多項式を演算するキー公式解き方部、演算されたエラー位置多項式及び前記エラー位置多項式の情報の中で少なくとも1つにしたがって受信された読出しベクトルのエラー数を測定する制御部、及び演算されたエラー位置多項式にしたがって受信された読出しベクトルのエラー位置を検索するチェン検索部に構成される。

(もっと読む)

半導体装置、情報処理装置およびエラー検出方法

【課題】小規模な回路でデータ伝送動作の信頼性を高める。

【解決手段】(n−1)個(ただし、nは4以上の整数)の2ビット検査部210_0〜210_(n−2)のそれぞれは、1ビットの入力データを冗長化して得られたnビットの符号化データIの入力を受け、符号化データIにおけるそれぞれ異なるビット同士の比較結果に基づく2ビット検査データを出力する。全ビット検査部220は、符号化データIの全ビットの排他的論理和に基づく全ビット検査データを出力する。エラー検出部230は、(n−1)個の2ビット検査データと全ビット検査データとに基づいて符号化データIに対するエラー検出を行い、エラー検出結果に基づいて入力データを出力する。

(もっと読む)

記憶装置、コンピュータ装置、コンピュータの制御方法、およびコンピュータプログラム

【課題】データの保持期間を長くする。

【解決手段】コンピュータシステムは、パーソナルコンピュータなどのホスト10と、ホスト10に接続されるUSBメモリデバイス100とを備える。USBメモリデバイス100は、ユーザ用データを格納するためのNAND型フラッシュメモリ130と、OTPメモリ140とを備える。NAND型フラッシュメモリ130には、ユーザ用データ以外に、ユーザ用データに対応した第1次のエラー訂正用符号であるECC_Aとが格納される。一方、OTPメモリ140には、ECC_Aに対応した第2次のエラー訂正用符号であるECC_Bが格納される。

(もっと読む)

データ記憶装置及びデータ処理装置及びコンピュータプログラム及びデータ記憶方法

【課題】実装面積を増大させることなく、ソフトエラーの発生を検出し、訂正できるようにする。

【解決手段】演算装置101(演算部)は、所定の演算により、複数の入力データ501に基づいて、誤り検出データ503を算出する。記憶装置102は、複数の入力データ501と、誤り検出データ503を記憶する。データ生成装置104(判定部・訂正部)は、記憶装置102が記憶した複数の入力データと記憶装置102が記憶した誤り検出データとの間に整合性があるか判定し、整合性がない場合、記憶装置102が記憶した複数の入力データと記憶装置102が記憶した誤り検出データとのうちから、誤っているデータを判定し、誤っていると判定したデータについて、正しいデータを算出する。

(もっと読む)

メモリ装置、メモリ制御装置、メモリ制御方法

【課題】ガベージコレクションの発生等に伴う他フラッシュメモリへのデータコピーを、コピーコマンドを使用する場合と同等に高速化する。

【解決手段】共通のデータ線が接続された複数のフラッシュメモリ部についてデータの読出/書込制御を行うように構成されたメモリ装置において、上記複数のフラッシュメモリ部のうち第1のフラッシュメモリ部に読出指示を行って当該第1のフラッシュメモリ部から上記共通のデータ線に読出データを出力させると共に、上記第1のフラッシュメモリ部から上記読出データが出力されるタイミングに応じたタイミングで、上記第1のフラッシュメモリ部とは異なる第2のフラッシュメモリ部に書込指示を行うことで、上記共通のデータ線に得られた上記読出データが上記第2のフラッシュメモリ部に書き込まれるようにする。

(もっと読む)

不良ビットエラーを処理するシステムおよび方法

【課題】半導体不揮発性メモリ装置における不良ビットエラーを補償する。

【解決手段】装置は、メモリ装置120から古いページを受け取り、そのページが不良ビットを有するか否かを決定する不良ビット検出モジュール116を含む。装置は、新しいページを生成する不良ビット修正モジュール118を含む。不良ビット修正モジュール118は、不良ビットの位置を特定し、不良ビットの好適値を決定し、不良ビットのユーザ値を決定する。不良ビット修正モジュール118は、古いページの実質的なデータに対応するビット列に好適値を挿入し、好適値が挿入されたビット列を記録する。不良ビット修正モジュール118は、古いページのアドレスに新しいページを格納する。

(もっと読む)

半導体記憶装置

【課題】

実施形態は、外部装置を変更せずに、データを復元可能な半導体記憶装置を提供する。

【解決手段】

本実施形態の半導体記憶装置によれば、メモリセルアレイと、外部とデータの入出力を行う入出力部と、前記メモリセルアレイに通常データを書き込むとき、前記入出力部から入力された外部冗長データ(パリティA)と、前記入出力部から入力された前記通常データ(通常データA)とに基づいて生成された内部冗長データ(パリティAA)を出力するECC回路とを備えることを特徴とする。

(もっと読む)

メモリ制御装置およびメモリ制御方法

【課題】メモリにおいて、時間経過とともに訂正不可能なビット誤りが生じることを防ぐこと。

【解決手段】メモリ制御装置は、第1の所定の期間が経過する毎に、読み出すブロックを更新しつつ、メモリから1ブロック分のデータを読み出すデータ読み出し部と、前記データに訂正不可能なエラーが含まれない場合に、前記データに含まれるエラーを訂正するエラー訂正部と、前記データに含まれるビット化け数が所定のビット数以上である場合に、前記エラー訂正部により訂正されたデータをメモリに書き込むデータ書き込み部と、を備えている。

(もっと読む)

メモリシステム

【課題】読み出し動作開始から読み出し動作完了までの処理時間を可及的に低減する。

【解決手段】制御部は、不揮発性メモリに格納されているデータを読み出す際、読み出し電圧管理情報に記録されている読み出し電圧の値を用いて不揮発性メモリからデータを読み出して、誤り検出部が読み出されたデータに誤りを検出したとき、誤り検出部が読み出されたデータに誤りを検出しなくなるまで読み出し電圧を変更して前記不揮発性メモリからデータの再読み出しを行い、誤り検出部が読み出されたデータに誤りを検出しなくなったとき、読み出し電圧管理情報に記録されている読み出し電圧を更新する。

(もっと読む)

半導体記憶装置及びその制御方法

【課題】半導体記憶装置に対する書き込み/読み出しに影響を与えることなく、読み出し時にエラー訂正されたデータを、メモリ本体に再書き込みする。

【解決手段】実施形態に係る半導体記憶装置1は、エラー訂正部9、第1の記憶部10、第2の記憶部11、制御部13を含む。エラー訂正部9は、メモリ本体8から読み出されたデータに対するエラー訂正を行う。第1の記憶部10は、エラー訂正部9によって訂正されたデータを記憶する。第2の記憶部は、エラー訂正部9によって訂正されたデータに対応するアドレスを記憶する。制御部13は、メモリ本体8に対する読み出し/書き込みが実行されていないタイミングにおいて、第1の記憶部10に記憶されているデータと第2の記憶部11に記憶されているアドレスに基づいて、メモリ本体8に対して再書き込みを行う。

(もっと読む)

誤り訂正回路およびメモリ装置、並びに誤り訂正方法

【課題】高速な誤り訂正を可能とし、誤り訂正回路の規模や消費電力の増大を抑えることができる誤り訂正回路およびメモリ装置、並びに誤り訂正方法を提供する。

【解決手段】冗長化された奇数個の二値情報を電流値で入力する入力手段153と、前記入力手段から入力する前記奇数個の電流値の和を電圧に変換する変換手段151と、前記変換手段が出力する前記電圧が予め設定された第1閾値以上であるか否かに応じて二値情報を出力する第1判定手段152とを備える。

(もっと読む)

メモリコントローラ及び情報処理装置

【課題】読み出しデータの3bitエラーを考慮した上で、訂正可能エラーを判別することを可能にするメモリコントローラ及び情報処理装置を提供する。

【解決手段】ECC機能付きメモリモジュールに接続され、メモリモジュールへのアクセスを制御するメモリコントローラにおいて、メモリモジュールから読み出された複数の読み出しデータについて、読み出しデータに対応するECCの符号情報を、メモリモジュールより読み出して、エラービットの有無及びエラービットの位置の検出を行うエラー検出部と、複数の読み出しデータを一時的に格納するバッファと、バッファに格納された複数の読み出しデータに、エラー検出部によって訂正可能エラーが検出されたデータが複数含まれ、かつ、検出されたデータのエラー検出位置が同じ場合に、複数の読み出しデータ全体として訂正可能なエラーを含むと判定する判定部と、を備える。

(もっと読む)

キャッシュコントローラ、キャッシュ制御方法及びデータ記憶装置

【課題】ハードエラーの発生に対する効率的な対処を実現し、キャッシュ動作の性能の劣化を抑制できるキャッシュコントローラを提供することにある。

【解決手段】実施形態によれば、キャッシュコントローラは、エラー検出訂正モジュールと、コントローラとを具備する。エラー検出訂正モジュールは、キャッシュメモリから読み出されたデータからエラーを検出し、当該エラーを訂正する。コントローラは、前記エラー検出訂正手段によるエラー訂正が不可能で前記エラーの種別がハードエラーの場合に、前記キャッシュメモリに対する電源遮断及び電源再投入の電源制御を実行する。

(もっと読む)

記憶装置、記憶媒体再生方法および記憶媒体再生プログラム

【課題】メモリ素子の情報を正常に読み出すことができる記憶媒体再生装置を提供すること。

【解決手段】電荷量の大小に関連付けて情報を記憶する記憶部110と、第1の閾値と、記憶部110に記憶された電荷量とを比較して、比較結果に基づいて記憶部110から電荷量に関連付けられた情報を読み出す比較部104a〜104cと、読出した情報に誤りが存在するか否かを判断する誤り検出部106と、情報に誤りが存在すると判断した場合に、比較部104a〜104cが情報を読み出す際に用いた第1の閾値と異なる値の第2の閾値を生成する閾値生成部107とを備え、比較部104a〜104cは、情報に誤りが存在すると判断した場合に、閾値生成部107が生成した第2の閾値を第1の閾値として記憶部110から情報読み出すことを特徴とする。

(もっと読む)

メモリ書込み制御装置

【課題】メモリへのデータ書込み処理に要する時間の短縮により、システム全体の速度性能の改善をはかる。

【解決手段】エラー検知部31が、CPU1から出力されるライト置情報に基づき、リードデータの特定された個所のエラー訂正の要否を示す制御情報を生成すると同時に、ライトデータ生成部32が、ライト位置情報に基づきメモリ2から読み出されるリードデータにライト要求データをマージしてライトデータを生成する。そして、エラー訂正部33が、その制御情報に基づき、ライトデータ生成部32から出力されるライトデータに対してエラー訂正を行ない、検査ビット生成部34がエラー訂正部33から出力される前記ライトデータからエラー訂正用検査ビットを生成してメモリ2に書き込む。

(もっと読む)

メモリシステム及びメモリコントローラ

【課題】処理内容の判別が可能なメモリシステムを提供する。

【解決手段】実施形態に係るメモリシステムは、外部からの入力データにパリティ情報を付加させた記憶データを記憶する複数のメモリセルを有するメモリデバイスと、前記入力データ及び前記記憶データ間の変換を行うメモリコントローラとを備え、前記記憶データに含まれる前記入力データに対応する情報データは、前記入力データに対して非線形の関係にあることを特徴とする。

(もっと読む)

21 - 40 / 431

[ Back to top ]