Fターム[5B018JA04]の内容

記憶装置の信頼性向上技術 (13,264) | 試験 (271) | 並列試験 (65) | 基準データとの比較 (30)

Fターム[5B018JA04]に分類される特許

1 - 20 / 30

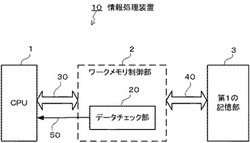

情報処理装置及び記憶部検査方法

【課題】CPUの運用中においても、記憶部の検査のためにCPUによるソフトウェアのデータ処理を一時停止させることがなく、記憶部の異常の有無をチェックすることができる情報処理装置及び記憶部検査方法を提供する。

【解決手段】CPU1とは独立に設置された記憶制御部2は、CPU1から書き込みようの処理データと書き込み先の記憶部3の指定アドレスを受け、検査用データを指定アドレスに書き込み、それを読み出す。記憶制御部2が備えるデータチェック部20は、検査用データと読み出されたデータとを比較し、一致するかどうかを判定する。一致しなければ指定アドレスに異常があると判定し、その旨をCPU1に通知し、一致すれば、記憶制御部は処理データを指定アドレスに書き込む。

(もっと読む)

メモリシステム

【課題】

実施形態は、信頼性を向上可能なメモリシステムを提供する。

【解決手段】

本実施形態のメモリシステムによれば、複数のワード線と、複数のビット線と、制御ゲートに前記ワード線が接続され、ドレイン端に前記ビット線が接続されたメモリセルと、複数の前記メモリセルを含むページ、複数の前記ページを含むブロックを有するメモリセルアレイと、前記ページごとに不良の前記ビットの個数が第1閾値以下である良ブロックに関するデータが保持された記憶領域とを備え、前記第1閾値は、不良ブロックか否かの判定に用いる第2閾値よりも小さいことを特徴とする。

(もっと読む)

電子装置、及び、これを用いた電動パワーステアリング装置

【課題】アドレスバスおよびデータバスの故障を検出する電子装置において、故障検出に係る処理負荷を低減し処理速度を向上する。

【解決手段】電子装置は、CPUとROMとを接続しアドレスを伝送する4つ以上のバスラインからなるアドレスバス21を備える。電子装置は、アドレスバス検査用アドレスAdによって指定されるROM領域13aから値を読み出し、読み出した値から計算した判定値Vjと予め計算されたアドレスバス検査用正解値Vtとを比較し、一致しない場合、アドレスバス21が故障していると判定する。アドレスバス検査用アドレスAdは、4つ以上のバスラインに対応する4ビット以上の値であって、2ビット以上の0の値と2ビット以上の1の値とを有する値を含み、複数のバスライン間の短絡故障を同時に検出可能である。これにより、故障検出に必要な検査用アドレスAdの数を低減することができる。

(もっと読む)

データ書き込み方法およびシステム

【課題】 エラー訂正符号格納領域を有するフラッシュメモリにおいて、ブロック消去の回数を削減し、製品寿命を延ばす。

【解決手段】 データ格納領域とエラー訂正符号格納領域とを含むフラッシュメモリにデータを書き込むデータ書き込み方法において、初期値をデータ格納領域に書き込み、書き込みフラグに基づいて書き込みが正常に行われたか否かを判定し、書き込みが正常に行われたときはデータ格納領域にデータを書き込み、書き込みが正常に行われていないときはデータ格納領域を含むブロックを消去する。データの書き込みを行う前に初期値をデータ格納領域に書き込むことで、エラー訂正符号格納領域が初期値か否かを確認できる。ブロックの消去動作を、エラー訂正符号格納領域が初期値でないときのみ実施することで、ブロックの消去の回数を削減でき、製品寿命を延ばすことができる。

(もっと読む)

不揮発性メモリのデータ破壊検出装置

【課題】不揮発性メモリに記憶されたデータがビット破壊しているか否かを検出する不揮発性メモリのデータ破壊検出装置を提供する。

【解決手段】不揮発性メモリ5は、アプリケーションの動作に使用するプログラムが書き込まれた使用アドレスとプログラムが書き込まれていない未使用アドレスとからなる。不揮発性メモリ5のデータ破壊検出装置6は、未使用アドレスに0/1の混合値と混合値の0/1が反転されたミラー値とを交互に書き込む書き込み部11と、混合値とミラー値とを読み出してデータが破壊されているか否かを判定するデータ破壊判定部12とを備えた。

(もっと読む)

メモリ診断方法及びメモリ回路

【課題】メモリ回路において、運用中に自動でメモリ全体の故障検出を行うことを目的とする。

【解決手段】ネットワークから受信したフレームのフレーム間ギャップを含む空きタイムスロットで、メモリのテストを行うためのテストアドレスを順次変化させて生成するテストアドレス生成手段と、メモリのテストアドレスから読み出したデータを退避する退避手段と、メモリのテストアドレスにテストデータを書き込むテスト書き込み手段と、メモリのテストアドレスからテストデータを読み出すテスト読み出し手段と、テスト読み出し手段で読み出されたテストデータを予め保持している基準データと比較して障害の有無を判定する判定手段と、退避手段に退避されているデータを前記メモリの前記テストアドレスに書き戻す書き戻し手段とを有する。

(もっと読む)

半導体試験装置

【課題】DUTから出力される複数の被測定信号をデジタル信号に変換してメモリに取り込むように構成された複数のデジタイザを有する半導体試験装置において、デジタイザ間の信号配線遅延の影響を受けずに常に同一のタイミングでデータを取り込めるようにするとともに、トリガ信号配線数の削減と、データ保存用メモリの有効利用も実現すること。

【解決手段】DUTから出力される複数の被測定信号をデジタル信号に変換してトリガ信号に基づきメモリに取り込むように構成された複数のデジタイザを有する半導体試験装置において、前記各デジタイザを駆動するクロックに対して適切なタイミング関係に位相調整されたトリガ信号を入力する共通のトリガ制御回路を設けたことを特徴とするもの。

(もっと読む)

有限の耐久性および/または持続性を有するメモリ装置からのモニタ・データの情報を分析する方法およびシステム

【課題】

有限の耐久性または持続性を有するメモリ装置からのモニタ・データの情報を分析する方法、システム、およびコンピュータ・プログラムを提供する。

【解決手段】

本発明による方法は、有限の耐久性および/または持続性を有する複数のメモリ装置からモニタ・データの情報を収集するステップであって、モニタ・データは既知に書込みサイクルの数を専用のメモリ・セルに格納された既知の内容のデータである、ステップと、そのモニタ・データの情報を分析するステップと、その分析するステップに基づいてメモリ装置の少なくとも1つに関してアクションを取るステップとを含む。更なるシステム、方法、およびコンピュータ・プログラムも開示される。

(もっと読む)

半導体装置およびその試験方法

【課題】SIP型の半導体装置において、ロジックチップとメモリチップとの間の接続故障を特定して検出することができる半導体装置およびその試験方法を提供する。

【解決手段】複数のメモリ側パッドを有するメモリチップと、複数のメモリ側パッドのそれぞれに接続された、複数のコントローラ側パッドを有するメモリコントローラチップとからなる半導体装置において、コントローラチップに、コントローラ側パッドのそれぞれが入力に接続され、コントローラ側パッドから出力される信号のレベルに応じた試験信号を生成する複数の試験信号生成回路を設け、試験モードにおいて、信号を対応するコントローラ側パッドに出力した状態で、複数の試験信号生成回路のそれぞれが生成する試験信号を期待値と比較する。

(もっと読む)

アドレスバスのテスト方法及びテスト装置

【課題】アドレスバスとデータバス夫々のバス幅の相対的な関係に依存せずにアドレスバスのテストをすること。

【解決手段】複数のメモリセルを有するメモリ装置20へ伝送される複数ビットのアドレスパタンの伝送路であるアドレスバス15aのテスト方法は、次のステップを含む。全ビットが第1論理値であるアドレスパタンにより特定されるメモリセルに対して第1論理値を書き込み、あるビットがその他の全てのビットとは異なり第2論理値である複数のアドレスパタン夫々により特定されるメモリセルに対して第1論理値を書き込み(S1)、第1のアドレスパタンにより特定されるメモリセルに対して第1論理値とは異なる値の第2論理値を書き込み(S5)、第2のアドレスパタンにより特定され、かつ第1論理値が読み出されるべきメモリセルからの第2論理値の読み出しに基づいてアドレスバスの不良を検出する(S4)。

(もっと読む)

論理制御装置およびプログラム書き込み方法

【課題】PLDを複数搭載したボードの不具合に対する原因究明の時間短縮のため、プログラムの誤書き込みを検出すること。

【解決手段】コンフィグレーション制御部20は、各デバイス30に本来のプログラムを書き込む前に、ナンバリング用のプログラムを書き込み、通知データの受信順にデバイス30に対して番号を付与する。番号付与後、各デバイス30に本来のプログラムを書き込む。本来のプログラムには、予め固有の番号(以下、機能番号)が格納されており、デバイス30にプログラムを書き込むことで当該機能番号を取得する。そして、コンフィグレーション制御部20は、各デバイス30から通知された機能番号と、先にデバイス30に対して付与した付与番号とを比較し、その整合性を判断する。両者の整合性がとれていなければ、プログラム保持部40へプログラムを書き込む際に、順序を誤って書き込んだものと判断することができる。

(もっと読む)

メモリデータのハイブリッド検出のための装置および方法

本発明は、メモリセルに格納されたデータを検出する装置および方法に関し、より詳しくは、硬判定検出と軟判定検出を行うハイブリッド検出装置および方法に関する。本発明は、メモリセルに格納された複数ビットのデータの中で特定ビットのデータと関連する基準電圧とメモリセルの閾値電圧とを比較する電圧比較部と、比較結果に基づいて特定ビットのデータの値を検出する検出部と、検出されたデータに対する誤りの発生有無に基づいて特定ビットのデータの検出成功の有無を判断する判断部を含み、検出部は、判断結果に応じて特定ビットより上位ビットのデータに対する検出情報に基づいて特定ビットのデータの値を再検出することを特徴とするデータ検出装置を提供する。本発明によれば、検出対象ビットの下位ビットと関連する硬判定基準電圧または下位ビットに対する検出情報に基づいて検出対象ビットに対する軟判定を行うことができる。  (もっと読む)

(もっと読む)

電子制御装置

【課題】より広範な特殊機能レジスタに対し固着の発生を検出することのできる電子制御装置を提供する。

【解決手段】マイコン10を構成するCPUコア11は、RAM14に割り当てられた特殊機能レジスタ領域SFR1〜SFRmに格納された各格納値V1〜Vmが当初の各設定値E1〜Emにそれぞれ一致しない場合に再書込み処理をそれぞれ繰り返し実行し、再書き込み処理の各繰り返し実行回数C1〜Cmが各既定回数F1〜Fmにそれぞれ達することをもって特殊機能レジスタ領域SFR1〜SFRmに固着が生じた旨を判断する。

(もっと読む)

メモリの検査方法

【課題】従来のメモリ検査方法では、異常が生じているアドレス信号線の位置を知ることができても、それが短絡しているのか開放しているのかは判別できないという問題があった。

【解決手段】メモリのアドレスを指定する複数のアドレス信号線を有するメモリの検査方法であって、前記基準アドレスと、検査アドレスと、検査隣接アドレスとを特定するビットを前記第1検査アドレス信号線のビットと、前記第2検査アドレス信号線のビットとの組合せが異なり、前記第1検査アドレス信号線のビット及び前記第2検査アドレス信号線のビットを除く他のビットは共通となるように決定するステップと、前記基準アドレスと、検査アドレスと、検査隣接アドレスにそれぞれ異なるデータを書き込むステップと、前記基準アドレスと、検査アドレスと、検査隣接アドレスからデータを読み取り、書き込んだデータと同一か否かを判断するステップとを有する。

(もっと読む)

データ残存期間管理装置及び方法

【課題】データ残存期間が有限の記憶装置について、データ残存期間をユーザが把握容易とするためのデータ残存期間管理装置及び方法を提供する。

【解決手段】本発明の一例であるデータ残存期間管理装置は、記憶装置8aに記憶されている監視対象データ10に対応するサンプリングデータを記憶装置8aから読み出し、当該サンプリングデータの測定結果に基づいて統計データ16を算出する統計算出手段22と、時間経過にしたがって統計データが変化する特性を表す残存期間特性データ15と、統計算出手段22が算出した統計データ16とに基づいて、監視対象データ10のデータ残存期間を表す残存期間データ17を求める残存期間検出手段とを具備する。

(もっと読む)

メモリカード

【課題】ホストから供給される電源電圧が不安定な場合であっても、メモリカードのパワーオンリセット処理を確実に行い、信頼性を大幅に向上する。

【解決手段】メモリカード1の初期設定において、フラッシュメモリ2に格納されているフラッシュ確認データFDを読み出し、そのデータFDと予めROMに格納されている動作確認用データFD11 とを比較し、異常がなければROM4aに格納された書き込み確認データFD12 をフラッシュメモリ2に書き込み、そのデータを再び読み出してROM4aの書き込み確認データFD12 と比較する。これらのデータ比較に異常がなければ、CPU4cはフラッシュメモリ2が正常と判断する。また、データ比較が異常の場合、CPU4cはレジスタ5aにリセット処理異常データを設定し、該コントローラ3をスリープモードにする。この期間にコマンドCMDを受けると再びデータ比較を実行する。

(もっと読む)

メモリ制御装置、メモリ装置及びこれらを用いた画像形成装置

【課題】メモリモジュールとメモリコントローラとの間で発生した異常を検出すると共に、該異常が発生した箇所を判定することが可能なメモリ制御装置及びそれを備える画像形成装置を提供すること。

【解決手段】メモリI/Fコントローラ19は、Vcc電源、及びGND電源に対してメモリモジュール11と接続された制御線CL1,CL2,・・・,CLnのうち何れかの制御線にVcc電圧又はGND電圧を交互に印加させるスイッチ制御部41と、スイッチ制御部41によって制御線CL1,CL2,・・・,CLnに印加させられたVcc電圧、及びGND電圧を検出するI/O制御部21と、Vcc電圧及びGND電圧の検出値と、Vcc電圧及びGND電圧の印加値を比較し、比較結果に基づいて制御線CL1,CL2,・・・,CLnの異常原因を判定する比較/判定部43と、異常原因に関する情報を出力する入出力部24とを備える

(もっと読む)

記憶装置

【課題】多ビットのメモリ故障であっても、効率よく、主記憶装置が使用不可になることを回避する。

【解決手段】主記憶装置2の初期化において、主記憶装置初期化/故障検出部6は、キャッシュメモリ5のキャッシュ有効フラグ4aに’0’を設定し、キャッシュメモリ5を無効とする。その後、主記憶装置2のSバイト領域に検査データWを記憶させた後に、主記憶装置2のSバイト領域を読み取った後、検査データWの反転データである検査データWWを主記憶装置2のSバイト領域に記憶させて、そのSバイト領域のデータを読み取る。検査データW,WWと読み取ったデータとが同じでない場合、主記憶装置2のSバイト領域が異常と見なし、そのSバイト領域をキャッシュメモリ5の任意のメモリ領域に割り付けて該Sバイト領域を救済する。

(もっと読む)

セルフテスト機能のあるメモリコントローラ及びそれをテストする方法

【課題】メモリコントローラのデータ及びデータタイミング信号をフィードバックして短時間内にメモリコントローラをテストする。

【解決手段】セルフテスト機能を追加したメモリコントローラはテストモードでテストデータを生成するテスト制御部、データ読み取りタイミング信号を生成し、データ読み取りタイミング信号に同期して生成されたテストデータとデータ読み取りタイミング信号を出力するデータ伝送部及び出力されたテストデータ及び出力されたデータ読み取りタイミング信号をデータ伝送部にフィードバックするデータ入出力部を含む。データ伝送部はフィードバックされたデータ読み取りタイミング信号に基づいてフィードバックされたテストデータを復元し、テスト制御部は復元されたテストデータと生成されたテストデータとを比較してテストを実施する。

(もっと読む)

評価システム及びその評価方法

【課題】従来の評価システムでは、記憶装置で発生するエラーを忠実に再現することができない問題があった。

【解決手段】本発明にかかる評価システムは、読出しクロックに基づき読出しデータを出力する記憶装置30と、記憶装置30に対して、読出しアドレスを出力し、読出し処理を実行するマイクロコンピュータ10と、記憶装置30とマイクロコンピュータ10との間で送受信される読出しアドレス及びモード信号に基づきエラー信号を生成し、エラー信号を出力するエラー発生回路20とを有し、マイクロコンピュータ10は、エラー信号が読出しデータの誤りを示す状態において、記憶装置30から受信した読出しデータに関わらず読出しデータを誤りと判定するものである。

(もっと読む)

1 - 20 / 30

[ Back to top ]