Fターム[5B033DD01]の内容

Fターム[5B033DD01]の下位に属するFターム

アドレス割付 (35)

汎用レジスタ (60)

制御レジスタ (18)

ワーク、入出力レジスタ (10)

2ポートレジスタファイル (6)

レジスタ・バス・ALU構成 (55)

Fターム[5B033DD01]に分類される特許

1 - 20 / 37

半導体集積回路

【課題】性能低下を招くことなく回路面積を削減出来る半導体集積回路を提供すること。

【解決手段】第1メモリ30と、第1メモリ30に対するキャッシュメモリとして働く第2メモリ10とを備える。第1メモリ30からデータが読み出される場合の第1読み出し、第2メモリ10からデータが読み出される場合の第2読み出し、及び該データを第2メモリ10から読み出すと決定する判定、は、複数の処理ステージのうちのいずれかの処理ステージで実行される。第1読み出しにて読み出されたデータが出力されるタイミングと、第2読み出しにて読み出されたデータが出力されるタイミングとは同一である。第1読み出しで読み出されたデータは、第2メモリ10を経由しない経路を用いて出力される。

(もっと読む)

演算処理装置及び演算処理方法

【課題】レジスタからの読み出しデータにおける誤り検出時に、プログラム実行動作を停止することなく、継続して実行可能である演算処理装置を提供する。

【解決手段】演算処理装置は、レジスタから読み出したデータのエラーを検出し訂正する訂正制御部と、命令の実行要求に応じてキャッシュ領域又はノンキャッシュ領域にアクセスするとともに、実行要求された一の命令がノンキャッシュ領域にアクセスするロード命令であることを通知するキャッシュ制御部と、一の命令がノンキャッシュ領域にアクセスするロード命令であることがキャッシュ制御部により通知されると、一の命令をキャッシュ制御部に実行させる間、他の命令の実行を待たせることにより、ノンキャッシュ領域にアクセスするロード命令の実行中にエラーが検出されないようにする命令実行制御部とを含む。

(もっと読む)

プロセッサ

【課題】レジスタファイルからの読み出し動作に係る電力消費を抑制しプロセッサの消費電力を低減する。

【解決手段】命令デコードステージでのデコード結果に基づく読み出しオペランド指定信号ROPRA又は前のサイクルでレジスタファイル33に出力した読み出しオペランド指定信号ROPRBを、オペランド制御信号OPRCに応じて現サイクルの読み出しオペランド指定信号ROPRBとして出力する指定信号制御回路31、32を有する。レジスタファイルから演算器36等へデータ供給が不要なサイクルでは、指定信号制御回路が、前のサイクルの読み出しオペランド指定信号ROPRBを現サイクルの読み出しオペランド指定信号ROPRBとして出力し、レジスタファイルからのデータ読み出しに係る信号変化を抑止して電力消費を抑制し、プロセッサの消費電力を低減できるようにする。

(もっと読む)

周知のプロセッサーステートに基いてCAMリネーミングレジスタファイルにおいてコンパレーターを選択的にイネーブルにするための電力節約方法および装置

【課題】リネーミングレジスタファイルの電力を節約する。

【解決手段】マッピングユニットは、インストラクションレジスタナンバー(IRN)を論理レジスタナンバー(LRN)に変換する。リネーミングレジスタファイルは、LRNを物理レジスタナンバー(PRN)にマップする。IRNの直接の使用によりアドレス可能なものよりより多い数の物理レジスタがある。リネーミングレジスタファイルはコンテンツアドレッサブルメモリ(CAM)を使用してマッピング機能を提供する。リネーミングレジスタファイルCAMはさらに現在のプロセッサー状態情報を用いてタグコンパレーターを選択的にイネーブルにしレジスタをアクセスする際の電力を最小にする。タグコンパレーターがイネーブルにならないとき、それは低電力状態になる。低電力特徴を有したリネーミングレジスタファイルを用いてプロセッサーも記載される。

(もっと読む)

半導体集積回路

【課題】性能低下を招くことなく回路面積を削減出来る半導体集積回路を提供すること。

【解決手段】データを保持する第1メモリ30と、前記第1メモリ30に対するキャッシュメモリとして働く第2メモリ10とを備え、前記データに対する読み出し処理と書き込み処理とを複数の処理ステージによりパイプライン実行する半導体集積回路1であって、前記読み出し処理の対象となるデータを前記第1メモリ30から読み出すと決定された場合に、該データの前記第1メモリ30からの読み出しを前記処理ステージのいずれかRR、RR/CRにおいて行う。

(もっと読む)

プロセッサ、プロセッサのデータ処理方法、情報処理装置

【課題】 大容量のレジスタファイルから小さいレイテンシで大量のデータを効率よく計算することができるプロセッサを提供する。

【解決手段】 プロセッサは、演算手段と、演算手段にクロスバースイッチを介して接続する複数の少ポート大容量のRAMをインタリーブ化したレジスタファイルと、演算手段の演算結果を格納し、クロスバーを介して演算結果をレジスタファイルに書き戻すと共に、クロスバーをバイパスするパスを介して演算手段に格納データを出力するレジスタキャッシュとを含む。

(もっと読む)

情報処理装置

【課題】レジスタの特定ビットに対して不要に書き換えられないようにすること。

【解決手段】本発明の情報処理装置は、複数ビットを有するレジスタ24−4を備える周辺回路20−3と、データバス12と、データバス12を介してレジスタ24−4の複数ビットのうちの特定ビットに対してアクセスするCPU11と、を具備している。周辺回路20−3は、レジスタ24−4の特定ビットに対してアクセスする内部回路21と、CPU11と内部回路21とでレジスタ24−4の特定ビットに対するアクセスが競合しないように、CPU11又は内部回路21を優先する制御回路22と、を更に備えている。

(もっと読む)

プロセッサ、プロセッサの実行制御方法及びそのプロセッサのためのプログラム生成装置

【課題】プロセッサにおいてレジスタファイルの低消費電力化を図ることのできるプロセッサを提供する。

【解決手段】プロセッサ1は、複数のレジスタを有するレジスタファイル12と、レジスタファイル12における、電源の供給を停止する1以上のレジスタを選択可能なスイッチ素子群回路12aと、オブジェクトコードの実行時に、オブジェクトコードに含まれる、使用するレジスタ数あるいは使用しないレジスタ数の情報に基づいて、レジスタファイル12を制御するためのレジスタファイル制御信号を出力する実行部21と、レジスタファイル制御信号に基づいて、電源の供給を停止する1以上のレジスタを選択するためのレジスタ制御信号をスイッチ素子群回路12aに出力するレジスタファイル制御部16とを有する。

(もっと読む)

プロセッサ、レジスタアクセス方法およびレジスタアクセスプログラム

【課題】レジスタスピル処理が発生してもプログラムの実行速度の低下を防ぐことのできるプロセッサの提供。

【解決手段】本実施の形態にかかるプロセッサでは、物理レジスタ120のうち、レジスタリネーミングによって論理レジスタ110との対応付けがされていない物理レジスタに、論理レジスタ:Lレジスタ0に格納されている値を格納する。物理レジスタ120のうち、PレジスタXXは、論理レジスタとの対応付けがされておらず、“空いた”状態である。したがって、論理レジスタ:Lレジスタ0に格納されている値を物理レジスタ:PレジスタXXに格納し、待避命令の処理が完了する。また、このとき待避命令に記述されていたアドレスXと物理レジスタ:PレジスタXXとが対応付けられたことを対応表140に反映させる。

(もっと読む)

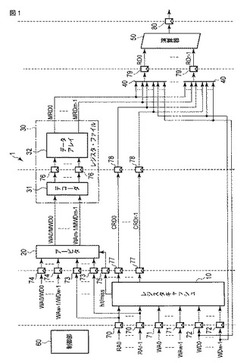

プロセッサおよびそれを用いたマイクロコンピュータシステム

【課題】汎用レジスタを用いないプロセッサを提供すること。

【解決手段】複数のCo−CPUが互いに接続され、複数のCo−CPUが別個の演算を並列に実行するプロセッサが提供される。複数のCo−CPUのそれぞれは、コマンドデコーダ22と、ALU21と、複数のセレクタ23〜36とを含む。コマンドデコーダ22は、コマンドコードをデコードする。セレクタ23〜28は、隣接する複数のCo−CPUからの出力およびMRAMからの出力を受け、少なくとも1つを選択的に出力する。ALU21は、セレクタ27および28からの出力に対してコマンドデコーダ22によるデコード結果に応じた演算を行なう。セレクタ31〜32は、ALU21による演算結果および隣接する複数のCo−CPUからの出力を受け、隣接する他の複数のCo−CPUに選択的に出力する。したがって、汎用レジスタを用いないプロセッサを提供することが可能になる。

(もっと読む)

キュープロセッサ、キュープロセッサによるデータ処理方法、およびキュープロセッサに用いるデータ処理プログラム

【課題】高い汎用性を有し、高速な演算処理が可能なキュープロセッサ、キュープロセッサによるデータ処理方法、およびキュープロセッサに用いるデータ処理プログラムを提供する。

【解決手段】演算処理の中間結果格納用メモリとして用いられる第1演算データ格納用キュー18の、キューヘッダQHの位置から所定ワード離れた位置に格納された第1データと、キューヘッダQHの次の位置から所定ワード離れた位置に格納された第2データとを取得し、第1データと第2データとを用いて演算処理を行い、演算結果を第1演算データ格納用キュー18のキューテールQTから所定ワード離れた位置に格納する実行ユニット17を備えることを特徴とする。

(もっと読む)

マイクロプロセッサ

【課題】レジスタの選択処理の高速化を図る。

【解決手段】プログラムコードには、オペランド10によって所定のレジスタが指定されている。プログラムコードより読み込まれたオペランド10は、オペランド保持部1に格納されるとともに、レジスタ指定修飾部2へ出力される。レジスタ指定修飾部2は、プログラムコードより読み込まれたオペランド10とともに、制御信号5を入力し、オペランド10内の修飾フィールドの値を入力した制御信号の値に応じて修飾する。レジスタ選択部3は、修飾されたオペランド10によって指定されるレジスタを選択し、アクセス可能とする。

(もっと読む)

演算装置

【課題】演算途中の結果が汎用レジスタのビット幅を超えるような演算においても、チップに対する占有面積の増加を抑えて、高精度の演算が可能な演算装置を提供する。

【解決手段】複数の汎用レジスタ12は、第1のビット幅を有している。演算器13は、第1、第2の入力端を有し、少なくとも第1の入力端が第1のビット幅より広い第2のビット幅を有し、汎用レジスタ12から第1、第2の入力端に供給されるデータを演算する。第1のビット幅より狭いビット幅を有する第1、第2のレジスタov0、ov1は、演算器13による演算の結果、あふれた桁のデータをオーバーフローデータとして保持し、演算器13の少なくとも一方の入力端に、上位ビットとして保持したオーバーフローデータを供給する。

(もっと読む)

適応性を有するマイクロプロセッサのレジスタファイル

レジスタファイル内の複数の形式のデータを閲覧するアーキテクチャ及び方法である。開示された様々な実施形態により、一のレジスタファイル内の複数の連続したレジスタが一つの命令によって見かけ上一時的に転置され、各転置されたレジスタが複数の連続したレジスタからの1バイト又は1ワードを含むことが可能になる。あるプログラムでは、レジスタ内のバイトに保存された値を同じレジスタ内のほかのバイトに保存された値と交換することによって、レジスタ内のバイトを任意に再編成することができる。レジスタの間接アクセスも、追加のスコアボーディング用ハードウェアを使用せずに一つのレジスタから別のレジスタへの見かけの移動によって実施することができる。I/OにおけるハードウェアデータFIFOの機能性も、レジスタからレジスタへの転送における電力消費を伴わずに付与されている。しかしながら、FIFOのサイズはプログラム制御下において変更可能である。  (もっと読む)

(もっと読む)

レジスタファイルの書き込み/読み出し方式

【課題】FPGA等で構成するマイクロプロセッサのレジスタファイルを、単一アドレスポートのRAMを使用して実現する。

【解決手段】レジスタファイルは、単一アドレスポートの非同期式RAM11と、パイプラインのステージ毎に、RAMのリードアドレスとライトアドレスを切り替えるマルチプレクサ12と、切り替えに同期してRAMの出力データを一時ラッチするフリップフロップ回路13とで構成する。

レジスタファイルを、単一アドレスポートの同期式RAMと、パイプラインのステージ毎にRAMのリードアドレスとライトアドレスを切り替えるマルチプレクサとする構成も含む。

(もっと読む)

算術プロセッサ

【課題】有限体演算やモジュラ整数演算など一群の関連する算術演算をそれぞれパフォームする複数の算術回路を有するALUを含むことを特徴とする算術プロセッサを提供する。

【解決手段】ALUは、オペランドデータを受信するオペランド入力データバスと、算術演算の結果を戻す結果データ出力バスとを有する。レジスタファイルはオペランドデータバスと結果データバスに結合されている。レジスタファイルは複数の算術回路によって共用されている。コントローラは、ALUおよびレジスタファイルに結合され、算術演算を要求するモード制御信号に応答して、複数の算術回路の1つを選択し、レジスタファイルとALUとの間でデータアクセスを制御し、それによりレジスタファイルが算術回路によって共用されるようにする。

(もっと読む)

マイクロプロセッサおよびその制御方法

【課題】 レジスタバンク切り替え機能によるスループットの低下を抑制できるマイクロプロセッサおよびその制御方法をを実現する。

【解決手段】 本発明のマイクロプロセッサおよびその制御方法は、データをレジスタR0〜Rnに格納した時のバンク番号B0〜BnがR0〜Rnごとに設定されているレジスタペア12と、複数のレジスタペア12を備えたCPUレジスタ11と、CPUレジスタ11の情報がレジスタペア12の単位で退避、回復されるレジスタファイル13と、データを演算処理する前に、当該レジスタペア12のB0〜Bnと現在のバンク番号19とを比較して入れ替え要求信号24を出力する比較器15と、入れ替え要求信号24を受けて、当該レジスタペア12の情報をレジスタファイル13との間で退避、回復するレジスタ入れ替え回路16を有する。

(もっと読む)

映像処理エンジンおよびそれを含む映像処理システム

【課題】CPUが発行する命令は、1サイクルに1命令以上が供給されるため、毎サイクル、命令メモリ読み出しが発生し、消費電力が大きい。また、マルチプロセッサ構成の場合、命令メモリ個数が増加し、毎サイクル、命令メモリの同時アクセスが発生し、消費電力が大きくなる。

【解決手段】命令のオペランドに2次元のソースレジスタとデスティネーションレジスタを指定する手段を設け、複数サイクルで、複数のソースレジスタを使用した演算を実行し、複数のデスティネーションを得る。複数ソースレジスタを利用して、複数サイクル消費してデスティネーションを得る命令において、データ丸め込み演算器をパイプラインの最終段に接続する。更に、複数のCPUを直列接続し、共有型の命令メモリを共有して使用する。この際、各CPUの命令オペランドに、隣り合うCPU間の同期を制御するためのフィールドを有し、同期化制御を行う。

(もっと読む)

汎用レジスタ回路

【課題】所望の信号出力の高速化を図ることが可能な汎用レジスタ回路を提供する。

【解決手段】本発明に係る汎用レジスタ回路100は、マトリクス状に配置されるとともに、データを書き込み読み出すためのワード線2およびビット線3に接続された複数のメモリセル4と、ビット線3が入力に接続されるとともに出力選択信号が伝送される制御線6が接続され、出力選択信号の入力に基づいて、メモリセル4から読み出されビット線4を介して入力されたデータの値と固定値とを切り替えて出力する複数のマルチプレクサ回路5と、を備える。

(もっと読む)

プロセッサ及びそのデータ処理方法

【課題】レジスタ・キャッシュを有効に活用し、処理性能を好適に向上することのできるプロセッサ及びそのデータ処理方法を提供する。

【解決手段】メイン・レジスタ・ファイルとレジスタ・キャッシュとに階層化された階層型レジスタ・ファイルを有するプロセッサにおいて、レジスタ・キャッシュのアクセスに係るインデクスを、メイン・レジスタ・ファイルの物理レジスタ番号から一義的に決定するとともに、未使用の物理レジスタ番号のモジュロ・ソートを行って、命令のフェッチ順にインデクスがラウンド・ロビンとなるように、レジスタ・リネーミング中の命令に対する物理レジスタ番号の割り当てるようにした。

(もっと読む)

1 - 20 / 37

[ Back to top ]