Fターム[5B042GC02]の内容

デバッグ、監視 (27,428) | 対象とデバッガ、監視装置間の情報授受 (1,172) | 端子ピン (173) | デバッグ、監視専用端子ピン (99)

Fターム[5B042GC02]の下位に属するFターム

内部状態出力端子ピン (37)

Fターム[5B042GC02]に分類される特許

1 - 20 / 62

バリアトランザクションのデバッグ

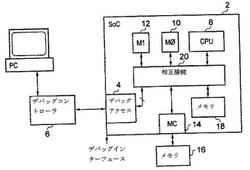

【課題】集積回路をデバッグするための技術を提供する。

【解決手段】集積回路2は、相互接続回路20を介してデータトランザクションを発行するための、1つ以上のトランザクションマスター8、10、12、4を含む。デバッグアクセスポート回路は、デバッグコントローラ6から受信されるデバッグコマンドに応答して、相互接続回路に発行されるバリアトランザクションを発生させるように構成される。相互接続回路は、データトランザクションの少なくともいくつかの相対的順序付けを、それらが相互接続回路を通過する時に抑制することによって、受信したバリアトランザクションに応答する。

(もっと読む)

エミュレータ及びデバッグ方法

【課題】JTAG-ICEにおいて、LSIの入出力状態をトリガとするエミュレーションのブレークを実現する「エミュレータ及びデバッグ方法」を提供する。

【解決手段】エミュレーション処理部23は、LSI31のICE制御ブロック314に命令を発行し、所定のプログラムをコアロジック311に実行させ、スキャン処理部24は、LSI31のコアロジック311のプログラムの1ステップ実行毎のスキャン動作を、LSI31のバウンダリスキャン制御ブロック315に行わせ、LSI31の各入出力端子312の状態をスキャンデータメモリ25に格納する。エミュレーション処理部23は、スキャンデータメモリ25からLSI31の各入出力端子312の状態を読み出し、読み出した各入出力端子312の状態が、予めブレーク条件メモリ26に設定されているブレーク条件にマッチするかどうかを調べ、マッチしていればプログラムの実行をブレークする。

(もっと読む)

障害検出方法、制御装置、マルチプロセッサシステム

【課題】複数のパーティションにハードウェア分割された装置では、通信経路上で障害が発生した場合は、障害発生箇所の特定が困難であり、人手での部品交換による部品の特定を実施する必要があるため、被疑判断に時間を要していた。

【解決手段】

本発明の制御装置は、第1のインタフェースを用いて外部装置と通信を行う通信手段と、通信に障害が発生したことを検出する検出手段と、検出手段で検出された障害をカウントする第1カウント手段と、検出手段で障害が検出された場合に、第1カウント手段をカウントアップする制御を行うと共に、外部装置のカウント手段をカウントアップする制御を第2のインタフェースを用いて行うカウント制御手段と、を具備する。

(もっと読む)

半導体集積回路及び半導体集積回路のバス制御方法

【課題】ROMエミュレータによるプログラムのデバッグでは、専用のコネクタをCPUが実装された基板に設ける必要ある。このコネクタを追加することにより、配線抵抗が上昇し、メモリのアクセスタイミングを悪化させる。そこで、メモリ間のアクセスタイミングに影響を与えずに、プログラムのデバッグを実現する半導体集積回路を提供する。

【解決手段】半導体集積回路は、メモリに対するアクセスを制御するメモリコントローラと、メモリコントローラの端子と外部端子の間に配置されるバウンダリスキャン回路と、バウンダリスキャン回路の動作モードを決定するモード信号の出力が可能なJTAGインターフェイスと、プログラムのデバッグ時に、モード信号に基づいて、メモリコントローラのリードアクセスを許可する制御信号を、バウンダリスキャン回路を介して、メモリコントローラに発行するタイミング制御回路と、を備える。

(もっと読む)

半導体装置

【課題】デバッグ端子部を介してのリバースエンジニアリングを防止できるようにする。

【解決手段】デバッグ端子部制御回路3は、CPU4で実行されたデバッグ用プログラムP1の中から有効化ルーチンR1を抽出し、該抽出した有効化ルーチンR1に基づいて、デバッグ端子部2で受信されるデバッグ入力信号S4をCPU4に入力するようにデバッグ端子部2を制御する。これにより、外部メモリ7aにデバッグ用プログラムP1が記憶されているときには、デバッグ端子部2が有効になってデバッグ入力信号S4がCPU4

に入力されるが、外部メモリ7aにデバッグ用プログラムP1が記憶されていないときには、デバッグ端子部2が無効になってデバッグ入力信号S4がCPU4に入力されない。この結果、出荷時にデバッグ端子部2を無効化することにより、デバッグ端子部2を介してのリバースエンジニアリングを防止できる。

(もっと読む)

マイクロコンピュータ

【課題】ユーザーが容易に変更できないように管理されている保護領域へのアクセスを、修理店等において簡易に行うことが可能なマイクロコンピュータを提供すること。

【解決手段】外部とのデータ通信を行う通信手段を備え、エントリーレベルに応じて、前記通信手段を用いた外部から所定の保護領域へのアクセスが制限されているマイクロコンピュータであって、外部から所定のデバッグモード開始信号を入力可能な入力受付手段と、前記入力受付手段に所定のデバッグモード開始信号が入力されたときに、前記所定の保護領域へのアクセス制限を緩和するように制御するデバッグモード制御手段と、を備えるマイクロコンピュータ。

(もっと読む)

インサーキットエミュレータ用アダプタおよびインサーキットエミュレータ

【課題】CPUコア用インサーキットエミュレータ(ICE)と、遊技機向け付加回路の機能をエミュレートするICE用アダプタとで構成されるICEにおいて、ブレーク中に、ICE用アダプタに搭載されている遊技機向け付加回路の内部状態を保存したまま、その付加回路内のメモリやレジスタからデータを読み出す

【解決手段】乱数回路11やウォッチドッグタイマ12のように状態遷移回路を含む回路では、CPUコア用ICE20がブレークされているとき、状態遷移回路の状態遷移を停止させる。受信用FIFO回路13のリードポインタのように、CPUコア用ICE20がレジスタやメモリの内容を読み出すと内部状態が変化する回路では、内部状態を保存したままレジスタやメモリの内容を読み出すことができる回路を付加する。

(もっと読む)

データ処理装置

【課題】複数のCPUを含むデータ処理装置において、円滑なトレースを可能とするための技術を提供する。

【解決手段】それぞれ供給されたCPU用クロック信号(clki0,clki1)に同期動作する複数のCPUと、供給されたデバッグ用クロック信号(clkd)に基づいて、上記複数のCPUで実行されるユーザプログラムのデバッグを可能とするデバッグ回路(200)とを含むデータ処理装置において、上記デバッグ回路に供給されるデバッグ用クロック信号の周波数をf1とし、上記複数のCPUに供給されるCPU用クロック信号の中で最も高い周波数をf2とするとき、f1≧f2が成立するように上記デバッグ用クロック信号及び上記CPU用クロック信号を形成するためのクロック制御回路(300)を設ける。

(もっと読む)

プログラム検証方法、プログラム検証装置、及び携帯端末装置

【課題】 携帯電話機の筐体の解体することなく、セキュリティ性を維持した状態でJTAG信号の取り出しを可能とする。

【解決手段】 携帯電話機のCPUコア22は、音声出力端子15を介してハイレベル(H)のデバッグモード移行制御信号が供給され、なおかつ、正規のユニーク認証コードが供給された場合のみ、デバッグモードに移行する。携帯電話機の外部メモリ装着部16には、一端がカード型半導体メモリの形状となっているパラレルデータラインが接続されており、デバッグモードに移行した際には、このパラレルデータラインを介してCPU19のJTAGコントローラ23とデバッガ装置31とを接続して、検査対象となっているソフトウェアプログラムのデバッグを行う。

(もっと読む)

半導体装置及びその診断システム

【課題】トレース用端子を増設することなく、最小限のメモリで、複数リソースのトレースを実行する。

【解決手段】半導体装置は、同じ内容のプログラムが実行される毎に、ROM1のアドレス、RAM2のアドレス、RAM2の中から、選択すべき1つのデータを切り替えて、トレース情報として出力するセレクタ12と、前記同じ内容のプログラムが実行される毎にセレクタ12により選択されたトレース情報を記憶し、次の同じ内容のプログラムが実行される前に前記記憶されたトレース情報が読み出されるトレース用メモリ17と、を備えている。

(もっと読む)

集積回路、デバッグ回路、デバッグコマンド制御方法

【課題】、内蔵するデバッグ回路からメモリ等の内部リソースに直接にアクセスできる構成において、バスを効率的に使用可能なようにバス権獲得要求及び承認を制御する集積回路を提供する。

【解決手段】集積回路は、バスと、ユーザプログラムを実行する処理ユニットと、処理ユニットからの命令転送要求に応答して処理ユニットにバスを介して命令レジスタ内の命令を転送する、バスに接続されたデバッグ回路とを含み、処理ユニットがユーザプログラムの実行を中断して命令転送要求をデバッグ回路に対して行なうと、デバッグ回路は、命令転送要求と命令転送動作との間の期間においてバスの使用権を前記処理ユニットから解放させる応答を行なう。

(もっと読む)

デバッグシステム

【課題】ターゲットマシンの構成を複雑化することなく、汎用性の高いUARTを用いたクロスデバッグ環境を提供する。

【解決手段】ターゲットマシン3において、識別回路13は、UART12で受信された8ビットのデータ(キャラクタ)の上位2ビットから、当該データがコマンド、アドレスまたは書込データのいずれであるかを識別する。コマンドデコーダ19は、コマンドとなるデータをコマンドにデコードしてターゲットCPU11に与える。また、アドレスレジスタ20は、アドレスとなるデータを4回の受信で24ビットのアドレスを蓄える。また、データレジスタ21は、書込データとなるデータを11回の受信で64ビットの書込データを蓄える。これにより、UART12のプロトコルを上記の回路によって実現することができ、当該プロトコルをソフトウェアで実現する場合のように、当該ソフトウェアを実行するCPUやその周辺回路を別途必要としない。

(もっと読む)

情報処理装置、秘密情報保護システムおよび秘密情報保護方法

【課題】秘密情報を保護する仕組みを有し、しかもデバッグを可能にする情報処理装置、秘密情報保護システムおよび秘密情報保護方法を得ること。

【解決手段】秘密情報保護システム100は、DTCPシンクデバイス101とDTCPソースデバイス102をLANケーブル103で接続した構成となっている。ここで保護されたコンテンツを要求してその再生を行うDTCPシンクデバイス101は、秘密情報を格納したセキュアCPU部121と、これと回路的に遮断されデバッガ104を接続可能な回路部分でコンテンツの再生を行う。

(もっと読む)

半導体集積回路装置

【課題】ソフトウェアの開発や保守におけるデバッグ作業を効率的に行うことのできる半導体集積回路装置を提供する。

【解決手段】半導体集積回路装置1の内部回路10で実行されるソフトウェアのデバッグを行うデバッグ回路2は、インターフェイス部24から入力される機能構成情報によりプログラマブルロジック部21の機能が構成され、デバッグポート22を介して、デバッグに必要な内部回路10の信号端および内部バスがプログラマブルロジック部21へ接続され、プログラマブルロジック部21から出力されてトレースメモリ23に格納されたデータを、インターフェイス部24から外部へ出力する。

(もっと読む)

マイクロプロセッサのモニタ回路により伝送されるメッセージの時間的相関

【課題】 マイクロプロセッサ(12)に集積化されるモニタ回路(18)の出力ターミナル(22)を介してデジタルデータメッセージを伝送する方法を提供する。そのメッセージは、マイクロプロセッサによる命令実行時に発生する決められたイベントを表す。本発明はまた、デジタルデータメッセージを伝送するための装置を提供する。

【解決手段】 方法は、特定のイベントに関連する少なくとも1つの特定のデジタルデータメッセージの伝送前又は伝送後に、特定のデジタルデータメッセージの識別子と、特定のデジタルデータメッセージの伝送に関連する命令及び先行のデジタルデータメッセージの伝送に関連する命令の間にマイクロプロセッサにより実行される命令の数のカウンタとを含む相関メッセージを伝送することから成るステップを有する。

(もっと読む)

半導体モニタ装置、半導体モニタ装置の通信条件設定方法、及びシミュレーションシステム

【課題】半導体装置が組み込まれる制御基板に、調整用の特別の回路を設けることなく、送受信データの位相調整、及び、受信データの受信開始タイミングの調整を容易に行なうことができる半導体モニタ装置を提供する。

【解決手段】コマンドデータを送信しコマンドデータに応答して返信される応答データを受信する通信インタフェース部51と、通信インタフェース部51を介して動作中の半導体装置2から受信した応答データに基づいて半導体装置2のリソース状態をモニタする半導体モニタ装置5であって、半導体装置2に備えた記憶部から通信インタフェース部51を介して検証データを読み出すデータ読出し処理部52と、データ読出し処理部52により読み出された検証データに基づいて通信インタフェース部51の通信条件を設定する通信条件設定部53を備えている。

(もっと読む)

半導体集積回路

【課題】本発明は、バッグ解析等に必要な内部ステータス信号を高精度に取得して出力する集積回路に関する。

【解決手段】ASIC1は、内部信号出力回路3を搭載しており、内部信号出力回路3は、機能モジュールMa〜Md、PCIe I/FモジュールMe、MfのステータスレジスタRa〜Rfのアドレスが、読み出し対象アドレスとしてアドレス指定レジスタ3bに外部のCPU10から設定指定されると、ポーリング間隔設定レジスタ3aに設定されているポーリング周期で該アドレス指定されているステータスレジスタRa〜Rfの内部ステータス信号を読み出して、外部端子4からASIC1外に出力する。したがって、ステータスレジスタRa〜Rfの内部ステータス信号を短サイクルで正確に読み取って外部に出力することができ、デバッグ等を正確かつ容易に行うことができる。

(もっと読む)

半導体集積回路装置及びその信号処理方法

【課題】情報の秘匿性を確保しつつ開発効率を向上出来る半導体集積回路装置及びその信号処理方法を提供すること。

【解決手段】暗号化データを保持する第1メモリ3と、前記暗号化データの平文を保持する第2メモリ4と、第1動作モードにおいてデバッグ制御回路12から独立し第2動作モードにおいて前記デバッグ制御回路12の支配下に置かれるプロセッサ11と、前記第2動作モードにおいて前記プロセッサ11を制御する前記デバッグ制御回路12と、前記暗号化データの正統性を認証するデータ認証部6と、前記第2動作モードにおいてフラグを保持するレジスタ13と、前記第2メモリ4へのアクセスを制御する第2メモリ制御回路5とを具備し、前記第2メモリ制御回路5は前記レジスタ13に前記フラグが保持されておらず且つ前記データの正統性が認証された場合に前記第2メモリ4へのアクセスを許可する。

(もっと読む)

コンピュータシステムのデバイス監視方式

【課題】監視対象デバイスの増設や変更にも柔軟にかつ容易に対応できる。

【解決手段】RAS機能付きインタフェース4と監視対象デバイス3A、3B、5C〜5NとはRAS専用の1本のシリアル伝送路6で接続し、ホスト側になるインタフェースからは各デバイスに対するポーリングで各デバイスの異常の有無を監視する。

ポーリングにはホスト側から各デバイスにステータス信号をそれぞれ要求し、各デバイスからのステータス信号の応答の有無、及びステータス信号の正常/異常の判定で当該デバイスの異常の有無を判定する。

(もっと読む)

マイクロコンピュータ、デバッグシステム、デバッグ方法

【課題】ハードウェアコンポーネント間のバス信号の衝突をモニタし、ソフトウェアのデバッグ処理効率を向上させる。

【解決手段】マイクロコンピュータ10は、デバッグ装置と通信を行ってオンチップデバッグ機能を実現するデバッグコントロールユニットDCUを有するマイクロコンピュータであって、マイクロコンピュータ10の外部バスBUSに接続された機器の通信を制御する外部バスコントローラ13と、外部バスコントローラ13から出力され、外部バスBUSへ出力されるべき第1外部バス信号B1をモニタする外部バスモニタ14と、外部バスモニタ14によってモニタされた第1外部バス信号B1が記憶されるメモリ(リングバッファ22)と、を有するものである。

(もっと読む)

1 - 20 / 62

[ Back to top ]