Fターム[5B047EA07]の内容

Fターム[5B047EA07]に分類される特許

261 - 271 / 271

画像処理機能メモリ

【課題】 システムバスより高速なメモリバスを用いる機能メモリを提供する。

【解決手段】 CPUがSDRAMから入力データを読み出し、その後にCPUがそのデータを画像処理機能メモリに書き込む従来のCPUによるデータの転送方式に比して、CPUのSDRAM読取り動作のみでデータを入力させるので、アクセス回数が半分になりデータの移動が高速化できる。

(もっと読む)

マーカー装置及びそれを備えた画像読取装置

【課題】画像読取装置において、ラインイメージセンサ間の継ぎ目補正を高精度に行うことを目的とする。

【解決手段】副走査方向に伸びる第1の補正用パターンCと、走査面上において、主走査方向の主走査座標に対し副走査座標が一意的に決定し、且つ、各イメージセンサ3の読み取りラインと2点で交わる第2の補正用パターンL、Rと、前記第1の補正用パターンCと前記第2の補正用パターンL、Rとを照射するマーカー照射部50とを有するマーカー装置を備える構成とする。

(もっと読む)

画像処理装置及び画像形成装置

【課題】符号データが生画像データよりも大きくなった場合でも、効率よく大容量記憶手段へデータを格納する。

【解決手段】入力された白黒画像データを圧縮、伸長する圧縮伸長手段と、画像データを一時的に記憶する画像メモリと、画像データを大量に記憶する大容量記憶装置と、前記画像データを前記画像メモリおよび/または大容量記憶装置へ記憶させる制御手段とを備えて画像処理装置において、前記制御手段は、前記圧縮伸長手段によって圧縮され、符号化されたデータの前記画像メモリへの格納と、前記画像データの前記大容量記憶手段への格納とを並行して行わせる。

(もっと読む)

画像合成装置

【課題】低コストで高速かつ自在に画像合成可能な画像合成装置を提供すること。

【解決手段】画像が入力される複数の入力チャンネルと、各入力チャンネルに入力された画像データを読み出し可能に格納する入力メモリ20と、各入力チャンネルに対応して設けられ、予め設定された合成情報に含まれるアドレス情報に基づいて、入力画像を構成する任意の画素を入力メモリ20から読み出し、出力画像の任意の位置に配置して出力する画素再配置装置30と、合成情報に含まれる合成比率情報に基づいて、出力画像として読み出された画素を合成するための画像合成部35とを備え、画素再配置装置30により、出力画像を構成する画素をすべて読み出して再配置した後に、画像合成部35において、各画素について合成比率情報に基づく画像合成処理を行うように構成した。

(もっと読む)

画像読み取り装置

【課題】 原稿を反転させることなく原稿の両面に形成された画像の読み取りを行うに際して、画質の低下を招くことなく、所望とする領域の画像データを取得する。

【解決手段】 原稿を搬送しつつ、原稿の表面に形成された画像をCCDイメージセンサ78で読み取り、原稿の裏面に形成された画像をCIS50で読み取る。CCDイメージセンサ78で読み取られた表面の画像データは画像処理された後そのまま出力され、CIS50で読み取られた裏面の画像データは画像処理された後一旦バッファメモリ203に格納され、表面の画像データの出力終了した後に出力される。そして、例えば原稿裏面の読み取り開始側の画像データを出力したい場合には固定バッファ制御によってバッファメモリ203に書き込みを行い、例えば原稿裏面の読み取り終了側の画像データを出力したい場合にはリングバッファ制御によってバッファメモリ203に書き込みを行う。

(もっと読む)

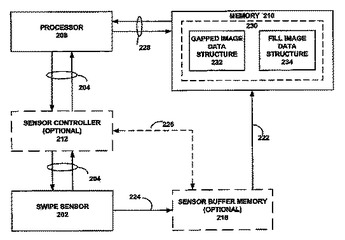

部分的な手の指の画像を作成し処理するセキュアシステム及び方法

詳細な特徴テンプレートを発生させるのに従来的に必要とされる十分な又は完全な指紋画像を決して発生させることも再構成することもなく、十分な画像指紋詳細特徴テンプレートを発生させることによって指紋センサから取得される指紋画像を作成し処理する際にセキュリティを提供する装置、システム、方法、コンピュータプログラム、及びコンピュータプログラム製造物品である。  (もっと読む)

(もっと読む)

データ値をメモリに一時的に記憶する方法

本発明は、データ値を記憶するメモリ管理ユニット(MMU)に関し、前記メモリ管理ユニットは、少なくとも2つの群のデータ値を一時的に記憶するメモリユニットと、データ値の第1の群を前記メモリユニットの第1領域に記憶するとともに、データ値の前記第1の群に水平及び/又は垂直方向に空間的に隣接するデータ値の第2の群を、データ値の前記第2の群の第1部分が、前記第1領域に水平及び/又は垂直方向にそれぞれ隣接する前記メモリユニットの第2領域に記憶されるように、及びそれぞれ水平及び/又は垂直方向に前記メモリユニットサイズを超える、記憶されるべきデータ値の前記第2の群の他の部分が、トーラス原理に従い前記メモリユニットの少なくとも1つの他の領域に記憶されるように、記憶することが可能であるように構成される制御器(CTRL)と、を備える。  (もっと読む)

(もっと読む)

データ値の多次元アレイへのパラレルなアクセスを提供するデータ処理装置

画素値の画像などのデータ値のアレイが、メインメモリに格納される。この画素値を利用して、処理演算が実行される。この処理演算は、画像における位置の多次元領域の移動の時点を規定する。領域内部及び周辺からの画素値が、処理のためにキャッシュされる。少なくとも領域の外部からの画素値に対してキャッシュミスが発生すると、キャッシュ位置におけるデータのキャッシュ置換が実行される。領域外の画像における位置に対する画素データを格納する位置が、領域内部の画像における画素データ位置を格納する置換キャッシュ位置から選択的に免除する置換のために選択される。実施例では、領域内部及び外部のデータ値をキャッシュするため、異なるタイプのキャッシュ構成が利用される。ある実施例では、領域内部の画素データに対するキャッシュ位置は、領域周辺の画素データに対するキャッシュ位置より高いレベルの出力並列化をサポートする。さらなる実施例では、領域内部の位置に対するキャッシュは、画像からの各ラインに対する各セットのバンクセットを有し、ラインからのデータは、バンク上で循環的に繰り返すようにして分散される。  (もっと読む)

(もっと読む)

データ駆動型アーキテクチャを有する画像信号プロセッサでの使用のためのメモリコマンドハンドラ

画像処理システムでの使用のための画像信号プロセッサが開示される。画像信号プロセッサは、データを記憶するローカルメモリ、及び複数のメモリアドレスジェネレータを有するメモリコマンドハンドラを含む。それぞれのメモリアドレスジェネレータは、ローカルメモリにメモリアドレスを発生し、画像処理タスクにおいて役立てるためにメモリアドレスデ位置されるローカルメモリのデータに演算を実行するためにコマンドを解釈する。 (もっと読む)

シェーディング補正回路

【課題】 取扱い画像データが大きくなっても一連の処理を短時間で実行可能なシェーディング補正回路を提供する。

【解決手段】 カメラからのp画素×qラインからなる画像を予め決められたi画素×iライン(i<p、i<q)からなるm×nのブロックに分割し、m×nからなる画像データに縮小するSHD縮小部1と、この縮小部1で縮小されたm×nからなる画像データからm×nからなるシェーディング補正データを生成するシェーディング補正データ生成部であるCPU7と、このm×nからなるシェーディング補正データをp画素×qラインからなるシェーディング補正データに拡大する拡大部3と、このp画素×qラインからなるシェーディング補正データとカメラからのp画素×qラインからなる画像データで対応する位置の画素の画像データを乗算するSHD演算部4と、からなる。

(もっと読む)

描画処理装置及び描画処理方法

【課題】効率良く画像データメモリにアクセスし、描画処理を行う描画処理装置及び描画処理方法を提供する。描画処理装置内の必要メモリ容量を低減する。

【解決手段】描画コマンドにより描画される画素を含むブロックを確定する描画処理ブロック確定部7と、処理ブロック確部7より指定されたブロックとメモリ4との読み書きを制御するメモリ制御手段4と、ブロック単位に描画処理を行う、描画ブロック処理部8を有する。

【効果】描画処理ブロック確定部7をブロック単位の描画ブロック処理部8と独立に有する事により、ブロックの読み出しに於けるメモリ制御と、ブロックの描画処理が並列に実行する事ができる。

(もっと読む)

261 - 271 / 271

[ Back to top ]