Fターム[5B048AA11]の内容

デジタル計算機の試験診断 (4,118) | 被試験装置 (1,129) | マイクロコンピュータ (293)

Fターム[5B048AA11]の下位に属するFターム

Fターム[5B048AA11]に分類される特許

1 - 20 / 69

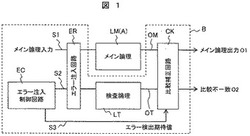

自己診断機能付き装置

【課題】自己診断する論理の範囲を比較回路以外の検査論理、更にはメイン論理に広げ、検査論理、メイン論理に異常がある場合、比較回路が不一致を発生する前に検出し装置の交換ができるようにする。

【解決手段】同じ入力が与えられ、同じ論理演算を実施する第1と第2の論理部、第1と第2の論理部のいずれかにエラー信号を与えるエラー注入回路、第1と第2の論理部の出力を入力し選択した信号を与える選択回路と第1と第2の論理部の出力を比較し、比較不一致信号を与える比較回路とを備えた比較補正回路から構成され、比較補正回路は、第1と第2の論理部のいずれかにエラー信号を与えた時、第1と第2の論理部の出力が不一致にならない場合、または、第1と第2の論理部にエラー信号を与えないときに、第1と第2の論理部の出力が不一致になる場合に異常があると判断する。

(もっと読む)

自己診断回路および自己診断方法

【課題】マイクロコンピュータの自己診断の実行時間を削減する。

【解決手段】リセット後の動作がホットスタートかコールドスタートかを判定する手段と、各機能ブロックで発生するエラーが他のどの機能ブロックへ影響があるのかの関連付け情報を保持し、通常動作時に発生したエラーがどのブロックで発生したエラーであるかを判定し、複数の機能ブロックからBISTを実行する機能ブロックを選択する手段と、選択された機能ブロックのBISTを実行する順序を関連付け情報に基づいて制御して、BISTの実行を指示する手段と、を備え、ホットスタートと判定された場合には、BISTを実行する機能ブロックを選択するとともに、選択した機能ブロックのBISTを実行する順序を関連付け情報に基づいて制御してBISTを実行し、コールドスタートと判定された場合には複数の機能ブロックのすべてのBISTを実行する。

(もっと読む)

マイクロコンピュータ

【課題】処理負荷の増大を抑制しつつ、処理結果の正確性を確保すること。

【解決手段】複数の命令実行手段を備え、該複数の命令実行手段について故障診断を行う機能を有するマイクロコンピュータであって、プログラムメモリに格納された命令を取得し、該取得した命令を解読する命令取得解読手段と、該命令取得解読手段により解読された命令に基づき、前記複数の命令実行手段に命令を発行すると共に、命令の発行先を特定する発行先特定情報を所定の記憶手段に書き込む命令発行手段と、を備え、前記複数の命令実行手段のうち、前記発行先特定情報が前記所定の記憶手段に書き込まれた命令実行手段について故障診断を行い、前記発行先特定情報が前記所定の記憶手段に書き込まれていない命令実行手段については故障診断を行わないことを特徴とする、マイクロコンピュータ。

(もっと読む)

車両制御装置

【課題】外部起動信号がオフ状態になったときに演算装置がオフになることを確認する診断を、通常動作中に実施することのできる車両制御装置を得る。

【解決手段】本発明に係る車両制御装置は、外部起動信号がオフ状態になったときにメインリレー駆動回路がメインリレーをオフ状態にすることを確認するための診断処理を、外部起動信号がオン状態のときに実行する。

(もっと読む)

電源スイッチ押下装置、電源スイッチ押下方法およびプログラム

【課題】電源オン/オフ機能を実現するソフトウェアを具備しないメインボードに対して、加工を必要とせずに、起動および停止の繰り返しを行う際の検査者の負担を軽減することができるようにする。

【解決手段】USB通信部130が、被検査コンピュータ300のシャットダウンを検出し、このシャットダウン検出に基づいて、スイッチ押アーム200が電源スイッチ359を押下する。これにより、電源オン/オフ機能を実現するソフトウェアを具備しないメインボード(処理部350)に対して、加工を必要とせずに、被検査コンピュータ300の起動および停止を自動で繰り返すことができるので、検査者の負担を軽減することができる。

(もっと読む)

試験アクセス・ポート・スイッチ

【課題】選択されていないTAPの電源がオンまたはオフされているかに関わらず、選択されたTAPへ情報を転送することができる電子システムを提供する。

【解決手段】電子システム10は、それぞれTAPスイッチ12に接続されたTAP20,22,24を有している。TAPスイッチ12は、例えば、命令に追加または事前追加されたコードのように、シリアル命令に含まれる選択コードに応答して、TAPのうちの選択された1つへクロック信号を提供するように構成された第1の回路40を備える。このTAPスイッチは更に、TAPスイッチによって受け取られたシリアル命令を、選択されたTAPへ渡すように構成された命令レジスタ(IR)を備える第2の回路38と、選択コードに応答して、選択されたTAPから受け取ったシリアル命令を、TAPスイッチの出力へと転送するように構成された第3の回路42とを備える。

(もっと読む)

半導体装置および半導体装置の動作試験方法

【課題】ROMに試験用プログラムを記憶させることができない場合にも初期動作の試験が可能な半導体装置の実現。

【解決手段】CPUコア11と、ROM13と、RAM14と、アドレス信号をデコードして、ROMまたはRAMの選択信号を発生するROM/RAM選択アドレスデコーダ15と、スタンバイ制御回路19と、RAM、ROM/RAM選択アドレスデコーダおよびスタンバイ制御回路の電源を、通常電源とバックアップ電源の間で切り替えるバックアップ電源切換機構と、を備え、スタンバイ制御回路は、スタンバイモードから通常動作状態に変化すると、CPUコアがROMの替わりにRAMをアクセスするように、ROM/RAM選択アドレスデコーダを設定可能であり、CPUコアがRAMに記憶された初期動作プログラムにしたがって起動動作を実行可能である。

(もっと読む)

半導体装置及びデータ処理方法

【課題】システムデバッグ時及び実機搭載時にオンチップの不揮発性記憶装置に対して所定権限のもとで保護の設定と解除が可能な半導体装置を提供する。

【解決手段】不揮発性記憶装置の遷移可能なセキュリティ状態として、不揮発性記憶装置に秘密情報がセットされていないとき不揮発性記憶装置の書き換えが許可され且つその記憶情報の読み出しが許可されるアンプロテクト状態(1)と、不揮発性記憶装置に秘密情報セットされているとき当該秘密情報を利用する認証結果が正当であることを条件に不揮発性記憶装置に対する書き換えが許可され且つその記憶情報の読み出しが許可されるプロテクトアンロック状態(2)と、不揮発性記憶装置に秘密情報セットされているとき当該秘密情報を利用する認証結果の正当性が確認されるまで不揮発性記憶装置に対する書き換えが禁止され且つその記憶情報の読み出しが所定の条件下で禁止されるプロテクトロック状態(3)を有する。

(もっと読む)

自己診断装置及び自己診断方法

【課題】自己診断において安全かつ信頼性、可用性及びコスト面を改善する。

【解決手段】一定周期内において予め設定されたアプリケーションによる処理を複数回実行し、実行された複数の処理結果を比較して自己診断を行う自己診断装置であって、ダイバース診断手法により設定された条件で前記アプリケーションを複数回実行する安全アプリ処理部と、前記安全アプリ処理部により得られる複数の処理結果を所定の退避領域に格納するメモリと、前記メモリに格納された複数の処理結果を比較し、比較した結果が一致しているか又は所定の誤差範囲にあるかに基づいてエラーの有無を判断する第1後処理部とを有することにより、上記課題を解決する。

(もっと読む)

処理システムおよび試験装置

【課題】複数の動作部が並列に命令データを処理する処理システムにおいて、各動作部が異常状態となった場合に、他の動作部への影響を排除する。

【解決手段】複数の動作部に対する命令データを受信して格納する共通バッファと、共通バッファが格納した命令データを順次読み出して、対応する動作部に順次振り分けて伝送し、且つ、いずれかの動作部へ命令データを伝送できず、共通バッファから当該命令データを削除できない場合に、当該動作部に代わって当該命令データに応じた処理を行い、共通バッファから当該命令データを削除する振分部とを備える処理システムを提供する。

(もっと読む)

仮想インフラストラクチャを用いた情報技術リスク管理

【課題】仮想インフラストラクチャを用いた情報技術リスク管理を提供する。

【解決手段】組織に対する情報技術リスクは、複数の仮想マシン(VM)103a、103bと関連しており、リスクオーケストレータ106は脅威表示メッセージ(TIM)を脅威インジケータ80、81から受信する。各TIMは、ホストが脆弱性を有する脅威の状態を表示する。脅威から生じるダウンタイム確率(DTP)および各ホストに対する全体のホストDTPが計算される。各VMに関しては、VMに関連するリスク値が、VMに対するホストDTPおよびVMに対する影響の関数として計算され、影響は組織にとってVMの相対的重要性を反映する値である。リスク軽減を必要とする各VMは、方針に従って識別され優先順位が付けられ、設定された軽減制御処置がリスク軽減を必要とする各VMに対して実行される可能性がある。

(もっと読む)

ディジタルシグナルプロセッサカードの自動試験装置

【課題】動作確認試験の作業効率を向上させ、生産性を向上させることが可能なDSPカード自動試験装置を提供すること。

【解決手段】DSP26用の動作試験プログラムがロードされる内部メモリ26−1を有するディジタルシグナルプロセッサ(DSP)26を複数備えたDSPカード12及び、DSP26用の動作試験プログラム及びホストCPU11用の動作試験プログラムがロードされるデータ領域を有するホストCPU11及び、試験用PC13とが相互に接続されたDSPカードの自動試験装置であって、試験用PC13からの指令により、ホストCPU11のデータ領域及び、DSP26の内部メモリ26−1に対して、それぞれ動作試験用プログラムを選択的にロードし、試験と判定を自動的に実行する。

(もっと読む)

プロセッサ試験装置、プロセッサ試験方法、プロセッサ試験プログラム

【課題】先行制御を中断せずに全ての条件コード設定命令の試験を行う。

【解決手段】プロセッサを試験するプロセッサ試験装置であって、プロセッサを試験するための試験命令列を1試験命令ずつ実行することで、試験命令列の条件コード設定命令で設定された条件コードを取得する条件コード取得機能部34aと、取得された条件コードと一致しない条件コードが出力されるという条件でエラー出力命令に分岐する条件分岐命令を生成し、試験命令列の条件コード設定命令の後に生成した条件分岐命令を加える条件分岐命令追加機能部36aと、プロセッサに、条件分岐命令を加えた試験命令列を先行制御方式で実行させる試験命令実行機能部37aと、を有するプロセッサ試験装置が提供される。

(もっと読む)

コンピュータ装置、メモリ診断方法、及びメモリ診断制御プログラム

【課題】複雑なメモリ診断プログラムであってもOS起動前にこれを正常に実行することができること。

【解決手段】メインメモリを有するコンピュータ装置であって、第1のメモリ診断プログラムを実行することにより、メインメモリの不良領域の特定を行う第1のメモリ診断手段と、再配置可能な第2のメモリ診断プログラムが記憶された記憶手段と、メインメモリのうち、第1のメモリ診断手段により特定された不良領域を除く領域に、記憶手段に記憶されている第2のメモリ診断プログラムを展開し、実行する第2のメモリ診断手段と、を有する。

(もっと読む)

コンピュータ装置、プロセッサ診断方法、及びプロセッサ診断制御プログラム

【課題】プロセッサの不良機能を確実に特定して、各種の診断テストの正常な実行を担保すること。

【解決手段】第1のプロセッサと、第2のプロセッサと、メインメモリとを有するコンピュータ装置であって、第2のプロセッサによりメモリ診断プログラムを実行させることにより、メインメモリを診断し、メインメモリ内の不良領域を特定するメモリ診断手段と、メインメモリのうち、メモリ診断手段により特定された不良領域を除く領域に、第1のプロセッサの有する複数の機能を診断するためのプロセッサ診断プログラムを展開する診断プログラム展開手段と、展開されたプロセッサ診断プログラムを第2のプロセッサにより実行させることにより、第1のプロセッサの有する複数の機能のうち、実行不能な機能である不良機能を特定する不良機能特定手段と、を有する。

(もっと読む)

プロセッサデバッグ装置

【課題】プロセッサのデバッグ効率を向上させること。

【解決手段】デバッグ機構233がシフトレジスタ234に過去6サイクル分のOPCODEを記憶し、スキャン部がシフトレジスタ234に記憶されたOPCODEをスキャンして読み出す。なお、デバッグ機構は、REQUEST_VALID信号を入力し、REQUEST_VALID信号の値が"1"であるときのみシフトレジスタにOPCODEを記憶するよう構成することもできる。また、複数の演算ユニットを有するプロセッサの場合には、デバッグ機構が複数の演算ユニットのOPCODEを記憶するよう構成することもできる。また、デバッグ機構がOPCODEまたはRUPT_CODEを選択して記憶するよう構成することもできる。

(もっと読む)

デバッグ装置およびデバッグ方法

【課題】デバッグの効率向上を図る。

【解決手段】インサーキット・エミュレータのCPUエバチップ140における手順違反検出部200は、CPU150のレジスタ群152および周辺エバチップ170のレジスタ群172に含まれる複数のレジスタに対して書込みの検出を行うと共に、検出したこれらのレジスタへの書込みの順番を監視し、該書込みの順番が予め規定された書込順に一致するか否かを検出する。表示装置133は、手順違反検出部200により不一致が検出されたときに、ユーザに警告を行う。

(もっと読む)

電子制御装置

【課題】CPU内部機能診断のために使用しているプログラム基本命令語に異常が発生した場合、CPU内部機能診断で異常が検知されないことがある。

【解決手段】CPU1と、このCPUの動作を監視するCPU監視装置2を備える電子制御装置において、CPU1には、CPUの内部機能の診断を行うCPU内部機能診断プログラムと、このCPU内部機能診断プログラム内でCPU内部機能診断のために使用しているプログラム基本命令語を診断する基本命令診断プログラムとを含み、基本命令診断プログラム実行後にCPU内部機能診断プログラムを実行することで、CPU内部の機能故障の有無を確実に診断する。

(もっと読む)

監視制御システム、監視制御方法、および監視制御プログラム

【課題】コンピュータシステム内に生じた誤動作を有効に検知し処理する。

【解決手段】コンピュータ1内のハードウェア装置104に接続され複数のコア処理手段101,102を有するマルチコアCPU100と、マルチコアCPU100に対してハードウェア装置104の動作制御を指示するBIOS部103とを備え、コア処理手段102が、ハードウェア装置104の起動動作時に当該ハードウェア装置の動作テストを行う初期動作診断機能を有し、コア処理手段101が、前記動作テストごとにハードウェア装置104における動作エラーをチェックし動作エラーが検知された場合に当該動作エラーに対するエラー処理を行う機能を備えた。

(もっと読む)

診断方法、電源制御装置、電子装置、電池パック、プログラム及び記憶媒体

【課題】本発明は、診断方法、電源制御装置、電子装置、電池パック、プログラム及び記憶媒体に関し、拡張スロットを設けることなく電子装置を診断可能とすることをも目的とする。

【解決手段】情報を格納するメモリを有する電池パックで動作可能な電子装置の診断方法において、前記電池パックから情報を読み出し、読み出した情報が診断モードを示すと前記電子装置を診断モードに設定するように構成する。

(もっと読む)

1 - 20 / 69

[ Back to top ]