Fターム[5B054BB05]の内容

Fターム[5B054BB05]に分類される特許

1 - 20 / 47

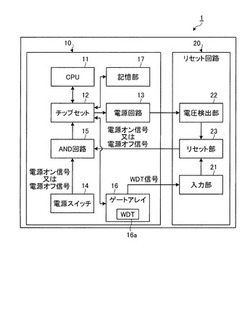

リセット回路および電子機器

【課題】リセット対象部を良好にリセットさせる。

【解決手段】実施形態のリセット回路および電子機器は、入力部と、リセット部と、を備える。前記入力部には、BIOSを実行する実行部を有するリセット対象部に設けられた異常検出部から出力された異常検出信号が入力される。前記リセット部は、前記入力部に前記異常検出信号が入力された場合、前記リセット対象部をリセットさせる。

(もっと読む)

電子機器

【課題】瞬断等による従来見られた不具合発生を防止する。

【解決手段】リセット端子を備えるメインICと、リセット端子に接続された追加回路とを備え、追加回路は、メインICへ供給される電源電圧を入力する第1入力端子と、メインICが稼働状態にあるときにメインICから出力される制御信号を入力する第2入力端子と、第2入力端子からの制御信号の入力があり且つ第1入力端子における電源電圧のレベルが上記所定レベルより高い所定のしきい値を下回ったときにオン状態となるスイッチ素子とを備え、スイッチ素子がオン状態となったときにリセット端子にリセット信号を与え、メインICは、リセット端子にリセット信号が与えられたときにリセット状態へ移行する。

(もっと読む)

端末装置並びにフリーズ検出方法及び端末装置の制御方法

【課題】細かい設定をすることなく、自動的にフリーズ状態を検出し、リセット処理等を行う端末装置の提供。

【解決手段】端末装置は、電源からCPUに供給される電流値を測定する電流測定部と、前記CPUをリセットするリセット制御部と、前記CPUと独立して動作し、動作モードに反した電流値の定常状態が観測された場合、前記リセット制御部に前記CPUをリセットさせる電流監視部と、を備える。

(もっと読む)

制御装置

【課題】複数のCPUコアを用いて構成される複数のシステムの中から異常状態のシステムを選択的にリセットするための技術を提供する。

【解決手段】マルチコアマイコン1の3つのCPUコア11〜13を用いて構成される3つのシステムの中から、異常状態のシステムが異常監視部40によって検出されると、異常状態のシステムを識別可能なリセット要求信号がリセット部50によって出力される。そして、3つのシステムで動的に共有される周辺機能部30は、周辺機能部30を利用しているシステムと、リセット要求信号に基づき識別される異常状態のシステムが一致することを条件としてリセットされる。このため、周辺機能部30が、正常なシステムによって利用されている状態においてリセットされないようにすることができる。

(もっと読む)

制御装置

【課題】複数のCPUコアを用いて構成される複数のシステムの中から異常状態のシステムを選択的にリセットするための技術を提供する。

【解決手段】マルチコアマイコン1の3つのCPUコア11〜13を用いて構成される3つのシステムの中から、異常状態のシステムが異常監視部40によって検出されると、異常状態のシステムを識別可能なリセット要求信号がリセット部50によって出力される。そして、3つのシステムで静的に共有されるメモリ20は、3つのシステムのそれぞれに割り当てられた3つの記憶領域21〜23のうち、リセット要求信号に基づき識別される異常状態のシステムに割り当てられた記憶領域がリセットされる。このため、正常なシステムによって利用されている記憶領域までリセットされないようにすることができる。

(もっと読む)

自動リセット回路、自動リセット方法、プログラム、自動リセット装置および情報端末

【課題】 MPUを用いることなく、ハードウェアリセットに依らなければ回復不可能な異常発生の際に、ハードウェアリセットを実施しシステムを回復する自動リセット回路を提供する。

【解決手段】 電源電圧確定回路5が、電源電圧確定信号14を出力し、リセット信号出力手段2が、タイマー1から出力されるタイマー信号11により起動してリセット信号10を出力し、リセット信号出力制御手段4が、コンピュータ起動時に、リセット信号出力手段2を制御し、ファームウェア6が、リセット信号出力制御手段4を稼働させ、タイマー1の初期化とタイマー設定を行いタイマー信号11を無効化し、割り込み検出回路7が、コンピュータ稼働中に、タイマー1の時間の経過により割り込み処理の実行を検出して出力した割り込みハンドラー起動信号13を受けて、割り込みハンドラー6が起動し、タイマー1の初期化とタイマー設定を行い、タイマー信号11を無効化する。

(もっと読む)

減電圧リセット回路及びこれを用いた電源装置

【課題】より確実に安定した減電圧監視を行うことが可能な減電圧リセット回路及び電源装置を提供する。

【解決手段】減電圧リセット回路15は、ドレインがリセット信号出力端子T5に接続されたNチャネル型の第1トランジスタ153と、ドレインがリセット信号出力端子T5に接続されたNチャネル型の第2トランジスタ154と、監視対象電圧V1の供給を受けて動作し、監視対象電圧V1が第1閾値電圧を下回っているときに第1トランジスタ153をオンさせる第1監視部151と、監視対象電圧V1とは異なる駆動電圧V0の供給を受けて動作し、監視対象電圧V1が第1閾値電圧よりも低く第1監視部151の下限動作電圧よりも高い第2閾値電圧を下回っているときに第2トランジスタ154をオンさせる第2監視部152と、を有する。

(もっと読む)

P−RUN信号出力装置、組込制御装置

【課題】組込ソフトウェアが異常動作したときは確実にリセット信号を出力し、組込ソフトウェアが正常動作している間はリセット信号を不要に発生させないようにすることのできる技術を提供することを目的とする。

【解決手段】本発明に係るP−RUN信号出力装置は、優先度の異なる複数の組込プログラムの実行状態を監視し、システムクロックが示す時刻と各組込プログラムの前回実行時刻との差分が所定閾値を超えている場合は、P−RUN信号を出力しない。また、P−RUN信号を出力するか否かを判断してP−RUN信号を出力する処理を、組込プログラムのなかで最も優先度の高いもの以上の優先度で実行する。

(もっと読む)

電子機器及びプログラム

【課題】ウォッチドックタイマのタイムアウトによる再起動が不用意に繰り返されてしまうことを防止することが可能な電子機器及びプログラムを提供する。

【解決手段】自己の装置の起動時に計時を開始する計時手段と、前記計時手段のカウント値が所定のタイムアウト値に到達するタイムアウト時に、自己の装置の再起動を行うリブート手段と、前記タイムアウト値よりも小さい一定の間隔毎に、前記計時手段のカウント値をリセットするカウント値リセット手段と、前記リブート手段により連続的に行われた再起動の回数を集計する集計手段と、前記集計手段による集計結果が所定の回数を上回った場合に、前記計時手段による計時を停止させた状態で起動を行う制御手段と、を備える。

(もっと読む)

情報処理装置、情報処理方法、及びプログラム

【課題】デバイスドライバの解析及びデバイスドライバの改竄を防止し、より高い安全性を確保することを目的とする。

【解決手段】第1のオペレーションシステム及び第2のオペレーションシステムを含むマルチOS環境下において、第2のオペレーションシステムが、第1のオペレーションシステムが使用するデバイスについて、デバイスの初期化を行うデバイス初期化部と、デバイスの利用状況を監視するデバイス監視部と、デバイスの異常を検知する異常検知部と、を有することによって課題を解決する。

(もっと読む)

ウォッチドックタイマ監視装置、ウォッチドックタイマ監視方法

【課題】CPUを個別に低電力モードにしても、CPUの異常を正確に検出できるマルチプロセッサシステムのウォッチドックタイマ監視装置及びウォッチドックタイマ監視方法を提供すること。

【解決手段】各CPUが個別に低電力モードに移行するマルチプロセッサシステムのウォッチドックタイマ監視装置100であって、各CPU毎に、プログラムが動作していることを示す動作状態情報を更新しながら記憶する動作状態記憶手段14と、動作状態記憶手段に動作状態情報が記憶されている場合、ウォッチドッグタイマ12をリセットするリセット手段13と、各CPU毎に、低電力モードであることを示す低電力モード状態情報を記憶するモード記憶手段15と、を有し、モード記憶手段に低電力モード状態情報が記憶されている場合、リセット手段は、動作状態記憶手段に動作状態情報が記憶されていなくても、ウォッチドッグタイマをリセットする、ことを特徴とする。

(もっと読む)

コンピュータシステム、及びコンピュータシステムの障害処理方法

【課題】OSが起動する前に拡張デバイスの初期化に要する時間を、短縮することのできる、障害復旧方法を提供する。

【解決手段】本体系装置と、複数の拡張デバイスと、前記本体系装置の動作を制御するサービスプロセッサと、を具備し、前記サービスプロセッサは、障害発生により前記本体系装置の電源が再投入されたときに、前記複数の拡張デバイスのうちでオペレーティングシステムの立ち上げに必要なデバイスである第1デバイス群のみを初期化し、前記第1デバイス群を初期化した後にオペレーティングシステムを起動させ、CPUは、オペレーティングシステムの起動後に、オペレーティングシステム上で障害処理を実行し、前記サービスプロセッサは、前記CPUによる障害処理の実行が開始された後に、前記複数の拡張デバイスのうちの前記第1デバイス群以外のデバイスである第2デバイス群を初期化する。

(もっと読む)

情報処理装置及び情報処理方法

【課題】エラー状態になった記憶装置を正常な状態に復帰させることができる情報処理装置及び情報処理方法を提供する。

【解決手段】液晶表示装置11は、メモリーカード20から画像ファイルの読み出し又は転送を行なう旨の制御指令を出力する画像再生制御装置13を備えている。この画像再生制御装置13は、制御指令が出力されてからの経過時間が予め設定された経過時間閾値以上になっても、制御指令に対する応答信号を出力しない、又は制御指令に対応した処理を完了しないエラー状態の記憶装置が検出された場合に、該エラー状態の記憶装置に対してリセット信号を出力する。

(もっと読む)

処理制御ユニット、処理実行ユニット、情報処理装置、制御方法、制御プログラム、および制御プログラムを記録したコンピュータ読み取り可能な記録媒体

【課題】メイン装置およびサブ装置を有する情報処理装置において、メイン装置での処理の実行状況に応じて、メイン装置が実行すべき処理を、サブ装置から制御する。

【解決手段】メイン表示装置210とは独立して動作可能なセンサ付きサブ表示装置230は、メイン表示装置210がメイン側BIOSプログラムP11を実行しながら生成したPOSTコードを取得するとともに、当該取得したPOSTコードが所定値であるか否かを判定するPOSTコード検査部24と、POSTコードが上記所定値であると判定された場合、メイン表示装置210において実行可能な複数のメイン側OSプログラムP21からP23のいずれか1つを実行するように指定するメイン側起動OS指定部25とを備える。

(もっと読む)

マイクロプロセッサ制御装置のための低電圧リセット判定及び動作フロー変更

リセット状態を識別する方法は、格納された値が特定の値と等しいかどうかを判定するステップと、格納された値が特定の値と等しくない場合に第1のモードを実行するステップと、格納された値が特定の値と等しい場合に第2のモードを実行するステップを有する。第2のモードは、格納された値を特定の値とは異なる値に設定するステップも含む。  (もっと読む)

(もっと読む)

コンピュータシステム、情報処理方法及びプログラム

【課題】POST中にコマンドのやりとりが不能になったときに、能動的にBIOSからBMCを再起動することにより、コンピュータシステムの動作に対する不具合を解消できるコンピュータシステムを提供する。

【解決手段】ファームウェアと、基板管理コントローラと、を有するコンピュータシステムであって、基板管理コントローラは、時間のカウントを行うとともに、ファームウェアからのコマンドを受けた場合にカウントをリセットするタイマ手段を備え、ファームウェアは、パワーオンセルフテスト中に、基板管理コントローラに対して、タイマ手段のカウントをリセットするためのコマンドを実行するコマンド実行手段と、基板管理コントローラからコマンドに対する応答が得られない場合、基板管理コントローラがストールしたと判断し、基板管理コントローラの再起動を指示する再起動指示手段と、を備える。

(もっと読む)

インターフェース制御装置

【課題】専用の制御プロセッサを用いることなく、不具合による初期化を実行するインターフェース制御装置を得る。

【解決手段】複数の情報管理モジュール14に対して指示する複数の情報処理端末12と一対一で接続されたインターフェース制御装置10のインターフェース部16は、不具合が発生、又はエラー信号を受信すると、情報処理端末12から送信されるリセット信号により不具合があるインターフェース部16のみ初期化される。インターフェース制御装置10は、モジュール14との情報の送受信を実行する第2送受信部26と、インターフェース部16と第2送受信部26との間にセレクタ制御部24とを備え、セレクタ制御部24は、情報処理端末12と情報管理モジュール14との情報を制御すると共に、第2送受信部26で受信される不具合情報に基づいて最先のリセット信号により第2送受信部26に対して初期化処理を実行する。

(もっと読む)

複合装置

【課題】例えばプリンタとスキャナーとを有する複合装置において、スキャナーの暴走が検出されたとき、これを制御するマイクロプロセッサにリセット信号を送ってリセットして初期化させることになるが、この場合、スキャナー全体が初期化されることになるため、例えばスキャン処理中であった場合には、最初から同じ処理を繰り返すことになって、非効率的になるという問題があった。

【解決手段】スキャナー101の異常を検出する検出部118と、異常に対する復旧情報を生成する復旧情報生成部120と、この復旧情報を表示する表示部と復旧情報に基づいた復旧指示を入力する入力部とを有するオペレーションパネル123と、入力された復旧指示に従って、スキャナー101の復旧処理を行う復旧処理部121とを備え、スキャナー101の一部をリセットすることで処理の継続を可能とする。

(もっと読む)

電気機器

【課題】 大容量のメモリが搭載されている場合でも、データの退避処理に要する十分な時間を確保することができ、これにより大事なデータの消失を未然に防ぐことができて信頼性の向上が図れる電気機器を提供する。

【解決手段】 バッテリ31を有する補助電源回路30をデータの退避処理のための動作用電源として採用する。

(もっと読む)

監視回路、電子制御装置、及び監視回路の制御方法

【課題】暴走しているにもかかわらずスリープ信号を出力した演算処理回路を適確にリセットする。

【解決手段】演算処理装置の監視回路において、演算処理回路に電源電圧を供給し、前記電源電圧レベルに応じて電源電流を制御する電源電圧制御部と、前記演算処理回路からスリープ信号が入力されたときに、前記電源電圧制御部の電源電流を低下させる判定部と、前記電源電圧制御部の電源電圧が所定レベルを下回ったときに、前記演算処理回路にリセット信号を出力する減電圧検知部とを有する。演算処理回路が暴走しているときは消費電流が大きく前記電源電圧制御部の電源電圧の降下が大きいので、減電圧検知部は、供給される電力の電圧レベルが所定レベルを下回ったときに、リセット信号を出力する。よって、演算処理回路をリセットでき、正常な動作を回復させることができる。

(もっと読む)

1 - 20 / 47

[ Back to top ]