Fターム[5B060CD11]の内容

Fターム[5B060CD11]の下位に属するFターム

アクセス優先制御 (161)

ビジー制御、ビジー判定 (28)

占有制御、排他制御 (52)

デッドロック回避(防止、解除) (4)

Fターム[5B060CD11]に分類される特許

1 - 20 / 80

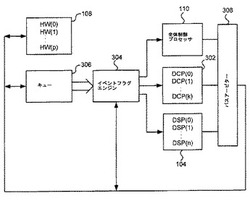

デジタル信号処理のデータ転送

【課題】デジタル信号処理システムにおいてデータを転送する技術を提供する。

【解決手段】一例では、デジタル信号処理システムは、メモリアクセスコントローラにそれぞれ接続され、メモリデバイスからデータを読み取り、データにおいて1つ以上の動作を実行し、データをメモリデバイスに書き込むようにそれぞれ構成された複数のハードウェア周辺装置を有する。ハードウェア周辺装置を共に配線結合することを回避するため、且つ、構成可能なデジタル信号処理システムを提供するため、マルチスレッドのプロセッサは、ハードウェア周辺装置とメモリとの間のデータの転送を制御する。各プロセッサのスレッドは、メモリアクセスチャネルに割り当てられ、スレッドは、イベントの発生を検出し、これに応じて、選択されたハードウェア周辺装置がそのメモリアクセスチャネルを介してメモリデバイスからデータを読み取ること又はメモリデバイスにデータを書き込むことを可能にするように、メモリアクセスコントローラを制御するように構成される。

(もっと読む)

RAM記憶装置

【課題】RAMへのアクセス競合が発生した場合であっても、両アクセスを有効なものとして応答可能なRAM記憶装置を提供する。

【解決手段】

制御信号に応じてクロック信号による1のサイクル内において2つのインターフェースのうちの一方に到来したアクセスをRAMに供給する選択部と、当該制御信号に応じて当該インターフェースのうちの他方に到来したアクセスを少なくとも当該1のサイクルに続く次のサイクルまで記憶する記憶部と、を含み、当該選択部は、当該次のサイクル以降において当該記憶部に記憶されているアクセスを当該RAMに供給する。

(もっと読む)

メモリ仲裁回路網

【課題】第1および第2のポートを有するデュアルポートメモリを提供する。

【解決手段】デュアルポートメモリは、単一ポートメモリ要素のアレイ22と、アレイに連結されており、かつアレイからデータを読み取り、アレイにデータを書き込むように動作可能である制御回路30と、第1のポートから第1のメモリアクセス要求を受信するように動作可能な第1の要求生成器60−Aと、第2のポートから第2のメモリアクセス要求を受信するように動作可能な第2の要求生成器60−Bと、制御回路、並びに第1および第2の要求生成器に連結されている仲裁回路64とを含み、仲裁回路は、同期モードで動作可能であり、同期モードにおいて、第1および第2の要求生成器は、等しい周波数を有する少なくとも2つのクロック信号を用いて制御される。

(もっと読む)

メモリ制御装置、集積回路、情報処理装置およびメモリ制御方法

【課題】信号線やチップのピン数等の増加を抑制して必要なメモリ帯域を確保する。

【解決手段】複数のメモリには、メモリ毎に独立してデータバスが接続される。また、複数のメモリには、メモリ毎に独立して選択信号線が接続される。コマンド信号線は、複数のメモリの間で共有して接続される。制御部は、複数のメモリのうちの少なくとも2つのメモリに対するバスマスタからのアクセス要求が出力された場合に、当該アクセス要求に応じたコマンドがコマンド信号線において重複して発行されないようにコマンド制御を行う。

(もっと読む)

データ転送制御装置、データ転送システム及びデータ転送方法

【課題】実行中のDMA転送の転送速度要求を満たしつつ、DMA転送とアクセス先が競合するマスタのアクセスを実行可能にする。

【解決手段】本発明に係るデータ転送制御装置110は、CPU101及び第1のDMAC102からの要求に従い、第1の記憶装置107へアクセスする第1のIF105と、第1のDMAC102からの要求に従い、第2の記憶装置108へアクセスする第2のIF106と、第2のIF106が第2の記憶装置108にアクセスを開始してからの経過時間をカウントするカウンタ109とを備える。第1のIF105は、連続転送動作中に、CPU101から第1の記憶装置107へのアクセス要求を受けた場合において、経過時間が基準値以下の場合、CPU101から第1の記憶装置107へのアクセスを許可する。

(もっと読む)

電子機器、及び画像処理装置

【課題】ページミスを発生させるアクセス要求よりも他のアクセス要求を優先させて、レイテンシーを低減させる。

【解決手段】調停回路は、アクセス要求を受け付けた場合、当該アクセス要求が、当該アクセス要求よりも前にメモリーコントローラーに出力した他のアクセス要求であって処理が終了していないアクセス要求と、ページミスを発生させないかどうかを判定する。当該アクセス要求がページミスを発生させる場合は、当該アクセス要求の出力を所定期間停止させ、その後のページミスを発生させないアクセス要求を、優先的に出力する。

(もっと読む)

情報処理装置

【課題】第1のチップで処理されたデータがバス及び第2のチップを経由してDRAMに転送される場合に、第1のチップで処理されたデータと第2のチップで処理されたデータとのアクセス競合を防止する。

【解決手段】デコーダ53は第1のチップ7で調停されてバス15及び第2のチップ9を経由してDRAM11に転送されるデータに対して、第2のチップ9上の配線61,63,65の中でそのデータに割り当てられている優先度に対応する配線を選択する。第2の調停部(調停部33c〜33g)は第1のチップ7で処理されたデータ及び第2のチップ9で処理されたデータの中で、同じ優先度が割り当てられているデータどうしのアクセスが競合すれば調停をし、かつ、異なる優先度が割り当てられているデータどうしのアクセスが競合すれば調停をする。

(もっと読む)

組込み型チャネル選択を備えるマルチチャネルメモリ

【課題】マルチチャネルメモリデバイス、及び、マルチチャネルデバイスの1つ又は複数のチャネルを選択する方法を提供する。

【解決手段】メモリデバイスに組み込まれたスイッチインターフェース(SI)レジスタ147は、複数のインターフェースの特権レベルを管理する。SIレジスタ147は、インターフェースに帰する特権レベルに関係なく、複数のインターフェースを介してアクセス可能であってもよい。ステータスレジスタ149はステートマシーンビジービットを含み、デュアルチャネルメモリにおいて、どちらかのインターフェースは、ステータスレジスタ149をいつでも読み出してもよく、一方では、メモリアレイ143にアクセスする比較的高い特権レベルを有するインターフェースのみが、ステータスレジスタ149に書き込んでもよい。

(もっと読む)

トラフィッククラスと関連するポートをもつマルチポートのメモリコントローラ

【課題】メモリコントローラは、QoSパラメータに対する強調を少なくさせるとともに、メモリコントローラパイプラインを通じてオペレーションが流れるのでメモリバンド幅の最適化に対する強調を増加させる。

【解決手段】一実施例においてメモリコントローラはマルチポートを含む。各ポートは異なるタイプのトラフィック専用である。一実施例においてサービスの質(QoS)パラメータがトラフィックタイプのために定義され、各トラフィックタイプは異なるQoSパラメータ定義を有する。メモリコントローラは、QoSパラメータに基づき異なるポートで受信したオペレーションをスケジューリングするよう構成される。一実施例において、サイドバンド要求を介して及び/又はオペレーションのエイジングを介してより高いQoSパラメータを有するその後のオペレーションが受信されるとき、メモリコントローラはQoSパラメータのアップグレードをサポートする。

(もっと読む)

マシンビジョン用マルチプロセッサシステムオンチップ

【課題】メインメモリに記憶されるデータを使用するソフトウェアを実行するように設定された、多重のプロセシングコアを含むマルチプロセッサシステムにおける共用資源の効率的使用のための方法及びシステムを提供する。

【解決手段】マルチプロセッサシステム10は、プロセッサコア200と外部メモリ500間を接続し、多重のプロセッサコア200による使用のため、データを外部メモリ500から事前に取得するように設定された、データストリーミングユニット2000を含む。マルチプロセッサシステム10は、プロセッサコア200に接続し、そして、多重のプロセッサコア200のために、2つ以上のプロセッサコア200に同時に1つの所与のデータアイテムにアクセスさせる、ソフトウェアの選択された部分を実行するように設定される、スクラッチパッドプロセスユニット1000を含む。

(もっと読む)

信号制御装置及び信号制御方法

【課題】2つのCPUがデュアルポートRAMに同じタイミングで読出し又は書込みを行う場合に、データ信号を正しく読出すこと。

【解決手段】信号制御装置4は、第1及び第2のCPUがデュアルポートRAM5に書き込むアドレスの衝突を検出するアドレス衝突検出部14を備える。また、アドレスの衝突が検出された場合に、デュアルポートRAM5に書込みを行う第1又は第2のCPUのいずれかに設けられたバッファメモリに、衝突したアドレスから読出したデータ信号を保存する制御を行う制御部13を備える。また、第1及び第2のCPUの読出し可能状態又は書込み可能状態に応じて、データ信号の読出し元であるレジスタ又はバッファメモリを切替えて、読出し可能状態となるCPUに読出した前記データ信号を出力するマルチプレクサ15a,15bを備える。

(もっと読む)

アクセス管理装置、情報処理装置、アクセス管理方法

【課題】複数のプロセッサが共有リソースにアクセスする際の調停頻度を、キャッシュやバッファを抑制するアクセス管理装置、情報処理装置及びアクセス管理方法を提供すること。

【解決手段】複数のプロセッサ11から要求された共通のリソース16へのアクセス要求を制御するアクセス管理装置100であって、複数のプロセッサ11から受け付けたリードアクセスの複数のアドレスを比較するアドレス比較手段13と、複数のアドレスのうち一致したアドレスのデータをリソース16からリードするデータリード手段14と、データリード手段14がリードしたデータを、一致した複数のアドレスを出力した複数のプロセッサ11に同じタイミングで出力するデータ出力手段15と、を有することを特徴とする。

(もっと読む)

メモリチップおよびメモリシステム

【課題】複数のポートを備え、各ポートからの同時アクセスを行うこと。

【解決手段】複数の単位領域に分割され、前記複数の単位領域は夫々個別にアクセスを受ける不揮発性のメモリセルアレイ10と、アクセスコマンドの入力を夫々受け付ける複数のポートと、アクセスコマンドに基づいて前記メモリセルアレイに夫々個別にアクセスするポート毎に備えられる複数の処理系11と、複数の処理系11の夫々が受け付けたアクセスコマンドに含まれるアクセス先アドレスを相互に比較することによってアクセス先の単位領域が複数の処理系11間で競合しているか否かを判定する競合判定を実行する競合判定部12と、を備え、複数の処理系11の夫々は、競合判定部12による競合判定結果が競合ありであるとき、アクセスの開始を待機し、競合判定結果が競合なしであるとき、アクセスを開始する。

(もっと読む)

半導体記憶装置

【課題】ホストからのデータの書き込みの要求に対する応答速度を著しく低下させることなく、追記方式におけるガベージコレクションを行うことが可能な半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、追記方式によって、ホストから論理アドレスが指定されたデータの書き込みの要求に応じて、半導体記憶チップに対してデータの書き込みを行ない、コンパクションにより、半導体記憶チップに対して有効データの書き込みを行なう。半導体記憶装置は、ホストからの要求に応じた書き込みの頻度とコンパクションにおける書き込みの頻度とを、予め設定された割合に応じて調整する。

(もっと読む)

電子機器、及びメモリー制御方法

【課題】優先順位が上位のモジュールの連続するメモリーアクセスの間に、優先順位が

下位のモジュールのメモリーアクセスが可能な優先制御方式において、上位のモジュール

の処理をより高速化する。

【解決手段】電子機器は、メモリーと、メモリーへのアクセス要求を1回受け付けた場

合に、当該アクセス要求のアクセス要求元の優先順位を最下位に設定し、次に受け付ける

アクセス要求を選択する優先制御により、メモリーへのアクセスを行うメモリー制御回路

と、メモリー制御回路のポートに接続され、アクセス要求を送る複数のモジュールと、を

備える。ここで、複数のモジュールのうち少なくとも1つの第1モジュールは、メモリー

制御回路の2つのポートに接続され、他のモジュールはそれぞれ1つのポートに接続され

ている。

(もっと読む)

メモリアクセス処理装置及び方法

【課題】メモリアクセス装置の各ポートのキャッシュ装置とメモリとの間で、各ポートの命令のリクエストの調停を行うメモリアクセス処理装置で、調停が混雑している場合に、メモリアクセスを最適化して、メモリアクセス効率を向上できるようにする。

【解決手段】調停制御部4は混雑判定部8を有し、混雑判定部8により調停の混雑が判定される。命令発行制御装置3a〜3dでは、調停が混雑している場合には、ストア命令をバッファに退避させ、ロード命令がストア命令を追い越すように制御している。このように、調停が混雑している場合には、ロード命令をストア命令に優先させるように、命令のリクエストの出力順を変更することで、メモリアクセスの最適化を図ることができる。

(もっと読む)

メモリ要求スケジューリングのアプリケーション選択

本開示は、一般に、メモリベースのスケジューリングを用いて、コンピュータシステムを動作させるためのシステム、方法、およびデバイスを説明する。このコンピュータシステムは、アプリケーションプログラム、およびメモリバンクと通信しているメモリコントローラのうちの1つまたは複数を含むことが可能である。このメモリコントローラは、要求をスケジューリングするためのスケジューラを含むことが可能である。このアプリケーションプログラムは、複数のスケジューリングアルゴリズムから、要求をスケジューリングするためのスケジューリングアルゴリズムを選択することが可能である。このアプリケーションプログラムは、選択されたスケジューリングアルゴリズムを使用して、要求をスケジューリングするようにスケジューラに命令することが可能である。  (もっと読む)

(もっと読む)

デュアルポートメモリのアクセス方法及びアクセス制御装置

【課題】デュアルポートメモリのディジタルデータ領域に対する高速アクセスと、アナログデータ領域に対するアクセスとを両立させ、大容量のメモリを不要としてコストの低減を可能にする。

【解決手段】ディジタルデータ領域とアナログデータ領域とを備えたデュアルポートメモリのアクセス方法であって、ディジタルデータ領域に、第1の通信装置としてのマスタ通信装置30が一定周期でアクセスしてディジタルデータを更新可能としたデュアルポートメモリ20のアクセス方法において、第2の通信装置としてのユーザI/F10からメモリ20にアクセス権取得のコマンドを送信した際にマスタ通信装置30がアクセスしていない限りユーザI/F10によるアナログデータ領域へのアクセスを許可すると共に、ユーザI/F10からメモリ20にアクセス権放棄のコマンドを送信してマスタ通信装置30によるアナログデータ領域へのアクセスを可能にした。

(もっと読む)

画像処理装置

【課題】マルチバンクアクセスをより多く発生させて、メモリーアクセス効率を向上させる。

【解決手段】メモリーコントローラー133は、マスター(1〜M)からのSDRAM140へのアクセス要求を受け付け、当該アクセス要求に含まれるアドレスを構成するビットのうち、予め設定されたビット位置のビットが示すバンクアドレスに対応するバンクにアクセスするアクセス手段を有する。また、上記のビット位置を再設定する設定手段を有する。また、設定手段により上記のビット位置を変更し、変更後の各変更ビット位置において、バンクごとに、アクセス手段によりアクセスされたアクセス頻度を記録する統計手段を有する。ここで、設定手段は、各バンクに対するアクセス頻度に基づいて1つの変更ビット位置を選択し、ビット位置として再設定する。

(もっと読む)

画像処理装置

【課題】複数のプロセッサを有する画像処理装置において、各プロセッサのプログラム実行に必要なメモリ容量を削減することのできる画像処理装置を提供する。

【解決手段】ROMローダ2はCPUコア4A、4Bの実行用プログラムをプログラムROM1から読み出してデュアルポートメモリ3A、3Bに格納し、CPUコア4A、4Bは、デュアルポートメモリ3A、3Bに格納されたプログラムを実行する。描画エンジン6はプログラムROM1に格納された画像データを直接読み出して伸張処理を行う。

(もっと読む)

1 - 20 / 80

[ Back to top ]