Fターム[5B060MM07]の内容

メモリシステム (7,345) | メモリモジュール構成、管理技術 (856) | メモリモジュールの実装制御 (117) | 種別検知 (71)

Fターム[5B060MM07]に分類される特許

1 - 20 / 71

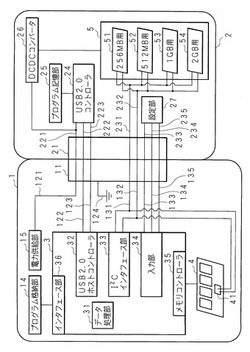

メモリモジュール検査システム、情報処理装置及び記憶装置

【課題】情報処理装置に装着された状態のメモリモジュールを検査できるメモリモジュール検査システム、情報処理装置、及びメモリモジュールの検査に必要なデータを記憶する記憶装置を提供する。

【解決手段】記憶装置2は、情報処理装置1で使用されるメモリモジュール4の正しい仕様を示す仕様データを仕様データ記憶部5で記憶している。情報処理装置1は、仕様データ記憶部5から仕様データを読み出し、メモリモジュール4のSPDメモリ(不揮発性メモリ)41に記憶している仕様データが正しいか否かを判定し、正しくない場合はSPDメモリ41の記憶内容を書き換える。また、記憶装置2のプログラム記憶部25は、メモリモジュール4の検査に必要なプログラムを記憶しており、情報処理装置1は、プログラム記憶部25からダウンロードしたプログラムに従ってメモリモジュール4の検査の処理を実行する。

(もっと読む)

半導体装置

【課題】チップ間の貫通電極(TSV)の数を増やすことなく、任意の数のチップに対して識別番号を割り付ける。

【解決手段】本発明による半導体装置は、積層された複数のチップを備えた半導体装置であって、前記複数のチップのうちの一つのチップが、所定の信号に基づきパルス信号を発生させて隣接チップに供給するパルス発生部(1100)を備え、前記複数のチップのうち、前記一つのチップを除く各チップが、一方の隣接チップからパルス信号が供給され、該パルス信号のパルスの数を変更して他方の隣接チップに供給するパルス変更部(2200)と、前記パルス信号のパルスの数に応じてチップの識別番号を表す識別信号を発生する識別信号発生部(2100)を備える。

(もっと読む)

メモリシステム、メモリ制御方法及びメモリ制御プログラム

【課題】本発明は、JEDEC準拠とJEDEC非準拠の双方のDIMMのメモリ制御を適切に行う。

【解決手段】メモリシステム1は、DIMMコネクタ4に着脱可能に装着されているDIMM10がJEDEC準拠DIMMとJEDEC非準拠DIMMのいずれであるかのDIMMの種別をメモリコントローラ3が判別し、メモリコントローラ3が、該DIMM10に搭載され該DIMM10の構成情報及び搭載メモリチップの情報等を格納するSPDに格納されている情報を読み取って、該SPDの情報及び該DIMM種別判別の判別結果に基づいて該DIMM10のアクセス制御を行う。

(もっと読む)

半導体装置

【課題】積層型の半導体装置においてコアチップの選択動作に必要な回路の規模を縮小する。

【解決手段】それぞれ固有のチップアドレスSID(CORE)を保持するコアチップCC0〜CC7と、これらを制御するインターフェースチップIFとを備える。インターフェースチップIFは、モード信号MODEに応じてアドレス信号及びチップ選択信号からチップ選択アドレスSID(IF)を生成するチップ選択アドレス生成回路42を備える。コアチップCC0〜CC7は、チップ選択アドレスSID(IF)とチップアドレスSID(CORE)とを比較し、両者が一致した場合にコマンドを通過させる比較回路63/64を備える。本発明によれば、動作モードによって変化するチップ選択アドレスSID(IF)をインターフェースチップIF側で生成していることから、全体として回路規模を縮小することが可能となる。

(もっと読む)

半導体集積回路及び書込処理方法

【課題】複数種類の外部不揮発性記憶装置に対して、それぞれに適した書込パラメータを自動選択することにより、書込処理が可能な半導体集積回路を提供すること。

【解決手段】複数種類の外部不揮発性記憶装置のそれぞれに対して書込処理を行なうための複数種類の書込パラメータが格納された内部不揮発性記憶回路102と、接続された外部不揮発性記憶装置200の識別情報を取得し、識別情報に基づいて複数種類の書込パラメータから接続された外部不揮発性記憶装置200に適した1つの書込パラメータを選択し、選択された書込パラメータを用いて接続された外部不揮発性記憶装置200に対して書込処理を行なう制御回路101と、を備えた半導体集積回路100。

(もっと読む)

コンピュータシステム、メモリ初期化方法、及びプログラム

【課題】メモリ初期化処理の更なる高速化を実現可能なコンピュータシステムを提供する。

【解決手段】仕様情報を含む第1のSPD情報を格納する複数のメモリモジュールと、システム内のメモリアクセスに用いられるアクセス設定値と、第1のSPD情報の複製である第2のSPD情報とを記憶する不揮発性メモリとを備える。読み出し制御部は、メモリ初期化処理において、第1のSPD情報と第2のSPD情報とが一致するか否か判定して、一致しない不一致メモリモジュールを特定すると、不一致メモリモジュールの第1のSPD情報を読み出して不揮発性メモリへ第2のSPD情報として書き込む。設定値生成部は、不一致メモリモジュールが存在する場合に、不一致メモリモジュールの第2のSPD情報が生成に用いられるアクセス設定値を、第2のSPD情報に基づいて生成して、不揮発性メモリへ書き込む。

(もっと読む)

半導体メモリ装置

【課題】アクセス装置が半導体メモリ装置の特性を意識することなく、最適なファイルアクセスを行うこと。

【解決手段】本発明に関わる半導体メモリ装置は、半導体メモリ装置の特性に関する情報を格納する装置情報格納部と、その情報を基に半導体メモリ装置の特性に適したファイルアクセスを行うインターフェース制御部を半導体メモリ装置内に備えることにより、アクセス装置が半導体メモリ装置の特性を意識することなく、最適なファイルアクセスを実現することができる。このような半導体メモリ装置は、デジタルAV機器や携帯電話端末、PC等の情報記録媒体として利用することができる。また、半導体メモリ装置の特性に応じた最適なファイルアクセスを実現するため、転送レートの高い高品質AVデータを記録する機器の情報記録媒体として利用する場合は特に好適に機能する。

(もっと読む)

DIMMにおける相変化メモリ

【課題】相変化メモリ(PCM)モジュールを有するデュアルインラインメモリモジュール(DIMM)メモリデバイスの管理を提供する。

【解決手段】BIOSは、PCMモジュール識別(ID)を読み出して、PCMモジュール構成に応答するための、実行可能コードを有することができる。PCMモジュールは、DIMMが行アドレスを受信した直後に、メモリコントローラによって生成される列アドレスをDIMMへ供給することを可能にするアディティブレイテンシと関連することができる。DRAMキャッシュメモリのようなメモリデバイスを用いて、PCMDIMMの特定のアドレスに対応する書き込みデータをキャッシュに格納することができる。

(もっと読む)

マスタ基板作成装置及び記録媒体

【課題】パソコンに保存されたSPDデータをパソコンに接続できない検査装置に保存する作業を短時間で簡単に行い、DIMM等の基板検査の作業効率を向上させることができる低コストで構築可能な検査システムを提供する。

【解決手段】パソコン1に接続されたマスタ基板作成装置10を用いて該パソコン内のSPDデータをそのEEPROMに記録したマスタ基板2を作成し、該マスタ基板を検査装置のソケットに装着して該マスタ基板から該SPDデータをダウンロードする。上記マスタ基板作成装置は、パソコンと接続するセントロコネクタ11と、DIMMを装着可能な2つのソケット13a,13bと、該セントロコネクタを介して入力されたSPDデータを該ソケットに装着されたDIMM上のEEPROMに書き込む書込制御部が設けられている。

(もっと読む)

メモリデバイスおよびメモリデバイス制御装置

【課題】従来のインタフェースの機器との接続互換性を保ちつつ、データ転送速度を向上できるメモリデバイスおよびメモリデバイス制御装置を提供する。

【解決手段】メモリデバイス103とホスト装置101の間に介在するメモリデバイス制御装置102は、クロック信号に同期してメモリデバイスとの間でデータを転送するデータ転送手段123を備える。データ転送手段123は、クロック信号の立ち上がりエッジ及び立下りエッジの一方に同期してデータを転送するシングルエッジ同期モード、または、立ち上がりエッジと立下りエッジとの双方に同期してデータを転送するダブルエッジ同期モードに対応する。メモリデバイス103がバスマスタとして動作してデータ転送を行う際、データ転送手段123はメモリデバイスに対してダブルエッジ同期モードでデータ転送を行う。

(もっと読む)

メモリコントローラ、不揮発性記憶装置、不揮発性記憶システムおよびプログラム

【課題】不揮発性メモリの種類により決定される要因を考慮して、タイムアウト規定を守ることができる不揮発性記憶システムを提供する。

【解決手段】不揮発性記憶システム100では、不揮発性メモリ制御部214が、タイムアウト監視部213から出力される集約処理停止信号に基づいて、集約処理を中断させ、タイムアウトの発生を確実に防止することができる。その結果、不揮発性記憶システム100では、タイムアウト値(タイムアウト規定)を厳密に守ることができる。

(もっと読む)

情報処理装置

【課題】スレーブデバイスのアドレスビット長に依存せずにブートアップ処理を行うことができる情報処理装置を提供する。

【解決手段】情報処理装置は、アドレスの各ビットをシリアルに送信し、データの各ビットをシリアルに受信するシリアルインターフェースと、起動プログラムを格納するブートメモリと、起動時に起動プログラムを実行して起動時処理を行なう制御回路とを含み、制御回路は、起動時処理において、第1のタイミングを開始タイミングとしてシリアルインターフェースがシリアルに受信するデータが所定のデータに一致するか否かを判断し、データ不一致の場合には、第2のタイミングを開始タイミングとしてシリアルインターフェースがシリアルに受信するデータが所定のデータに一致するか否かを判断することを特徴とする。

(もっと読む)

情報処理装置,記憶制御装置及び制御方法

【課題】 システムボードに搭載された複数のメモリモジュールのSPDの設定情報を一致させる。

【解決手段】 メモリの設定情報を格納するSPD12を備える複数のメモリモジュール10A,10Bを備えるコンピュータ1において,メモリ・コントローラ2のSPDコントローラ20の設定情報取得部21は,メモリモジュール10A,10BのSPD12A,12Bから設定情報SPD_A,SPD_Bを取得し,設定情報保持部24に保持する。設定情報比較部22は,設定情報SPD_A,SPD_Bを比較し,設定情報の内容が異なる場合に,設定情報書き換え部23は,これらの設定情報のうちいずれか一の内容(SPD_A)を用いて,メモリモジュール10BのSPD1Bの設定情報(SPD_B)を上書きする。

(もっと読む)

電子機器

【課題】波形品質の確保と消費電力の低減とを両立する電子機器を提供することを目的とする。

【解決手段】データ信号線11に終端抵抗7が接続された回路構成を有する電子機器1であって、データ処理手段2と、データ処理手段2の主記憶装置となる1つ以上のデータ記憶手段3と、データ処理手段2とデータ記憶手段3とを接続するデータ信号線11に終端抵抗7を介して終端電圧を印加する終端電圧生成手段6と、データ信号線11と終端抵抗7との間に接続される通電遮断手段8と、を有し、データ処理手段2はデータ記憶手段3の構成を検知し、その検知結果に基づいて、通電遮断手段8によりデータ信号線11と終端抵抗7との間を通電させて終端抵抗7を有効にし、又はデータ信号線11と終端抵抗7との間を遮断して終端抵抗7を無効にすることにより上記課題を解決する。

(もっと読む)

記録制御装置、記録制御方法、記録制御プログラムおよび記憶媒体

【課題】NVRAMを正規の位置と異なる位置に誤実装した際に、データの保障を行う記録制御装置、記録制御方法および記録制御プログラムを提供することを目的とする。

【解決手段】各データ内にデバイス識別情報(ID)を有する、脱着可能な不揮発性メモリのNVRAM1、2と、各IDと各NVRAMがRAM内で使用するメモリ領域との対応付けを記憶保持する、IDテーブルを備えたFlashROMとを有し、IDとIDテーブルとを参照することにより、NVRAM1、2の実装位置の正誤判断を行う。

(もっと読む)

電子機器およびその制御方法

【課題】SPDを必要に応じて実装することができる電子機器およびその制御方法を提供する。

【解決手段】メモリ素子実装領域部17にSPDが実装されている場合は、SPDから読み出したDRAMアクセスパラメータをメモリコントローラ12に設定し、メモリ素子実装領域部17にSPDが実装されていない場合は、BIOS18から読み出したデフォルトのDRAMアクセスパラメータをメモリコントローラ12に設定する。

(もっと読む)

半導体集積回路装置

【課題】異なる仕様の不揮発性半導体メモリであっても接続を可能にする。

【解決手段】DDR−SDRAM/DDR2−SDRAMが接続された場合、半導体集積回路装置には、レベル判定用の基準電圧VREFが入力される。I/Oバッファ制御回路8は、基準電圧VREFを検出し、Lo信号のバッファ制御信号CBを出力する。出力バッファ9は、DDR−SDRAM/DDR2−SDRAMに対応する駆動能力となる。また、セレクタ回路13は、入力バッファ12の出力信号を選択して出力するように接続先を切り替える。Mobile DDR−SDRAMが接続されると、基準電圧VREFが入力されないので、I/Oバッファ制御回路8は、Hi信号のバッファ制御信号CBを出力する。出力バッファ9は、該SDRAMに対する駆動の力となり、セレクタ回路13は、入力バッファ11の出力信号を選択して出力するように接続先の切り替えを行う。

(もっと読む)

データスワップ制御装置

【課題】 パラレルインターフェースでのデータの配置が互いに異なる複数の種類のフォントメモリからのフォントデータをそれぞれ使用可能にすることができるデータスワップ制御装置を提供する。

【解決手段】 デバイスID判定回路26は、データスワップ回路25によって配置入替処理が実行された入替IDが、デバイスID格納テーブル23に格納される登録IDに一致するか否かを判定する。データスワップ制御回路27は、デバイスID判定回路26によって一致しないと判定されるとき、配置入替処理の種類を変更するようにデータスワップ回路25を制御し、デバイスID判定回路26によって一致すると判定されるとき、外部ID制御回路21によって読み出されたフォントデータに対して、そのときの配置入替処理を実行するようにデータスワップ回路25を制御する。

(もっと読む)

印刷記録材容器の識別システムおよび識別方法

【課題】 識別情報の格納に必要なデータ容量を増大させることなく、識別可能な記憶装置の数を増大させること。

【解決手段】記憶装置21〜28に対するデータの書き込み、および記憶装置21〜28からのデータの読み出しを制御する制御回路30は、クロック信号線CL、リセット信号線RLを介してクロック信号SCK、及びリセット信号RSTを各記憶装置21〜28に送出する。制御回路30から送出されるデータ列のうち、第1グループを構成する記憶装置21、23、25、27に対するデータ列である第1データSDA1は、第1データ信号線DL1を介して第1グループを構成する記憶装置21、23、25、27に供給される。データ列のうち、第2グループを構成する記憶装置22、24、26、28に対するデータ列である第2データSDA2は、第2データ信号線DL2を介して第2グループを構成する記憶装置22、24、26、28に供給される。

(もっと読む)

半導体記憶装置

【課題】外部からID読み出し要求が入力された場合でも、システムブートに支障を来すことがない半導体記憶装置を提供する。

【解決手段】データを記憶するメモリ部と、メモリ部に対するアクセスを制御するメモリコントローラとを有し、メモリコントローラは、パワーオンリセット期間中に外部からID読み出し要求が入力されたら、ダミーIDを外部に出力する機能を有する。

(もっと読む)

1 - 20 / 71

[ Back to top ]