Fターム[5B079BC01]の内容

Fターム[5B079BC01]に分類される特許

101 - 120 / 506

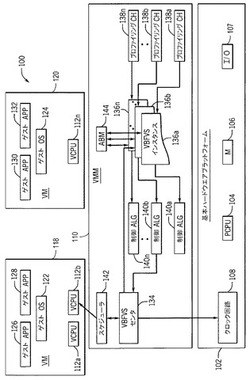

仮想CPUベースの、周波数、及び電圧制御

【課題】仮想環境の各々の仮想プロセッサのために実行される周波数、及び電圧制御を統合して、性能を犠牲にせずにパワーセービングを達成する。

【解決手段】各々の仮想プロセッサによって実行されるワークロードの特徴は、動的にプロファイルが作られ、かつ制御アルゴリズム140a〜140nは、前記プロファイルが作られた特徴の関数として、その仮想プロセッサのための制御ファクタを決定する。プロファイルが作られた特徴は、実行されている前記ワークロードに関連づけられた、仮想化イベントを含んでもよく、加えて、特定の制御アルゴリズム、及びプロファイリング技術は、どの仮想プロセッサが現在動作しているかに基づいて選択されてもよい。

(もっと読む)

プロセッサシステム、命令列最適化装置、および命令列最適化プログラム

【課題】複数のプロセッサを備えたプロセッサシステムの消費電力を処理能力を低下させることなく低減する。

【解決手段】命令解析部402は記憶部100に記憶されている所定量の一連の命令コードを先読みして解析し、各命令がCPU103とHWE104で並列に実行可能な場合に、標準実行時間推定部403、換算実行時間算出部404が標準実行時間の推定、換算実行時間の算出をし、割り当て・クロック周波数決定部405はCPU103およびHWE104を最高クロック周波数で動作させた場合に待ち時間が生じる方に最高クロック周波数よりも低い周波数のクロック信号を供給することにより消費電力が最小になるようにプロセッサの割り当て、クロック周波数を決定し、クロック制御部106は出力するクロック信号の周波数を切り替え、命令割り当て制御部102は命令コードをCPU103等に転送して実行させる。

(もっと読む)

情報処理装置

【課題】余分な消費電力の発生を抑制することを課題とする。

【解決手段】情報処理装置は、割り込みコントローラへの割り込み要因の入力とともに、当該割り込みコントローラへのクロック信号を送信する。また、情報処理装置は、割り込みコントローラへ入力される割り込み要因がマスク対象である場合に、当該割り込みコントローラへのクロック信号の送信を停止する。また、情報処理装置は、DSPへの割り込み信号がマスク対象である場合に、割り込みコントローラへのクロック信号の送信を停止する。また、情報処理装置は、DSPへの割り込み信号の入力とともに、当該DSPへのクロック信号を送信する。また、情報処理装置は、DSPにおける処理の終了後、終了通知を受信し、割り込みコントローラ及びDSPへのクロック信号の送信を停止する。

(もっと読む)

集積回路装置、電子機器及び調整電圧の制御方法

【課題】 温度条件が変化しても停止電圧との適切な電位差を保ち低消費電力を実現する集積回路装置等を提供する。

【解決手段】 集積回路装置1であって、第1の振幅と比べて、入力された発振信号400の振幅の方が大きい場合に、第1の矩形波信号408を出力する第1の矩形波信号生成部11と、前記第1の振幅よりも大きな第2の振幅と比べて、前記発振信号400の振幅の方が大きい場合に、第2の矩形波信号402を出力する第2の矩形波信号生成部12を含む。

(もっと読む)

IEEE1394通信装置、IEEE1394通信システム及びその電力制御方法

【課題】アクティブな機器が接続されても、動作状態に応じて任意のタイミングで省電力モードへ移行、及び復帰することで機器の発熱低減を実現するIEEE1394通信装置、IEEE通信システム及びその電力制御方法を提供する。

【解決手段】CPU11と、LINKチップ1と、PHYチップ12と、LINKチップ1にクロックを供給するクロックジェネレータ2を有するIEEE1394通信装置において、LINKチップ1に、Asynchronous転送を制御するAsynchronous制御回路8と、Isochronous転送を制御するIsochronous制御回路9とを備え、Asynchronous制御回路8及びIsochronous制御回路9に、独立にクロックを供給する。

(もっと読む)

情報処理装置

【課題】動画像再生が可能な情報処理装置に関するものであり、期待するフレームレートを維持し、かつ消費電力を低減させる為の省電力制御を提供する。

【解決手段】動画像の任意の1フレームのデコード処理の終了から画像表示までの時間とCPUの動作周波数を変更させる為に必要な時間とを比較し、比較結果に基づいて次に処理すべきフレームのデコード処理に必要なCPUの動作周波数を決定し、CPUの動作周波数を変更または休止する。

(もっと読む)

電力管理においてクロックを起動させる戦略法

システムは、電圧検知モジュールと周波数調節モジュールとを含む。電圧検知モジュールは、回路ブロックの供給電圧を検知し、供給電圧が第1の電圧以下である場合、第1の制御信号を生成し、供給電圧が第2の電圧の所定の範囲内にある場合、第2の制御信号を生成する。周波数調節モジュールは、電力投入再設定の後に初めて供給電圧が回路ブロックに供給された場合、及び、第1の制御信号または第2の制御信号が受信された場合に、回路ブロックに供給されるクロック信号の周波数を、回路ブロックの通常の動作周波数未満の値に設定する。 (もっと読む)

論理回路設計支援方法及び装置

【課題】 実動作において低消費電力化が図れるゲーティッドクロック設計が可能な論理回路設計支援方法を提供する。

【解決手段】 最適化対象論理回路の回路構造を記述した回路データD1に基づいて、最適化対象論理回路に入力する複数のイネーブル信号の情報D2を抽出する第1ステップS1と、最適化対象論理回路と抽出された複数のイネーブル信号の生成論理に対して実動作モードの論理シミュレーションを実行して、イネーブル信号毎の動作時におけるアクティブ状態と非アクティブ状態間の状態遷移に係る時系列情報D4を取得する第2ステップS2と、時系列情報D4に基づいて、最適化対象論理回路とクロックゲーティング回路の合計消費電力が、クロックゲーティング回路を挿入する前の最適化対象論理回路の消費電力より低減されるように、クロックゲーティング回路の挿入個数及び挿入箇所を最適化する第3ステップS3〜S5を有する。

(もっと読む)

マルチコアプロセッサ用の電力チャネルモニタ

マルチコアプロセッサ内での電力チャネル監視の技法を、全般的に説明する。電力管理システムを、マルチコアプロセッサ内の個々のコアに供給する電力チャネルを監視するように構成することができる。電力チャネルモニタは、各コアの電力消費の直接測定値を提供することができる。個々のコアの電力消費は、どのコアの使用が多いか、または少ないかを示すことができる。使用判定を、測定されるコアへまたはこれからのデータメッセージの送信を全く伴わずに行うことができる。各プロセッサコアによってサービスされる判定された使用負荷を使用して、そのコアに供給される電力および/またはクロック信号を調整することができる。  (もっと読む)

(もっと読む)

共振クロック分配ネットワークの周波数スケール調整された作動のためのアーキテクチャ

共振クロック分配ネットワークのためのアーキテクチャが提示される。このアーキテクチャにより、選択的にイネーブルされるフリップフロップの導入によって、複数のクロック周波数での共振クロック分配ネットワークのエネルギ効率の良い作動が可能になる。提示されたアーキテクチャは、主として一体化インダクタを有する共振クロックネットワーク設計を目的としており、インダクタのオーバヘッドが出現しない。このようなアーキテクチャは一般に、複数のクロック周波数を有しマイクロプロセッサ、ASIC、及びSOC等の高性能かつ低電力のクロッキング要件の半導体デバイスに適用可能である。更に、達成可能な性能レベルの応じた半導体デバイスのビニングに適用可能である。 (もっと読む)

クライアント端末及びシンクライアントシステム

【課題】ネットワーク帯域を考慮してクロック周波数を制御することで無駄な消費電力を抑えることが出来るクライアント端末及びシンクライアントシステムを提供する。

【解決手段】ネットワークを介して受信したデータを処理する処理部を備えるクライアント端末であって、前記ネットワークの帯域に合わせて、前記処理部を動作させるクロック周波数を判別する判別手段と、前記処理部のクロック周波数を、前記判別されたクロック周波数に変更するクロック制御手段と、を備えることを特徴とする。

(もっと読む)

無線デバイスにおける消費電力の最適化に関する装置と方法

無線デバイスのパワー最適化に関する装置と方法が開示されている。前記の装置と方法は、プロセッサからのデータ出力とプロセッサへのデータ入力をバッファするデータ・バッファに記憶されるデータの前記量を監視することに影響する。前記バッファに記憶される前記データの量に依存して、ダイナミックなクロック及び電圧のスケーリング(DCVS)機能のような、制御機能のパラメータは、前記データ・バッファに記憶されるデータの前記量に基づいて修正される。前記制御機能の前記パラメータを修正またはプリエンプティングすることで、これは少なくともプロセッサ周波数で制御するが、前記プロセッサは初期のパラメータ設定をこえてよりダイナミックにアプリケーションを処理できて、特に、1つかそれ以上のリアルタイム・アクティビティが完了に関して厳密な時定数を持つような状況では、増大したバッファの深さにはっきり表されるように前記プロセッサによりハンドルされる。その結果、前記制御機能が処理する条件に対して敏感であるので、電力の使用はさらに最適化される。  (もっと読む)

(もっと読む)

ベクトル処理装置、ベクトル処理方法、およびプログラム

【課題】 ベクトル処理において、ベクトルマスク制御やベクトル長制御により、ベクトル命令で読み書きが行われない要素に対する制御で消費電力を低減する。

【解決手段】 同一要素番号を有する要素を要素単位でSRAMに格納する要素単位ベクトルレジスタと、要素単位ベクトルレジスタからの要素の読み出し、要素間の演算、および要素単位ベクトルレジスタへの演算の結果の書き込みを制御するベクトル演算処理部と、マスク制御またはベクトル長制御により読み書きが行われない要素単位で要素単位ベクトルレジスタのクロックを停止するクロック停止処理部と、を備える。

(もっと読む)

マイクロコンピュータ

【課題】 CPUのスリープ状態時に、CR発振回路が生成する低速且つ周波数ばらつきの大きいクロックに基づき動作する起動タイマを備えるマイクロコンピュータにおいて、正確なスリープ期間を判定することができる半導体集積回路を提供する。

【解決手段】 CR発振回路が生成するクロックを、分周比が選択可能な分周回路に入力し、分周比を設定するとともに、水晶発振回路が生成するクロックにより基準期間信号を生成し、分周回路からのクロック信号出力の1周期と、基準期間信号との比から、起動時間設定レジスタ値の補正を行う手段を備える。

(もっと読む)

携帯機器、プログラム、および記録媒体

【課題】CPUの負荷を切り替えることなく、省電力化が可能な携帯機器を提供する。

【解決手段】携帯情報端末1は、バッテリの残存容量を評価する容量評価部28と、容量評価部28が評価したバッテリの残存容量に応じて、GPUの動作周波数を切り替える周波数制御部26と、周波数制御部26が切り替えた動作周波数に応じて、GPUの画像処理を制御する画像処理制御部30とを備えていることを特徴とする

(もっと読む)

半導体集積回路

【課題】独立してクロック信号の供給と遮断が行われる領域を有する半導体集積回路において、クロックスキューを低減し、かつ、消費電力を低減すること

【解決手段】本発明にかかる半導体集積回路1は、クロック信号が供給される第1の配線と、第1の配線に供給されるクロック信号とは独立して供給と遮断とが切り替えられてクロック信号が供給される第2の配線と、第1の配線からクロック信号が供給される第1のメッシュ形状配線を有する第1の領域と、第2の配線からクロック信号が供給される第2のメッシュ形状配線を有する第2の領域と、第1のメッシュ形状配線と第2のメッシュ形状配線の間の信号の導通と遮断を切り替え可能な切り替え回路とを備える。

(もっと読む)

半導体集積回路及び省電力制御方法

【課題】本発明は、効果的な省電力を行う半導体集積回路及び省電力制御方法に関する。

【解決手段】I/O制御用デバイス14は、バス監視クロック制御部25が、サブCPU22のバスアクセス信号を監視し、該バスアクセス信号の監視結果に基づいて、クロックジェネレータからサブCPU22及びI/O制御用デバイス14内の各部に供給される動作クロックの周波数を個別に指定制御する。したがって、プログラムを用いることなく、ハードウェア構成によって、I/O制御用デバイス14の動作状況に応じて動作クロックの周波数を変更する。

(もっと読む)

携帯機器に搭載されるプロセッサ、および消費電流低減方法

【課題】複数のブロックの使用状態に応じてクロック信号の周波数を変更して、消費電流を低減することができるプロセッサを提供する。

【解決手段】プロセッサ50は、クロック信号にもとづいて機能をそれぞれ実現するように動作する複数のブロック(Aブロック51、Bブロック52、およびCブロック53)を備え、周波数決定手段54と、周波数変更手段55と、クロック信号供給手段56と、周波数測定回路57とを含む。周波数決定手段54は、クロック信号の周波数を各ブロックの動作状態に応じた周波数に決定する。周波数変更手段55は、クロック信号の周波数を周波数決定手段54が決定した周波数に変更する。クロック信号供給手段56は、周波数変更手段55によって周波数が変更されたクロック信号を各ブロックに供給する。

(もっと読む)

半導体集積回路及びそのクロック制御方法

【課題】従来の半導体集積回路は、効果的にピーク電流を抑制することができないという問題があった。

【解決手段】本発明にかかる半導体集積回路は、クロック生成回路と、クロック生成回路により生成されるクロックに基づいて動作するモジュール7と、クロック生成回路により生成されるクロックに基づいて動作し、モジュール7との間でデータ転送を行うモジュール8と、を備え、モジュール7とクロック生成回路との間のクロック経路上に挿入された遅延素子の数と、モジュール8とクロック生成回路との間のクロック経路上に挿入された遅延素子の数と、に基づいてモジュール7及びモジュール8に供給されるクロックの位相が異なる。このような回路構成により、効果的にピーク電流を抑制することができる。

(もっと読む)

回路設計方法、及び回路設計プログラム

【課題】論理合成済みの回路に対して容易かつ高精度にクロックゲーティングセルを挿入することができる回路設計方法、及び回路設計プログラムを提供することである。

【解決手段】本発明にかかる回路設計方法は、設計者の意図する論理に基づいて、クロックゲーティング条件を含まないRTL記述ファイルを作成する第1のステップ(ステップS1)と、論理合成ツールを用いて、RTL記述ファイルに基づき第1のネットリストを生成する第2のステップ(ステップS2)と、第1のネットリストにクロックゲーティングセルを挿入して第2のネットリストを生成する第3のステップ(ステップS3)と、自動レイアウトツールを用いて、第2のネットリストに含まれるセルの配置を決定する第4のステップ(ステップS4)と、を有する。

(もっと読む)

101 - 120 / 506

[ Back to top ]