Fターム[5B079CC02]の内容

計算機・クロック (4,131) | 位相/タイミングの調整 (657) | 調整手段 (364) | 遅延回路を用いるもの (210)

Fターム[5B079CC02]に分類される特許

201 - 210 / 210

遅延制御装置

【課題】本発明は、データをストローブ信号に同期させて取り込む際のデータとストローブ信号の同期を簡単かつ適切にとる遅延制御装置を提供する。

【解決手段】遅延制御装置1は、MUX11がストローブ信号を選択しているときに、遅延素子13が、当該ストローブ信号を遅延値だけ遅延させて、データをストローブ信号に基づいて取り込むフリップフロップ23〜26に入力させ、MUX11がクロックを選択しているときに、遅延素子12と遅延素子13のクロックの遅延出力の位相を、位相比較器14で比較し、遅延制御回路15で、位相比較器14の比較結果に基づいて、第2遅延素子の遅延値を制御する。したがって、遅延素子13のフリップフロップ23〜26に至るまでの遅延値を基準となる遅延素子12の遅延値と等しくし、データ転送を適切に行うことができる。

(もっと読む)

システムLSI

【課題】 製造プロセスのばらつきによるシステムLSIの製品不良を回避する。

【解決手段】 ROM等の特定ブロック20へのクロック供給経路上に、縦続接続された複数の遅延素子31a〜31cとセレクタ32で構成されて遅延制御信号DCNに従って遅延クロック信号DCKを選択出力するクロック遅延回路30を設ける。製品試験時に、セレクタ43を介して遅延調整端子51から遅延制御信号DCNを与えて特定ブロック20の動作試験を行い、正常動作が得られる遅延制御信号DCNの値を調べる。製品試験で得られた適正な遅延制御信号の値を、ヒューズ回路またはPROMで構成される遅延設定回路40に記憶させる。通常動作時には、遅延設定回路40の記憶内容をセレクタ43を介してクロック遅延回路30に与える。

(もっと読む)

SMD任意逓倍回路

【課題】

入力信号に同期し逓倍数が可変に設定される信号を出力する逓倍回路の提供。

【解決手段】

入力信号の周波数を可変に逓倍した出力信号を出力する逓倍回路であって、入力信号の周期を測定する周期測定用の遅延回路と、周期測定用の遅延回路で測定された周期に基づき、遅延時間が可変に設定され、遅延時間を再現する遅延再現用の遅延回路とを備えた同期遅延回路10と、同期遅延回路から出力される位相が異なる複数の信号を受けて多重化する多重回路20と、設定逓倍値にしたがって、周期測定用の遅延回路の遅延段数、遅延再現用の複数の遅延回路の段数の設定を可変に設定する制御回路30とを備え、多重回路20から入力信号に同期しその周波数を逓倍した出力信号が出力される。

(もっと読む)

多重データレートRAMメモリコントローラ

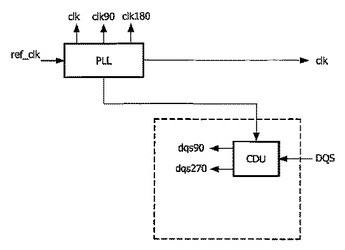

多重データレートRAMメモリモジュールのメモリコントローラを備える。前記コントローラは、参照クロック(ref clk)から異なるクロック位相(clk、clk90、clk180)を生成するためのPLLユニット(PLL)を含む。さらに、ストローブ信号(dqs)を遅延させるための制御可能な遅延ユニット(CDU)を備える。  (もっと読む)

(もっと読む)

遅延線同期装置および方法

従来の調節可能な遅延回路と用いることにより、異なるクロック領域のクロック信号のうちの1つが出力される調節可能な遅延回路の時間遅延が変更されても、それらのクロック信号間の擬似同期位相関係を維持することが可能な同期システムおよび方法。  (もっと読む)

(もっと読む)

プログラマブルクロック生成

集積回路用のクロック信号を生成するメカニズム、又はその部品であって、クロック出力線に偽信号又は異常が作り出されることなく、周波数が安全に連続的に変化され得る(すなわち、漸進的な周波数変化)。典型的な実施例に係る電子装置は、2つの入力信号を有するマルチプレクサ10を含み、第2のマルチプレクサは、第1のマルチプレクサの遅延型であって、一般的な組み合わせの遅延素子12を介して、マルチプレクサ10に入力を供給することによって作り出され、そして、マルチプレクサ出力idは、インバータ14を介して出力(Out)へ供給される。素子はさらに、「D」入力としてのプログラミング信号(Fk)を有するD型フリップフロップ16を含み、D型フリップフロップからの2つの出力「Q」及び「Qn」は、それぞれの駆動信号をマルチプレクサ10に供給する。入力信号(In)に対する出力信号(Out)の遅延は、プログラミング信号(Fk)の値に依存し、ローカルクロック(sync_ck)の立ち上がりエッジに同期する。  (もっと読む)

(もっと読む)

遅延ロックループ位相混合回路

例えば遅延ロックループ(DLL)回路において、位相を微調整するための技術および回路構成を提供する。1つまたは複数の遅延素子を電流源の出力ノードと選択的に接続することにより、複数の位相信号を、単一の電流源から生成するようにすることができる。遅延素子は、電流源を切り替えることによって生成される信号のタイミングを変更するようにすることができる。  (もっと読む)

(もっと読む)

クロック信号を同期化する際に使用する装置、および、クロック信号同期化方法

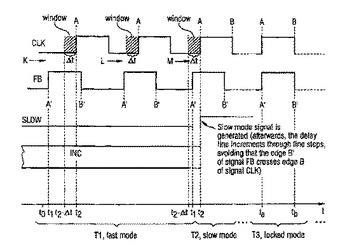

本発明は、可変制御可能な遅延時間(tvar)を有する遅延手段(2)を備え、クロック信号(CLK)またはこのクロック信号(CLK)から得られる信号が、遅延手段(2)に入力され、可変制御可能な遅延時間(tvar)だけ遅延され、遅延されたクロック信号(DQS)の形状で出力される、クロック信号同期化方法、および、クロック信号(CLK)の同期化に使用する装置(1)に関するものである。本発明は、遅延手段(2)から出力される遅延されたクロック信号(DQS)またはこのクロック信号(DQS)から得られる信号(FB)の上記クロックエッジ(A’)が、上記クロック信号(CLK)またはこのクロック信号(CLK)から得られる信号の対応するクロックエッジ(A)の前の所定の時間窓の内側にあるかどうかを決定するためのデバイス(5)が設けられていることを特徴とする。  (もっと読む)

(もっと読む)

多電源半導体装置

複数のブロック31、32により構成され、各ブロック31、32が独立したクロック回路41、42を有し、可変電源101により動作する多電源半導体装置において、クロック生成回路10から複数のブロック32に供給されるクロック信号に、可変電源101の電圧値に基づいて遅延量が変化する可変遅延回路20を設ける。このことにより、可変電源101の電源電圧を変化させた場合でも、ブロック間のクロックスキューが低減される。 (もっと読む)

可変遅延生成回路

【課題】 電流制御型発振回路4から出力されるクロック8の遅延量を細かく設定する。

【解決手段】 制御電圧1を入力し、この制御電圧1の大きさに対応した可変電流3を出力するV/Iコンバータ2と、可変電流3を入力し、この可変電流3の大きさに対応した周波数のクロック8を出力する電流制御型発振回路4と、クロック8、及び可変電流3を入力し、この可変電流3の大きさに対応した遅延をクロック8につけて出力する電流制御型遅延回路9とを備えるものとした。

(もっと読む)

201 - 210 / 210

[ Back to top ]