Fターム[5B079CC02]の内容

計算機・クロック (4,131) | 位相/タイミングの調整 (657) | 調整手段 (364) | 遅延回路を用いるもの (210)

Fターム[5B079CC02]に分類される特許

61 - 80 / 210

動作モード設定装置、それを含む半導体集積回路および半導体集積回路の制御方法

【課題】クロックの状態変化による誤動作に対する適応性を向上させる動作モード設定装置、それを含む半導体集積回路および半導体集積回路の制御方法を提供する。

【解決手段】本発明の動作モード設定装置は、基準クロックとフィードバッククロックの位相を判別して固定猶予信号を生成する動作モード設定制御部およびリセット信号と前記固定猶予信号の制御によって位相比較信号とパルス信号に応答して固定完了信号を生成する動作モード設定部を含む。

(もっと読む)

多相クロック生成回路

【課題】高分解能の多相クロックを生成する。

【解決手段】第1のクロック生成回路120は、入力される2つの信号のレベル変換を行い該2つの信号のレベルが同一になるクロスポイントを基準にレベルが切り替わる一対のパルス信号を生成するレベル変換バッファ回路BUFをn段備える。第1のクロック生成回路120における第i段のBUFは、差動入出力する遅延素子DCELをn段リング状に接続してなるリング発振器110における第i段(1≦i≦n)と第(i+1)段(i=nの場合は1)の2つの遅延素子の差動出力のそれぞれの片側の出力からなる片側出力ペアを入力する。該片側出力ペアは、次段の遅延素子の正転端子に入力される2つの片側の出力、または次段の遅延素子の反転端子に入力される2つの片側の出力である。

(もっと読む)

マルチクロックネットワークを備えたデジタルデバイス用共振クロックおよびインターコネクトアーキテクチャ

バッファなしでクロックおよびデータ信号を分配する共振ドライバを使ったクロック、データ分配ネットワークが提案されており、低ジッター、低スキュー、低エネルギー消費、そして緩いタイミング要求が実現される。このようなネットワークは、概してFPGAのようなPLD用アーキテクチャに適用可能であり、同様に、マイクロプロセッサ、ASIC、SOCなど、複数のクロックネットワークとクロック周波数、ハイパフォーマンスおよび低電力クロッキング仕様をもつ他の半導体デバイスにも適用可能である。  (もっと読む)

(もっと読む)

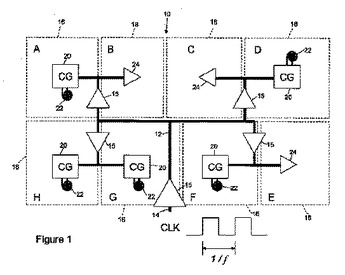

共鳴クロックされたシステムのためのクロック分配ネットワークアーキテクチャ

本明細書に開示されているのは、基準クロックを運ぶための分配ネットワークと、基準クロックによる同期作動のために基準クロックを受信するように分配ネットワークと結合された複数のサーキットドメインと、を含んでいるデジタルシステムである。複数のサーキットドメインの各サーキットドメインは、共鳴クロック信号を発生させるように基準クロックによって駆動されるそれぞれのクロックジェネレータと、共鳴クロック信号に従って作動するためにクロックジェネレータと結合されたそれぞれの回路であって、回路は、共鳴クロック信号のための容量性負荷を含む、回路と、回路の容量性負荷に共鳴するために回路およびクロックジェネレータに結合されたそれぞれのインダクタンスと、を含む。  (もっと読む)

(もっと読む)

半導体記憶装置

【課題】指定されたレイテンシ、外部クロック周波数での動作を安定して実現するために、製造ばらつき、動作電圧ばらつき、温度変化に対応して、適切な内部タイミング信号を発生する半導体装置を提供する。

【解決手段】外部入力コマンドサイクルによって決まるカラムサイクル時間で動作するべき回路ブロックのタイミング信号を発生する第1の遅延回路ブロックと、全体の遅延量が外部クロックとレイテンシで決まるアクセス時間とカラムサイクル時間の差に調節される第2の遅延回路ブロックを有する。これらの遅延回路ブロックは、カラムレイテンシ、動作周波数にあわせて各遅延回路の遅延量が適切な値に調節されると共に、プロセスや動作電圧のばらつき、動作温度の変化に対応して、遅延量が調節される。

(もっと読む)

多相クロック生成回路およびシリアルデータ受信回路

【課題】位相比較時のオフセットを少なくして高精度で高分解能の等位相多相クロックが生成されるとともに、小回路規模化および低消費電力化が図れる多相クロック生成回路およびシリアルデータ受信回路を提供する。

【解決手段】複数の電圧制御遅延回路2a〜2jを直列接続し、初段の電圧制御遅延回路2aの差動出力から生成される信号F00と、最終段の前段の電圧制御遅延回路2iの差動出力から生成される信号F88Aの逆相の信号であるF00Aとを、位相比較器3で比較し、比較結果をチャージポンプ4、ローパスフィルタ5を経由してバイアス回路から出力する制御電圧信号Pnct,Ncntで信号F00とF00Aとの位相差が無くなるように電圧制御遅延回路2a〜2jの遅延を調整し、電圧制御遅延回路2a〜2jの各差動出力信号からクロック生成部7でシングル信号に変換して等位相の多相クロックを生成する。

(もっと読む)

遅延信号発生回路

【課題】 遅延データを順次複数のカウンタにロードし、これらのカウンタを基準クロックでダウンカウントして、カウント値が所定の値になったタイミングでカウンタの出力を有効にするようにし、これらのカウンタ出力を合成して遅延信号を発生させる遅延信号発生回路では、連続して遅延トリガ信号を与えることができる遅延データの上限を増加させるためにはカウンタの数を増やさなければならず、レジスタの数が大きく増加してしまうという課題を解決する。

【解決手段】 遅延データによってシフト段数を変化させることができる可変段数シフトレジスタを用い、カウンタの出力をこの可変段数シフトレジスタでシフトするようにした。連続して遅延トリガ信号を与えることができる遅延データの上限を増加させる場合に、従来に比べてレジスタの増加を大幅に抑えることができる。

(もっと読む)

クロック信号供給回路

【課題】クロック信号が安定するまでの待ち時間を設定するレジスタの初期値を任意に変更可能としたクロック信号供給回路を提供する。

【解決手段】待ち時間設定部は、起動時の初期値に基づいて、待ち時間設定信号を選択するための選択信号を出力するデータ保持回路9a,9bと、選択信号に基づいて待ち時間設定信号を選択する選択回路と、データ保持回路9a,9bの初期値を任意に設定可能とする初期値設定回路21,22,23,24,25とを備えた。

(もっと読む)

半導体集積回路

【課題】通信相手の半導体集積回路に位相比較回路および位相調整回路を設けなくとも、通信相手の半導体集積回路がデータ信号の取り込みタイミングを知らせるクロック信号を元にデータ信号を良好に受信することができるようにした半導体集積回路を提供する。

【解決手段】タイミング最適化回路51により、DQ0送受信回路48、DQ1送受信回路49およびDQ2送受信回路50における送信タイミングを調整し、メモリ42が、メモリコントローラ41が送信するデータ信号DQ0〜DQ2の各ビットのデータ信号をセンターポイントで受信できるようにする。

(もっと読む)

同期回路

【課題】広い範囲で遅延調整を可能にしてACタイミングを確保し易くする。

【解決手段】フリップフロップ回路FF1と組合せ論理回路LOGIC1との間にフリップフロップ回路FF1aを挿入し、セレクタMUX1によりいずれか一方のフリップフロップ回路の出力データ信号を選択可能にする。フリップフロップ回路FF1に入力するクロック信号をフリップフロップ回路FF1aに入力するクロック信号よりも遅らせる。

(もっと読む)

タイミング調整回路及びそれを備えた半導体装置

【課題】テスト装置のピン間スキューによる制限を受けること無く、高い精度でタイミングずれを除去することができるタイミング調整回路を提供する。

【解決手段】タイミング調整回路30に、データ入力回路66のレプリカ回路31を設ける。レプリカ回路は、初段回路32とラッチ回路33とを含む。初段回路は、外部クロック信号を受け参照クロック信号を出力する。クロックドライバ64からの内部クロック信号に同期して、参照クロック信号をラッチし、外部出力端子34へ位相進み遅れ信号として出力する。

(もっと読む)

DDR−SDRAMインターフェース回路

【課題】安定したデータ取り込みや、遅延時間の微調整や、消費電流の削減が可能なDDR−SDRAMインターフェース回路を提供すること。

【解決手段】4分周回路13から出力される内部クロック信号CLK1が、遅延回路30に入力される。遅延回路30は、遅延バッファDB1およびDB2、バリアブルディレイライン31を備える。遅延バッファDB1は出力バッファOB1と同一素子、同一回路構成を有し、遅延バッファDB2は入力バッファIB2と同一素子、同一回路構成を有する。遅延回路30からは、内部クロック信号CLK1に総遅延時間DDTが付与されて得られた遅延内部クロック信号DCLK1cが出力される。フリップフロップFF2では、遅延内部クロック信号DCLK1cのエッジに応じて、サンプリングリードデータ信号SDQがサンプリングされる。

(もっと読む)

遅延調整回路を有するアレイ型プロセッサ

【課題】各構成のサイクル時間を調整可能とするアレイ型プロセッサの提供。

【解決手段】複数のプロセッサエレメント11がアレイ状に配置されたデータパス部10と、データパスの切り替え制御を行う情報を格納しておく状態遷移管理部12と、前記状態遷移管理部からの情報に基づき、入力されたクロック信号の遅延を調整し、前記データパス部に出力する遅延調整回路13と、を備え、前記遅延調整回路13は、遅延制御情報メモリ14とプログラマブルディレイ15を備え、遅延制御情報メモリは、複数の遅延制御情報を記憶しており、状態遷移管理部からの構成番号をアドレスとして遅延制御情報を読み出し前記遅延制御情報を前記プログラマブルディレイに与え、前記プログラマブルディレイは、入力されたクロック信号を前記遅延制御情報により指定された遅延だけ遅らせてデータパス部に出力する。

(もっと読む)

クロック発生回路

【課題】 DLL回路を用いたクロック発生回路においては、活性化される半導体装置が切り替わる場合に、DLL回路のロック時間が長くなるという問題がある。

【解決手段】 DLL回路の遅延調整回路を固定長遅延回路と、N個の可変長遅延回路で構成し、N個の半導体装置に内部クロックを供給する。N個の可変長遅延回路の遅延差をN個の半導体装置に対する遅延差と同じくする。選択された半導体装置に対し、遅延差がなくなるようにN個の可変長遅延回路からの遅延クロックを選択する。

(もっと読む)

クロック位相シフト回路

【課題】プロセス条件、電源電圧、温度等の変動によらず、入力クロックの位相シフトの調整ができ、かつ、従来のDLL回路を用いた場合と比較して占有面積の小さいクロック位相シフト回路を提供する。

【解決手段】入力クロックを遅延させる遅延回路の遅延セルと同一の遅延セルで構成されたリングオシレータを用いて、入力クロックのm周期分の発振出力をカウントし、入力クロックの1周期分の遅延セル段数を計算して位相シフト量分の遅延セル段数を設定する。

(もっと読む)

モジュラー・メモリー制御装置のクロック供給アーキテクチャ

【課題】 従来のクロック供給アーキテクチャは、単一のメモリー制御装置チャンネルの全てのデスキューを制御するために、比較的多数のロジック構成要素を実装する。

【解決手段】 ある実施例によると、メモリー制御装置が開示される。メモリー制御装置は、示差基準クロックを生成する位相ロック・ループ(PLL)、及び前記PLLと結合された第1のクロック供給構成要素を有する。第1のクロック供給構成要素は、前記基準クロックを受信し送信及び受信遅延デスキュー・クロック信号を生成する第1の遅延ロック・ループ(DLL)、データ送信デスキューを提供する第1の位相補間器セット、及びデータ受信デスキューを提供する第1のスレーブ遅延線セット、を有する。

(もっと読む)

情報処理装置および位相制御方法

【課題】冗長化された各系に供給されるクロックの位相差を補正するにあたって、精度よく柔軟に位相制御をおこなうこと。

【解決手段】スイッチカード3230aは、スイッチカード3130aから送信されたクロックをスイッチカード3130aへ折り返す。そして、スイッチカード3230aは、折り返されるクロックと、固定遅延回路3146aから出力される比較基準クロックの位相を比較し、折り返されるクロックの位相が比較基準クロックの位相と一致するように、スイッチカード3230aへ送信するクロックに遅延を加える可変遅延回路3143aを制御する。同様の動作を全ての系で実行することにより、全てのクロックの位相が比較基準クロックと一致することとなる。

(もっと読む)

分周クロック生成回路

【課題】クロック配線の末端においてもシステムクロックと分周クロックとの間に位相の逆転現象が発生しない分周クロック生成回路を提供する。

【解決手段】分周クロック生成回路1は、システムクロックFPHを分周した基本分周クロックPHを出力する分周器11と、クロック配線末端におけるシステムクロックFPHDの位相が基本分周クロックPHの位相に対して遅れているか進んでいるかを判定して判定信号SELを出力する位相判定回路12と、基本分周クロックPHを配線末端のシステムクロックFPHDに同期させた上で遅延させた遅延分周クロックPHTを出力する同期遅延回路13と、位相判定回路12から出力される判定信号SELが位相遅れを示すときは遅延分周クロックPHTを選択し、判定信号SELが位相進みを示すときは基本分周クロックPHを選択して、分周クロックPHSとして出力する選択回路14と、を備える。

(もっと読む)

タイマ起動回路

【課題】クロック生成回路を設け、このクロック生成回路からタイマスタート信号をトリガとして1周期Tのクロックを発生させ、カウンタに出力するようにしたものにおいては、カウンタ起動直後の時間に誤差が発生する。

【解決手段】クロック生成回路の出力側に遅延部を設け、この遅延部にクロック生成回路からのクロックとタイマスタートトリガとを印加する。タイマスタートトリガ印加後のクロック1周期時間経過後に、遅延部からクロックを発生させてカウンタに出力するよう構成する。

(もっと読む)

半導体装置、半導体集積回路装置、及び許容位相差測定回路

【課題】低コストで電流ピークを効果的に抑制することができる半導体装置を得る。

【解決手段】ステップST1において、モジュールA21とモジュールB22とのクロック位相を一致させた後、ステップST2において、モジュールA21からモジュールB22にデータ転送を行う。その後、ステップST3において、モジュールA21のクロックCLKAとモジュールB22のクロックCLKBとのクロック位相差を所定の大きさに設定した後、ステップST4において、モジュールA21とモジュールB22とがそれぞれ独立に所定の演算処理を行う。そして、ステップST5において、モジュールA21のクロックCLKAとCPU25のクロックCLKPとの位相を一致させた後、ステップST6においてモジュールA21の演算結果をCPU25で読み取る。

(もっと読む)

61 - 80 / 210

[ Back to top ]