Fターム[5B079CC02]の内容

計算機・クロック (4,131) | 位相/タイミングの調整 (657) | 調整手段 (364) | 遅延回路を用いるもの (210)

Fターム[5B079CC02]に分類される特許

101 - 120 / 210

I2Cクロックの生成方法及びシステム

I2Cクロック生成器を、多様な方法を用いてインプリメントする。そのような方法の1つを使用して、I2Cバス上のクロック信号(110)を制御するためのステートマシンに配置される論理回路を用いる方法をインプリメントする。ステートマシンの第1の状態(202)は、クロックストレッチング遅延を実行するか否かを判定する。ステートマシンの第2の状態(206)は、前記I2Cバスが、標準クロックモードにおいてか、または、他の複数の高速クロックモードのうちの1つで動作するように設定されているか否かを判定する。ステートマシンの第3の状態(210)は、クロック信号を一方の2値論理状態で駆動させる前に、クロック信号を、約0.5マイクロ秒以上で、約2.5マイクロ秒未満の間、他方の2値論理状態で駆動させ、そして、クロック信号を、約0.5マイクロ秒以上で、約2.5マイクロ秒未満の間、前記一方の2値論理状態のままにする。  (もっと読む)

(もっと読む)

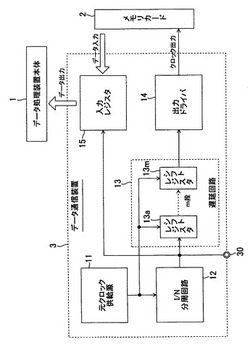

電子装置及びそのデータ通信装置

【課題】安価に且つ精度良く遅延量の調整すなわちタイミング調整を行うことができるデータ通信装置を提供する。

【解決手段】外部機器2との間でクロックに同期したデータ送受信を行うデータ通信装置において、高周波の元クロックを分周して基準クロックを生成し出力する基準クロック発生手段12と、カスケード接続された複数段のシフトレジスタ13a,…,13mで構成され基準クロックを取り込み所定遅延量だけ遅延させた遅延基準クロックを生成し出力するクロック遅延手段13と、前記手段12および13の一方から出力されるクロックを外部機器2に出力するクロック出力手段14と、前記手段12および13の他方から出力されるクロックにより動作し外部機器2から読み出されたデータを受信するデータ入力手段15とを備える。

(もっと読む)

情報処理装置

【課題】メモリカードが必要に応じて挿抜されるシステムにおいて、データ転送時におけるビット間スキューを調整し、データ転送の信頼性を向上させる。

【解決手段】ホストにメモリカードが挿入され、通信が正常に行われると、該メモリカードに書き込まれたテストデータライトを読み出し、その際にビット間スキュー検出回路24が検出したビット間スキューの検出データをビット間スキュー表示レジスタ25から読み出し、問題がない場合、あるいは、タイミング選択レジスタ23によるビット間スキューの調整で問題がないと判断するとメモリカードに対するリード/ライト動作を行う。また、ビット間スキュー値、またはタイミング選択レジスタ23によるビット間スキューの調整に問題がある場合、ビット間スキューの調整、またはビット幅の縮小などの処理を行う。

(もっと読む)

半導体集積回路

【課題】複数の順序回路として少なくともレベルセンス型順序回路を用いたシステムにおいて、動作周波数を高めると共に、信頼性を向上させる。

【解決手段】マイクロコンピュータ(1)は、クロック供給元とされるクロック発生回路(2)と、クロック信号CLKに同期動作する機能モジュールと、機能モジュールに含まれ、クロック供給先とされるレベルセンス型順序回路(12〜14)と、クロック信号をレベルセンス型順序回路に伝播するクロック供給系(11)等とを備える。クロック供給系は、クロック発生回路から出力されるクロック信号を複数の分岐を介して末端に伝播するクロック配線(20)を有する。クロック配線の途中には、少なくともパルス生成回路(26,28,29)が配置される。パルス生成回路は、レベルセンス型順序回路の入力動作期間の終点を規定するクロック信号の立ち下がりエッジの変化タイミングを可変とする。

(もっと読む)

データ出力装置、コントローラおよびクロック遅延量設定方法

【課題】 複数のクロックに対応してデータを出力するデータ出力装置において、データ読み取り側の装置に適した遅延量を確保するための技術を提供する。

【解決手段】 クロックを入力し、データを出力するデータ出力装置であって、多段に接続された複数の遅延手段と、前記遅延手段を通る個数の異なるクロックのうちいずれかのクロックを選択する遅延量選択手段と、前記選択されたクロックに合わせてデータを出力するデータ出力手段とを備えること特徴とするデータ出力装置。

(もっと読む)

データ処理装置

【課題】データ処理能力アップが必要な時だけクロック周波数を上昇し、データ処理能力アップが必要なくなるとクロック周波数を下降することにより、消費電力を低減できるデータ処理装置を提供する。

【解決手段】メモリ制御回路4、複数の遅延回路を含むクロック制御回路11などを有するデータ処理装置において、メモリ5に対するデータ転送リクエストを検出したらデータ処理回路(復調回路1、誤り訂正回路2、ホストI/F回路3)に供給するクロックを高い方に切り換え、一定期間検出しなかったらクロックを低い方に切り換えることにより、データ処理能力アップが必要な時だけクロック周波数を上昇させ、データ処理能力アップが必要なくなるとクロック周波数を下降させる。さらに、クロック切り換えは、各データ処理回路からのデータ転送リクエストの組み合わせにより段階的に行う。

(もっと読む)

EMI低減制御装置

【課題】EMI低減のためにスペクトラム拡散を行う際に、クロック周波数の推移による映像信号への影響を排除するためのFIFOメモリの容量を抑えること。

【解決手段】EMI低減のためにスペクトラム拡散を行う際に、スペクトラム拡散後のクロックは1水平期間よりも十分短い期間でスペクトラム拡散前のクロックに同期させるとともに、FIFOメモリの読み出しアドレスは書き込みアドレスよりもクロック周波数の変調量分量以上進めておく。

(もっと読む)

デジタルDLL回路

【課題】信号の立ち上がり側と下がり側の遅延は個別に制御でき、クロックのデューティーずれやデータ信号の立ち上がり/立ち下がりの遅延差を補償することができるデジタルDLL回路を提供する。

【解決手段】信号の立ち上がりエッジ側遅延指定のための第1遅延指定値を保持する第1レジスタ11、信号の立ち下がりエッジ側遅延指定のための第2遅延指定値を保持する第2レジスタ12、信号の立ち上がり側と下がり側の遅延を個別に制御可能なデジタル制御可変遅延回路13、および可変遅延回路13の立ち上がり側遅延と立ち下がり側遅延をそれぞれ第1レジスタ11の第1遅延指定値および第2レジスタ12の第2遅延指定値に維持するよう制御を行う制御回路14を有する。

(もっと読む)

周波数逓倍回路および送信装置

【課題】 本発明は、電子機器において所望のクロック信号を2逓倍する周波数逓倍回路と、その周波数逓倍回路によって生成された2逓倍クロック信号に同期して伝送情報のCMI符号化を行う送信装置とに関し、物理的なサイズが小さく、かつ安価に精度よく2逓倍クロック信号が生成されることを目的とする。

【解決手段】 クロック信号の周期Tの半分に相当する遅延d(=T/2)を前記クロック信号に与え、遅延クロック信号を生成する遅延手段と、前記クロック信号と前記遅延クロック信号との双方の前縁または後縁に同期し、パルス幅が前記周期Tの四分の一であるパルス信号の列を生成するパルス幅調整手段とを備えて構成される。

(もっと読む)

半導体集積回路

【課題】回路規模を大きくすることなく、複数の回路を動作させるための夫々のクロックの位相を容易に制御することが可能な半導体集積回路を提供する。

【解決手段】本発明の半導体集積回路40は、クロックを入力され、クロックの1周期分に相当する同相遅延素子段数CTを求める遅延制御手段41と、遅延制御手段41により求められた同相遅延素子段数CTから、所定量の遅延を発生させる遅延素子の段数DEGOUT1〜DEGOUTnを決定する遅延素子段数決定手段42と、クロックを遅延素子段数決定手段42により決定された遅延素子の段数分遅延させる遅延クロック生成手段431〜43nとを有する

(もっと読む)

デジタルDLL回路

【課題】位相比較回路等を用いることなく、簡単な構成で遅延フィードバック値を容易に得ることができ、複雑な制御を容易に行うことができるデジタルDLL回路を提供する。

【解決手段】遅延目標値を保持するレジスタ11、リングオシレータ12、測定周期を決めるために、外部の基準クロックRCLKをカウントする第1カウンタ13、第1カウンタ13で決まる測定周期ごとにリングオシレータ12の発振出力クロックCLKをカウントする第2カウンタ14、デジタル制御の可変遅延回路15、および第1カウンタ13のカウント値C1を基に、第1カウンタ13および第2カウンタ14のリセット、起動、さらに必要に応じて停止の制御を制御信号CTL1、CTL2に基づいて行い、第2カウンタ14のカウント値C2とレジスタの遅延目標値DVをデジタル演算して、この演算結果を可変遅延回路15に遅延制御値DCVとして与える制御回路16を有する。

(もっと読む)

遅延素子の遅延寄与決定を有する時間−デジタル変換

【課題】本発明は、時間−デジタル変換に対応する方法に関する。

【解決手段】遅延素子(126.1、...、126.N)の少なくとも1つのチェーンを備える時間−デジタル変換器(110)であって、前記遅延素子(126.1、...、126.N)のチェーンのステータスが変換する時間間隔に関連するデジタル信号を表し、前記時間−デジタル変換器(110)が、遅延素子(126.1、...、126.N)の中で転送されるパルスを基準にして統計的に等しく分散された可変位置を有するトリガ信号(154)を供給する手段(156)であり、前記較正トリガ信号(154)に応じて遅延素子(126.1、...、126.N)の前記チェーンのステータスを捕捉する手段(130)であって、前記ステータスは前記遅延素子(126.1、...、126.N)の遅延時間によって決まり、前記較正トリガ信号(154)に応じて、パルス位置の発生に基づく前記遅延素子(126.1、...、126.N)の全遅延に対する少なくとも幾つかの前記遅延素子(126.1、...、126.N)の実寄与を決定する手段と、前記時間間隔を前記デジタル信号(168)に変換する際に、少なくとも幾つかの前記遅延素子(126.1、...、126.N)の前記実寄与を考慮する手段(164)とを備えることを特徴とする時間−デジタル変換器(110)。

(もっと読む)

半導体集積回路及びそれを用いたデューティ測定・補正方法

【課題】 外部信号を用いずにクロック信号のデューティを正確に測定及び補正する。

【解決手段】 半導体装置20には、半導体集積回路としてのデューティ測定・補正回路1及びPLL回路4が設けられている。デューティ測定・補正回路1は、デューティ測定回路部2及びデューティ補正回路部3から構成され、デューティ比が変化した補正前クロック信号CLKAが入力される。デューティ測定回路部2から出力される信号Outが“Low”レベルから“High”レベルに変化したときのデューティ測定回路部2の遅延回路の遅延時間が補正前クロック信号CLKAのデューティとして、デューティ測定回路部2で測定される。このとき、デューティ測定回路部2の遅延回路と対をなすデューティ補正回路部3の遅延回路が選択されて、補正前クロック信号CLKAのデューティがデューティ補正回路部3で補正される。

(もっと読む)

半導体装置およびデータ入出力システム

【課題】 外的要因による影響からシステムクロックの周期を短くし、高速化を図ることは困難であった。

【解決手段】 半導体装置は、システムクロックに基づいた内部クロックで動作し、前記内部クロックに同期してデータを入出力する半導体装置であって、前記内部クロックを生成する位相同期回路と、前記半導体装置のデータの入出力に基づいて、前記位相同期回路に対するフィードバックループに挿入される遅延パスを切り替えるスイッチ素子とを有する。

(もっと読む)

半導体装置

【課題】内部ブロックの動作による電源変動によっても外部出力クロックの出力に影響を及ぼさないことにより、より安定したクロック信号を供給することの可能な半導体装置を提供する。

【解決手段】発振源102から出力されるクロックを基準として外部回路118とデータの授受を実行する半導体装置100において、発振源から出力されるクロックを半導体装置に備わる内部回路114へ分配するクロック分配手段112と、クロックを外部回路に供給するクロック供給手段104と、外部回路に供給されるクロックとクロック分配手段の終端におけるクロックとの位相差を検出する位相差検出手段106と、位相差検出手段で検出された位相差のデータを元にクロック供給手段から出力されるクロックの遅延を調整するクロック遅延調整手段110と、を含むことを特徴とする。

(もっと読む)

半導体集積回路のクロックツリー形成方法およびプログラム。

【課題】製造ばらつきの影響の小さいクロックツリーを生成するクロックツリー形成方法を提供する。

【解決手段】クロックツリー回路のFF対のフリップフロップ間の経路に対して、クロックスキューがない状態でタイミング解析を行い、ホールドエラーが発生する基準値に対しての余裕度としてホールドスラック値を求めるホールドスラック計算処理22と、クロックツリー回路の分岐点となるバッファからFF対ごとのフリップフロップ入力間の経路に対して、経路の遅延の最小値、最大値を計算し記憶するバッファ遅延計算処理23と、経路ごとにホールドスラック値と最大値から最小値を減算した結果を比較して、ホールドスラック値より大きいと判断された場合はFF対をグループ化するFF対集合操作処理24と、同一グループのFF対の経路ごとに、FF対が同一のバッファで駆動するようにバッファを挿入するバッファ挿入処理25を行う。

(もっと読む)

同期式半導体メモリ装置

【課題】レイテンシ制御が改善された同期式半導体メモリ装置を提供する。

【解決手段】半導体装置は、外部クロック信号を受信してデータ出力クロック信号を提供するクロック同期回路、少なくとも一つのクロック制御信号を出力遅延時間と読出命令遅延時間との和の分だけ遅延させ、少なくとも一つの遅延されたクロック制御信号に同期した少なくとも一つのサンプリングクロック信号を発生させるレイテンシ制御回路、少なくとも一つのサンプリングクロック信号に応答して読出信号を保存し、データ出力クロック信号を受信して順次に少なくとも一つのクロック制御信号を発生させ、少なくとも一つのクロック制御信号に同期した少なくとも一つのトランスファークロック信号を発生させ、読出信号の保存に使われた少なくとも一つのサンプリングクロック信号と関連したトランスファークロック信号に応答してレイテンシ信号を提供するレイテンシ回路を含む。

(もっと読む)

入力クロックの位相補償装置

【課題】入力クロックの位相の遅延を補償する。

【解決手段】2つのクロック信号の位相差を検出する位相比較部120および130と,位相比較部120および130の後段と発振器150との前段との間に設けられ,位相比較部120および130からの出力信号の中から1つを切り換えて出力する信号切換部140と,信号切換部140の後段に設けられ,位相比較部120および130の出力電圧に応じた周波数を出力する発振器150と,を含み,位相比較部120および130は,外部からのクロック信号と,発振器150から出力されたクロック信号との位相を比較して差分信号を出力し,発振器150は,信号切換部140から出力されたクロック信号を入力し,位相比較部120および130にクロック信号を与えることを特徴とする,入力クロックの位相補償装置100が提供される。

(もっと読む)

半導体メモリのクロック回路

【課題】読み込みアクセス時間tACがクロック周期tCKを越えないことを確実にするために、読み込み出力を駆動する遅延されたクロック信号を生成する回路技術を提供する。

【解決手段】本発明の回路及び方法は、半導体メモリ装置において、読み込みアクセス時間がクロックの周期時間を越えないことを確実にするために、入力クロック信号から読み込みクロック信号を生成する。上記クロック信号の周波数に応じて、複数の遅延量の1つが、上記入力クロック信号に課されるために選択される。

(もっと読む)

DLL制御遅延線のタイミング分解能を改善するための方法

【課題】 遅延線のタイミング分解能を改善する。

【解決手段】 マスタ電圧制御遅延線における遅延段の数を可変にすることによって、DLLに基づく遅延線のタイミング分解能を達成することができる。スレーブ電圧制御遅延線で選択されるタップのみならず、マスタ電圧制御遅延線における遅延段数をも調整することにより、固定長マスタ電圧制御遅延線を使用する従来の遅延線回路に比較したとき、タイミング分解能を少なくとも2倍に改善することができる。

(もっと読む)

101 - 120 / 210

[ Back to top ]