Fターム[5B079DD17]の内容

Fターム[5B079DD17]に分類される特許

1 - 20 / 22

半導体集積回路及びその省電力制御方法、並びに半導体装置

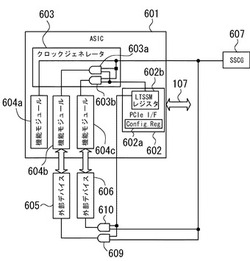

【課題】デバイス間のインタフェースとしてPCI Expressを用いた画像処理装置において、画像読取部からの画像データで、画像データの転送に影響を与えずに、ASPMを利用可能にする。

【解決手段】LTSSMで定義された状態のうち、低消費電力(省電力)状態にいることを示す信号をLTSSMレジスタ602bからアンド回路603a,603bに出力し、SSCG607からのクロックをマスクすることにより、PCIeのリンクの状態に応じて、ASIC601内の所定の機能モジュールへのクロック供給を止めることができる。これにより、ASIC601の消費電力を削減できる。ASPMによる動的なクロックゲーティングが可能となり、ASIC601内のこまめな省電力制御が実現できる。

(もっと読む)

位相補間回路及びその設計方法

【課題】トランジスタのばらつきによる影響を抑制し、位相歪みを解消する位相補間回路を提供する。

【解決手段】位相補間回路は、位相の異なる入力波形を受け付ける複数の差動対を含み、複数の差動対のうち、第1の差動対及び第2の差動対の出力波形を合成する位相補間回路である。さらに、複数の差動対にバイアス電流を供給する電流源をn個含み、第1の差動対に供給するバイアス電流を、n個の電流源のうち、m個の電流源から供給可能であると共に、第2の差動対に供給するバイアス電流をn個の電流源のうち、n−m個の電流源から供給可能であって、n個の電流源が供給する電流は、予め定められた単位電流値を基準として、それぞれ重み付けがされている可変電流源と、出力波形の位相シフト量に基づいて、可変電流源のm個の電流源の数を変更する制御回路と、を備えている。

(もっと読む)

分周回路

【課題】分周回路の動作不良を抑制する。

【解決手段】第1又は第2のクロック信号に従って2×X個(Xは2以上の自然数)のパルス信号を生成して出力するシフトレジスタと、2×X個のパルス信号に従って、第1のクロック信号の周期のX倍の周期である第3のクロック信号となる信号を生成して出力する分周信号出力回路と、を具備し、分周信号出力回路は、ゲートのそれぞれに、2×X個のパルス信号における1個目乃至X個目のパルス信号のうち、互いに異なるパルス信号が入力され、第3のクロック信号となる信号の電圧を第1の電圧に設定するか否かを制御するX個の第1のトランジスタと、ゲートのそれぞれに、2×X個のパルス信号におけるX+1個目乃至2×X個目のパルス信号のうち、互いに異なるパルス信号が入力され、第3のクロック信号となる信号の電圧を第2の電圧に設定するか否かを制御するX個の第2のトランジスタと、を備える。

(もっと読む)

信号整形装置

【課題】高いクロック周波数に対応した高速動作が可能であると共に、高い精度でデューティ比を調節できる信号整形装置を提供すること。

【解決手段】所定パルス幅のパルス信号を生成するパルス信号生成部11と、パルス信号のデューティ比を制御するデューティ比調節部12と、を有する信号整形装置であり、パルス信号生成部11は、クロック信号が入力されるフリップフロップ回路101と、フリップフロップ回路101の出力信号を遅延させて当該遅延量に応じたパルス幅を有する単相のパルス信号を出力する遅延回路102と、を備え、デューティ比調節部12は、遅延回路102から出力される単相のパルス信号を互いに極性が反転した第1パルス信号と第2パルス信号からなる差動パルス信号に変換し、第1パルス信号の平均電圧と第2パルス信号の平均電圧との差に基づいて、パルス信号が目標のデューティ比になるように遅延回路102の遅延量を制御する。

(もっと読む)

クロック信号を電荷ポンプに提供するための方法および装置

信号処理装置

【課題】0と1の出現確率が異なるデータ信号のデューティサイクルの歪みを補正する。

【解決手段】位相検出回路21は、0と1の出現確率が異なるデータ信号の位相の進みおよび遅れを検出する。AND回路43はデータ信号の立ち上がりを検出し、AND回路44は立ち下がりを検出する。+DCD検出回路45は、位相検出回路21とAND回路43および44の検出結果に基づいて、デューティサイクルのプラス側の歪みを検出し、−DCD検出回路46は、デューティサイクルのマイナス側の歪みを検出する。デューティ調整回路12は、+DCD検出回路45と−DCD検出回路46の検出結果に基づいて、デューティサイクルを調整することにより、デューティサイクルの歪みを補正する。本発明は、例えば、データ信号を受信する受信装置に適用することができる。

(もっと読む)

クロックデューティ変更回路

【課題】PLL回路の構成に依存することなく汎用的に適用することができ、製造ばらつきによる出力クロック信号のデューティ比のずれを補償可能なクロックデューティ変更回路を提供する。

【解決手段】調整回路2は、デューティ比の目標値を指示する制御信号S[2:0]及び制御信号cntd[2:0]に基づいて決定される遅延時間だけ入力クロック信号PLLCKを遅延させた遅延信号lng及びshtを生成する遅延選択回路20及び21と、lng及びshtとPLLCKとを用いた論理演算により出力クロック信号PLLDを生成する演算回路23及び24とを有する。また、比較回路4は、PLLDのデューティ比が目標値と一致するか否かを判定する。さらに、補正回路3は、比較回路4による判定結果に応じて、PLLDのデューティ比と目標値とのずれを減少させるようlng及びshtに与えられる遅延時間の補正量を示すcntd[2:0]を生成する。

(もっと読む)

信号伝送回路、CMOS半導体デバイス、及び回路基板

【課題】大規模集積回路内に形成される長い信号線路或いは接続される被駆動回路の数が多数存在する等により形成される静電容量の容量値が大きい信号線路の信号伝送特性を改善する。

【解決手段】駆動回路及び被駆動回路の電源電圧の中点電圧を出力し、出力インピーダンスが低い付加回路を信号線路に接続し、信号線路の電位を電源電圧の中点電圧に維持すると共に、駆動回路から出力される駆動信号を中点電圧(被駆動回路の閾値電圧)を中心に小振幅で励振させ、この小振幅に制限された駆動信号により被駆動回路を駆動させる。

(もっと読む)

クロックデューティ自動補正回路及びそれを用いたクロックデューティ自動補正方法

【課題】 外部信号を用いずにクロック信号のデューティを正確に測定及び自動補正する。

【解決手段】 半導体装置30には、クロックデューティ自動補正回路1及びPLL回路2が設けられている。クロックデューティ自動補正回路1は、クロック測定部11、クロックデューティ特定部12、及びクロック生成部13から構成され、PLL回路2から出力されるデューティ比が変化した補正前クロック信号CLKAが入力される。補正前クロック信号CLKAのデューティがクロック測定部11で測定され、クロックデューティ特定部12でデューティが特定される。クロックデューティ特定部12から出力されるクロック切り替え信号SCLKS2と遅延選択信号SDS2をもとにして、クロック生成部13で補正前クロック信号CLKAのデューティ比の自動補正が外部信号を用いずに行われる。

(もっと読む)

パルス信号発生器及びクロック信号発生器

【課題】発振の成長初期におけるパルス信号のスパイク状波形による悪影響を除去し得るパルス信号発生器及びクロック信号発生器を提供する。

【解決手段】クロック信号CLKの平均の直流電圧値Vdutyが所定の基準値VRを超えたことを検出してこのことを表す第1の状態信号Dinを形成する比較器17と、第1の状態信号Dinが立ち上がった後にブロックしていたクロック信号CLKを出力するDフリップフロップ回路18及びナンドゲート回路14からなる論理回路とを有する。

(もっと読む)

I2Cクロックの生成方法及びシステム

I2Cクロック生成器を、多様な方法を用いてインプリメントする。そのような方法の1つを使用して、I2Cバス上のクロック信号(110)を制御するためのステートマシンに配置される論理回路を用いる方法をインプリメントする。ステートマシンの第1の状態(202)は、クロックストレッチング遅延を実行するか否かを判定する。ステートマシンの第2の状態(206)は、前記I2Cバスが、標準クロックモードにおいてか、または、他の複数の高速クロックモードのうちの1つで動作するように設定されているか否かを判定する。ステートマシンの第3の状態(210)は、クロック信号を一方の2値論理状態で駆動させる前に、クロック信号を、約0.5マイクロ秒以上で、約2.5マイクロ秒未満の間、他方の2値論理状態で駆動させ、そして、クロック信号を、約0.5マイクロ秒以上で、約2.5マイクロ秒未満の間、前記一方の2値論理状態のままにする。  (もっと読む)

(もっと読む)

半導体集積回路及びそれを用いたデューティ測定・補正方法

【課題】 外部信号を用いずにクロック信号のデューティを正確に測定及び補正する。

【解決手段】 半導体装置20には、半導体集積回路としてのデューティ測定・補正回路1及びPLL回路4が設けられている。デューティ測定・補正回路1は、デューティ測定回路部2及びデューティ補正回路部3から構成され、デューティ比が変化した補正前クロック信号CLKAが入力される。デューティ測定回路部2から出力される信号Outが“Low”レベルから“High”レベルに変化したときのデューティ測定回路部2の遅延回路の遅延時間が補正前クロック信号CLKAのデューティとして、デューティ測定回路部2で測定される。このとき、デューティ測定回路部2の遅延回路と対をなすデューティ補正回路部3の遅延回路が選択されて、補正前クロック信号CLKAのデューティがデューティ補正回路部3で補正される。

(もっと読む)

クロックのデューティ調整回路、これを用いた遅延固定ループ回路及びその方法

【課題】スキューによるクロックのデューティの偏差を減少させる。

【解決手段】立ち上がりクロック用ミキサーと下がりクロック用ミキサーとクロック選択器とを含むデューティー調整回路を提供し、立ち上がりクロック用ミキサーは、印加される第1及び第2位相固定状態信号を用いて、立ち上がりクロックのデューティ調整を行うためのデューティ調整イネーブル信号と、立ち上がりクロックと下がりクロックとの位相の混合率を決定するための比重選択信号とを用いて立ち上がりクロックと下がりクロックとの位相を混合し、下がりクロック用ミキサーは、デューティイネーブル信号と前記比重選択信号とを用いて前記立ち上がりクロックと下がりクロックとの位相を混合し、クロック選択器は、比重選択信号により、立ち上がりフィードバック前置クロック信号と下がりフィードバック前置クロック信号を選択する。

(もっと読む)

クロック切り替え装置及びクロック切り替え方法

【課題】装置の処理を中断することなく自動的にバックアップ用のクロック分配系に切り替えることのできる、クロック切り替え装置及びクロック切り替え方法を提供する。

【解決手段】第1のクロック分配系CIN0のあるクロックパルスT0とその1周期前のクロックパルスT0’の位相を合わせる第1の検出用位相調整手段1と、クロックパルスT0とT0’の論理レベル(HIGH/LOW)が一致しているかどうかチェックし、不一致の場合ALM0をHIGHにする第1の異常検出手段2と、第2のクロック分配系CIN1のあるクロックパルスT1とその1周期前のクロックパルスT1’の位相を合わせる第2の検出用位相調整手段3と、切替信号生成手段6と、切替手段7を有する。

(もっと読む)

可変遅延回路網

入力データ信号を集積回路上の他の回路網に提供するための回路網は、粗遅延チェーンおよび微遅延チェーンを含む。これらの2つの遅延チェーンは、カスケードにすることが可能であり、必要に応じて、非常に広い範囲の可能な遅延量を提供する。これらの遅延量は、微遅延チェーンを使用することによって、細かく段階付けされ得る。これらの遅延チェーンを含む可変遅延回路網は、プログラマブルロジックデバイス(「PLD」)などで、有益に使用される。  (もっと読む)

(もっと読む)

オンデマンド電力管理の方法及び機器

【課題】電力管理、特に、アプリケーション処理要求に応答した電圧及び周波数の管理の技術を提供する。

【解決手段】システムコントローラと、システムコントローラに結合されたクロック領域マネージャと、システムコントローラに結合された配電マネージャとを含むオンデマンド電力管理のための機器。システムコントローラは、処理システム内の処理要求をモニタする。クロック領域マネージャは、1つ又はそれよりも多くのクロック周波数を供給し、処理要求に応答して、処理システムを停止することなくクロック周波数の第1の組とクロック周波数の第2の組の間で切り換える。配電マネージャは、1つ又はそれよりも多くの作動電圧を供給し、処理要求に応答して、処理システムを停止することなく電圧の第1の組と電圧の第2の組の間で切り換える。

(もっと読む)

半導体集積回路

【課題】 半導体集積回路の動作に起因するクロック信号の乱れを除去する。

【解決手段】 クロック信号CLKは、入力バッファ10で反転されてマスク信号S70と共にNAND20に与えられる。NAND20の信号S20が立ち上がると、積分部30,40の積分回路による遅延時間の後、この積分部40の信号S40が立ち下がる。信号S20は信号S40と共にNAND50に与えられるので、このNAND50の信号S50は、クロック信号CLKの立ち上がり時点から積分回路による遅延時間の間、“L”に固定される。信号S50は積分部60で遅延され、AND70で積分部60の遅延時間が追加されてマスク信号S70が生成される。一方、信号S50は、インバータ80で反転され、内部クロックCKIとしてデータ入力部1、データ処理部2及びデータ出力部3に供給される。

(もっと読む)

プログラマブルコントローラ

【課題】 システムバス上の個々のモジュールに接続されるコネクタの直近にバッファ回路を設けることにより、システムバス上に接続されるモジュール増減による負荷容量の影響をなくしたプログラマブルコントローラを提供する。

【解決手段】 プログラマブルコントローラは、個々のモジュールが接続され、整列配置してなる複数のコネクタと、システムバスを通して複数のコネクタの夫々にクロック信号を分配するクロック駆動回路と、を備えたプログラマブルコントローラであって、複数のコネクタの夫々に、クロック信号をプルアップするプルアップ手段、即ち、夫々のコネクタの直近にバッファ回路を配置し、このバッファ回路を通してから複数のコネクタの夫々にクロック信号を供給する構成にしたことである。

(もっと読む)

グリッチを誘発しないクロックスイッチング回路

【課題】 グリッチを誘発しないクロックスイッチング回路を提供する。

【解決手段】 速いクロックから遅いクロックへのクロックスイッチングを指示する選択信号をクロックスイッチング信号として直ぐ使用せず、速いクロックから遅いクロックへの転換が2回にわたる同期化作業を通じて得られる選択遅延信号に基づいて出力クロックを発生させ、遅いクロックから速いクロックへのクロックスイッチング時、遅いクロックから速いクロックへの転換が3回にわたる同期化作業を通じて得られる選択遅延信号に基づいて出力クロックを出力するクロックスイッチング回路である。これにより、出力クロックにグリッチが発生しない。

(もっと読む)

クロック信号の補正に適したクロック信号入出力装置

本発明は、クロック信号入出力装置(1、101)に加えて、クロック信号補正方法に関するものである。本発明の方法では、クロック信号(clk)または該クロック信号から得られた信号を、上記装置に入力し、分周器(4、104)に伝送し、分周器(4、104)から出力された信号、または、該信号から得られた信号(clk2)を、信号積分器(6、106)に伝送し、該信号積分器(6、106)から出力されるか、または、該信号から得られた信号(I2)を、第1信号比較回路(8、108b)に伝送する。さらに、分周器(4、104)から出力された信号、または、該信号から得られた信号(clk2)を、第2信号比較回路(9、109a)に伝送し、クロック信号用の入出力装置(1)は、第1信号比較回路(8、108)から出力された、または、該信号から得られた信号(rIclk)に応じて、および、第2信号比較回路(9、109a)から出力された、または、該信号から得られた信号(rclk)に応じて、クロック出力信号(clk50)を出力するための、信号出力回路(11、111)を備えている。  (もっと読む)

(もっと読む)

1 - 20 / 22

[ Back to top ]