Fターム[5B083BB01]の内容

計算機における入出力系RAS (2,172) | RAS動作 (543) | 検出、監視 (176)

Fターム[5B083BB01]に分類される特許

1 - 20 / 176

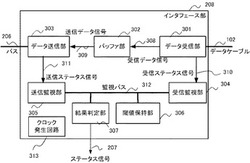

インタフェース装置及びその制御方法

【課題】 一方のインタフェースのみのパフォーマンスを測定するだけでは性能低下の原因を特定することができない。

【解決手段】 第1機器と第2機器との間に介在するインタフェース装置及びその制御方法であって、第1機器からの第1制御信号に応じて第1機器からデータを受信し、第2機器からの第2制御信号に応じてデータを第2機器に出力する。これら第1及び第2制御信号の状態を監視し、その監視された第1及び第2制御信号の状態に応じて、第1機器或いは第2機器のいずれの性能が低下しているかを判定する。

(もっと読む)

データ転送制御装置

【課題】連続的で高速なデータ転送に起因する、データ転送停止や回路の異常発熱を回避することが可能なデータ転送制御装置を実現する。

【解決手段】データ転送制御装置(20)は、ホスト装置とのデータのやりとりを行うことが可能なホストインターフェース部(24)と、周辺装置とのデータのやりとりを行うことが可能な周辺装置インターフェース部(21)と、ホストインターフェース部または周辺装置インターフェース部の異常状態を検出する異常検出部(25)と、異常検出部が異常を検出した場合に、ホストインターフェース部または周辺装置インターフェース部でのデータ転送を中断し、その後、異常検出部がホストインターフェース部または周辺装置インターフェース部の正常状態への回復を検出した場合に、ホストインターフェース部または周辺装置インターフェース部でのデータ転送動作を再開する転送制御部(25)とを備える。

(もっと読む)

半導体集積回路

【課題】デバッグを効率的に行なうことができる半導体集積回路を提供する。

【解決手段】受信されたパケットをその宛先に応じて分配する分配部と、自身に分配されたパケットを各々が順次蓄積する複数の蓄積部と、中継許可指令に応じて当該蓄積部のうちの対応する1つに蓄積されているパケットを対応する1つの処理部に各々が供給する複数の中継部と、自身に分配されたパケットが中継許可パケットであると判別した場合に当該中継部のうちの当該中継許可パケットによって指定された1つに対して当該中継許可指令を与える出力制御部と、を含む半導体集積回路。

(もっと読む)

プリンタ装置、通信システム、通信方法

【課題】USBインターフェースにおける通信エラーを容易に検出・修正することのできる通信システム及び通信方法、並びに当該通信システムに用いられるプリンタ装置を提供すること。

【解決手段】本プリンタ装置20は、ホスト10と接続されたUSBケーブル30が接続される接続部22と、ホスト10から定期的に送信され、USBケーブル30の通信状態が正常であることを示すピング信号を、接続部22を介して受信する受信部26と、ピング信号が一定時間以上受信されない場合に、USBケーブル30を一度未接続状態に切り替えた後、再度接続状態に切り替える再接続設定を行う制御部26と、を備える

(もっと読む)

半導体装置、それを用いた無線通信端末、及び電源制御方法

【課題】従来の半導体装置は、消費電力が大きくなる問題があった。

【解決手段】半導体装置1は、プログラムとプログラムによって利用されるデータとの少なくとも一方が格納される記憶領域部16と、プログラムを実行して記憶領域部16にバスを介してアクセス要求を発行する機能ブロック11と、バス23上に流れる、記憶領域部16に対するアクセス要求を示す第1の信号REQと、記憶領域部16によるバス23の占有状態を示す第2の信号GNTと、を監視して記憶領域部16へのアクセスが発生していない期間は記憶領域部16をスタンバイ状態に制御し、記憶領域部16へのアクセスが発生している期間は記憶領域部16を活性状態に制御するバス状態監視回路20と、を有し、記憶領域部16は、プログラム又はデータを記憶する記憶セルの低電位側電源電圧と高電位側電源電圧との電圧差を前記スタンバイ状態において活性状態よりも小さくする。

(もっと読む)

マルチコアLSI

【課題】動作の安定性を向上できるマルチコアLSIを提供する。

【解決手段】このマルチコアLSI1は、第1の共有バスb1に接続された複数のCPU#0,#1と、第2の共有バスb2に接続された1個以上のモジュールm1〜mnと、第1の共有バスb1と第2の共有バスb2との間に接続され、複数のCPU#0,#1のモジュールへのアクセスを調停する共有バス制御部3と、アクセス先のモジュールから、CPU#0,#1のアクセス要求信号に対する応答信号が出力されたか否かを監視するシステムコントローラ9とを備え、システムコントローラ9は、共有バス制御部3から第2の共有バスb2にアクセス要求信号が出力されてから所定時間経過するまでに、アクセス先のモジュールから応答信号が出力されない場合は、共有バス制御部3を介して第1の共有バスb1に疑似応答信号を出力して、アクセス中のCPUの当該アクセスを終了させる。

(もっと読む)

1553バス動作の自己検査のためのシステムおよび方法

【課題】1553バス動作の自己検査のためのシステムおよび方法を提供する。

【解決手段】1553自己検査論理は、1553バストランシーバと自己検査プロセッサペアとのデータ通信を管理する。1553自己検査論理は、ロックステップで動作する一次論理および二次論理を含む。1553自己検査論理が1553バストランシーバにデータを書き込むとき、1553自己検査論理は、一次論理によって生成された第1の1553フォーマット済みメッセージを、二次論理によって生成された第2の1553フォーマット済みメッセージと比較し、第1の1553フォーマット済みメッセージが第2の1553フォーマット済みメッセージと一致しないときに、エラー表示を生成する。

(もっと読む)

デバイス制御装置及び方法、クライアント装置、並びにデバイス制御システム

【課題】クライアント装置によるデバイスの監視処理を不要とし、ネットワーク上のトラフィックを低減することができるデバイス制御装置を提供する。

【解決手段】デバイス300がローカル接続されるデバイスサーバ200は、ネットワーク500を介してクライアントPC100に接続される。デバイスサーバ200は、デバイス300の状態を監視するための定義ファイル及びトリガ検知アルゴリズムを用いてデバイス300を監視し、この状態変化を検知したときに、この検知を示すトリガ通知をクライアントPC100に送信する。デバイスサーバ200は、さらに、トリガ通知を受信したクライアントPC100とセッションを開始して、この状態変化を検知したデバイスとのデータ通信を中継し、クライアントPC100とのセッションが切断されたとき、デバイス300の状態の監視を再開させる。

(もっと読む)

情報処理装置、制御装置および異常ユニット判定方法

【課題】I2Cバスに接続されたI2Cユニットに異常があった場合、どのI2Cユニットに異常があるのかを判定できる。

【解決手段】I2Cバス装置9は、I2Cバスで接続する複数のI2Cスレーブユニット3を制御するI2Cマスタユニット1Aと、複数のI2Cスレーブユニット3を制御し、I2Cマスタユニット1Aと二重化されたI2Cマスタユニット2とを有し、I2Cマスタユニット1Aは、自ユニットと接続されたI2Cスレーブユニット3へのアクセスで異常を検出したとき、異常を検出した箇所に関するアクセス結果と、I2Cマスタユニット1Bと接続されたI2Cスレーブユニット3へのI2Cマスタユニット1Bからのアクセス結果とを用いて、異常となるユニットを判定する制御部30を有する。

(もっと読む)

データ転送装置およびフィールド機器

【課題】定期的に到来する所定のデータをDMA転送するデータ転送装置において、システムのパフォーマンスを維持しつつ(CPUの処理能力を奪うことなく)、転送障害が発生した場合に迅速にそれを検出する。

【解決手段】データ転送装置(マイコン110が相当する)の代表的な構成は、定期的に到来する所定のデータ(物理量データ)の転送要求に基づいてそのデータを転送するDMAコントローラ116と、その転送要求に基づいて時間の経過を計測するデータ転送監視回路120内のタイマと、タイマのタイムアウトを検出するタイムアウト検出回路とを備え、データ転送が完了するまでの時間を監視し、その時間内にデータ全体の転送が完了しなければ、タイムアウトが発生するので、転送障害が発生したものとしてエラーを出すようにした。

(もっと読む)

データ送信装置、データ受信装置、データ送受信装置及びデータ送受信装置の制御方法

【課題】複数の伝送路を用いてデータの送受信を行うシステムの運用中に、エラーが発生した伝送路を特定する技術を提供する。

【解決手段】送信側は、レーン毎に、そのレーンで送信したデータを用いてCRC符号を計算し、レーン毎に計算したCRC符号を格納したDLLPを送信する。受信側は、レーン毎に、そのレーンで受信したデータを用いてCRC符号を計算し、DLLPを受信すると、そのDLLPに格納されたCRC符号を、計算したCRC符号とレーン毎に比較する。それにより、システムの運用中であってもエラーが発生したレーンを受信側が検出可能にする。

(もっと読む)

異常検出回路及び回路の異常検出方法

【課題】回路面積の増大を抑制することができる異常検出回路及び回路の異常検出方法を提供すること

【解決手段】本発明にかかる異常検出回路4は、複数の入力信号に対応した複数の出力信号を出力するバッファ群3に設けられる。異常検出回路4は、複数の入力信号に基づく固有信号MISROUT1を生成するMISR回路5と、複数の出力信号に基づく固有信号MISROUT2を生成するMISR回路6と、両固有信号の不一致を検出して異常信号を特定する異常信号特定回路7を備える。異常信号特定回路7は、両固有信号の不一致を検出した場合、制御信号CAPTUREを生成し、MISR回路5、6は、当該制御信号に応じて、複数の入力信号、出力信号を異常信号特定回路7に順次出力する。異常信号特定回路7は、複数の入力及び出力信号との不一致を順次検出することによって、複数の入力及び出力信号における異常信号を特定する。

(もっと読む)

システム、ホスト装置及びエラー検出方法

【課題】端子の接触不良を検出する回路の故障を検出可能なシステム、ホスト装置及びエラー検出方法等を提供すること。

【解決手段】システムはホスト装置10と記憶装置20を含む。記憶装置20は、不揮発性の記憶部60と、不揮発性の記憶部60に対するアクセス制御を行うアクセス制御部36と、電源端子TV及びグランド端子TGの少なくとも一方のフローティング状態を検出する検出回路32と、を有する。ホスト装置10は、電源電圧VDD及びグランド電圧VSSのうちのフローティング状態が検出される検出対象電圧の供給・非供給を切り換える切り換え回路50と、検出対象電圧が非供給に設定された場合の記憶装置20からの信号に基づいて検出回路32が正常であるか非正常であるかを判定する判定部70と、を有する。

(もっと読む)

検証機能を有する半導体デバイス

【課題】内部バスの検証モジュールを有する半導体デバイスを提供する。

【解決手段】内部バスと、第1の接続点において前記バスに接続されたマスターと、第2の接続点において前記内部バスに接続され、前記マスターと通信可能に設けられたスレーブと、検証モジュールとを備えた半導体デバイス。前記検証モジュールは、前記マスターが前記スレーブに供給した制御信号を検出し、当該検出信号に基づいて、前記内部バスの通信量に関するデータを生成する。前記制御信号は、前記マスターが前記スレーブを制御するための信号であって、例えば、書き込み信号、読み出し信号、バースト信号等を含む。前記検証モジュールは、各制御信号がアサートされた回数に基づいて、前記内部バスの通信量に関するデータを生成してもよい。前記検証モジュールは、前記内部バスに接続された検証用マスター及び検証用スレーブをさらに有してもよい。

(もっと読む)

情報処理装置、その制御方法及びプログラム

【課題】汎用品のIPコアを使用した情報処理装置は、IPコアを含むデバイスとチップセットの間の通信が救済不可能な状態に遷移して初めて、デバイスとチップセット間の異常を検出することができる。つまり、救済不可能な状態に遷移する以前の救済可能異常状態を検出することができない。そのため、通信が不能に至る前の状態を検出し、必要な予防動作の実行が可能な情報処理装置が望まれる。

【解決手段】図1に示す情報処理装置は、IPコアと、パトロールパケットの送信を指示するパトロールパケット送受信部と、受信したパトロールパケットと同一性を維持した折り返しパトロールパケットをIPコアに対して送信するパトロールパケット返信部と、を備えている。パトロールパケットが処理される時間と閾値を比較することで、パケット通信の状態を判断し、予防動作の実行を実現する。

(もっと読む)

電子装置、集積装置、情報処理システム、および、処理方法

【課題】信頼性を向上させる。

【解決手段】電子装置は、第1のバスとは直接に接続され、第2のバスとは前記第2のバスに接続される第2の電子装置を経由して接続され、前記第1のバス、および、第2のバスに接続される第3の電子装置からのアクセスを、前記第1のバスから直接に、または、前記第2のバス、かつ、前記第2の電子装置を経由して受け取る。

(もっと読む)

PCIバス制御システム

【課題】イニシエーターとターゲットとをPCIバスにより接続したPCIバス制御システムに関し、コマンドエラーを回避する。

【解決手段】

イニシエーター1とターゲット2−1,2−2との間をPCIバスにより接続したPCIバス制御システムであって、監視回路3と救済回路4とを設け、PCIバスによりイニシエーター1とターゲット2−1,2−2間を監視回路3と救済回路4とを介して接続すると共に、イニシエーター1と監視回路3と救済回路4との間を、コマンドCOMMとパリティPARとパリティエラーPERRとを転送するローカルバスにより接続し、監視回路3によりコマンドのパリティチェックを行って送出し、救済回路4は、PCIバスとローカルバスとを介してそれぞれ転送されたコマンドについて、正常な側を選択して、ターゲット2−1,2−2にコマンドを転送する構成を備えている。

(もっと読む)

データ転送装置およびストレージ装置

【課題】非ハンドシェイク型の通信を行っている装置においてデータの送達を確認することができるデータ転送装置およびストレージ装置を提供する。

【解決手段】送信素子と、受信素子と、監視素子とを備え、送信素子は、非ハンドシェイク型の通信でデータを送信し、受信素子は、送信素子から送信されたデータを受信し、監視素子は、受信素子とは別に設けられたものであって、受信素子によって受信されるデータのサイズを監視して監視結果を送信素子に通知する。

(もっと読む)

電子端末装置及び電子連動装置

【課題】CPUから入出力のポートを指定する出力用アドレスバスと入力用アドレスバスのアドレスバスを共通化してアドレスバスのいずれかのビットに生じた固定故障を確実に検知する。

【解決手段】 出力用アドレスデコーダ13及びフィードバック用アドレスデコーダ14とCPU11との間を共通のアドレスバス18で接続し、出力用アドレスデコーダ13の制御出力端子を指定するアドレスとそれに対応するフィードバック用アドレスデコーダ14の制御出力端子を指定するアドレスはデコード順を逆に設定して、アドレスバス18のいずれかのビットが「0」又は「1」に固定故障すると正常と異なる入力ポート16をCPU11で読み取り、アドレスバス18の固定故障を確実に検知する。

(もっと読む)

電子機器装置

【課題】上位装置と電子機器装置(下位装置)との通信構成を複雑化させることなく電子機器装置の自己復旧によって動作安定性を向上させた電子機器装置を提供する。

【解決手段】電子機器装置30は、その動作の制御機能を有するメインCPU32と、その動作状態の監視機能を有するサブCPU36と、メインCPU32と上位装置10との間で、各種データの送受信を行う汎用性通信接続21と、サブCPU36と上位装置10との間で、この電子機器装置の動作状態を示す動作状態信号を通信する汎用性通信接続22と、を有する。また、メインCPU32とサブCPU36との間で互いにソフトウェアの更新機能を有する。

(もっと読む)

1 - 20 / 176

[ Back to top ]