Fターム[5B125BA05]の内容

リードオンリーメモリ (43,397) | メモリ種別 (5,638) | EEPROM、フラッシュ (3,956) | SGを有する (139)

Fターム[5B125BA05]に分類される特許

1 - 20 / 139

不揮発性半導体メモリ素子、および不揮発性半導体メモリ装置

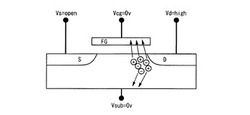

【課題】フローティングゲートへの電荷の蓄積と消去を容易に行え、またフローティングゲートの電荷を消去する場合にメモリセルの閾値を容易に制御できる、不揮発性半導体メモリ素子を提供する。

【解決手段】フローティングゲートへの電荷の蓄積時に、フローティングゲートとドレイン(またはソース)間に電圧を印加し、バンド・バンド間によるホットエレクトロンを半導体基板中に発生させ、フローティングゲートに電荷を注入する。また、フローティングゲートの電荷の消去時には、フローティングゲートとドレイン(またはソース)間に電圧を印加し、バンド・バンド間によるホットホールを発生させ、該ホットホールにより蓄積された電荷を消去する。また、フローティングゲートの電荷の消去時には、メモリセルのコントロールゲートとソース間の閾値が所望の値になるように制御しながら、電荷を消去する。

(もっと読む)

半導体装置

【課題】電荷捕獲型の場合であっても高速にプログラムすることが可能な不揮発性メモリを備えた半導体装置を提供する。

【解決手段】半導体装置において、メモリアレイは、行列状に配列され、各々が閾値電圧のレベル変化によってデータを記憶する複数のメモリセルMC0,MC1を含む。ベリファイ回路50は、プログラム対象のメモリセルに対して複数回実行されるプログラム動作ごとに、閾値電圧がプログラムベリファイ電圧に到達したか否かを判定する。電流調整回路52は、プログラム対象の複数のメモリセルのうち、ベリファイ回路50によって閾値電圧がプログラムベリファイ電圧に達していないと判定されたメモリセルには第1の電流値のプログラム電流を流し、閾値電圧がプログラムベリファイ電圧に達したと判定されたメモリセルには第1の電流値よりも小さい第2の電流値のプログラム電流を流す。

(もっと読む)

不揮発性半導体記憶装置

【課題】高速で動作し得る不揮発性半導体記憶装置を提供する。

【解決手段】選択トランジスタとメモリセルトランジスタMTとを有するメモリセルMCがマトリクス状に配列されて成るメモリセルアレイ10と、ビット線BLの電位を制御する列デコーダ12と、第1のワード線WL1の電位を制御する電圧印加回路14と、第2のワード線WL2の電位を制御する第1の行デコーダ16と、ソース線SLの電位を制御する第2の行デコーダ18とを有し、列デコーダは電圧印加回路及び第2の行デコーダより耐圧の低い回路により構成されており、第1の行デコーダは電圧印加回路及び第2の行デコーダより耐圧の低い回路により構成されている。ビット線と第2のワード線とが高速で制御され得るため、メモリセルトランジスタに書き込まれた情報を高速で読み出すことができる。

(もっと読む)

双方向分割ゲートNANDフラッシュメモリ構造及びアレイ、そのプログラミング方法、消去方法及び読み出し方法、並びに、製造方法

【課題】NANDフラッシュメモリ構造において、各セルについてのライン数を削減して、不揮発性メモリデバイスのピッチを改善すること。

【解決手段】分割ゲートNANDフラッシュメモリ構造が、第1伝導型の半導体基板上に形成される。このNAND構造は、第2伝導型の第1領域と、基板内にこの第1領域から間隔をおいて配置されてこの第1領域との間にチャネル領域を定める、第2伝導型の第2領域と、を備える。各々が上記チャネル領域から絶縁された複数の浮動ゲートが、互いに間隔をおいて配置される。各々が上記チャネル領域から絶縁された複数の制御ゲートが、互いに間隔をおいて配置される。該制御ゲートの各々は、1対の浮動ゲートの間にあって該1対の浮動ゲートに容量的に接続される。各々が上記チャネル領域から絶縁された複数の選択ゲートが、互いに間隔をおいて配置される。該選択ゲートの各々は、1対の浮動ゲートの間にある。

(もっと読む)

制御信号発生回路およびそれを用いた半導体装置

【課題】半導体装置の制御に好適な制御信号発生回路を提供する。

【解決手段】ジョンソンカウンタ31は、フリップフロップFF1〜FF4およびゲート回路41〜44を含み、順次入力されるスタート信号ST1〜ST4に応答してそれぞれ制御信号C1〜C4を「H」レベルにした後、順次入力されるストップ信号SP1〜SP4に応答してそれぞれ制御信号C1〜C4を「L」レベルにする。したがって、多数のフリップフロップを用いることなく、所望の時間間隔で制御信号C1〜C4を順次「H」レベルにし、順次「L」レベルにすることができる。

(もっと読む)

バイト、ページおよびブロックに書き込むことができ、セルアレイ中で干渉を受けず分割が良好な特性を備え、新規のデコーダ設計とレイアウトの整合ユニットと技術を使用する単体式複合型不揮発メモリ

【課題】

バイト、ページおよびブロックで書き込むことができる新単体式複合型不揮発メモリを提供する。

【解決手段】

不揮発メモリアレイは、シングルトランジスタフラッシュメモリセルおよびダブルトランジスタEEPROMメモリセルを備え、同じ基板上に整合することができ、該不揮発メモリセルは低いカップリング係数の浮遊ゲートを備えて、メモリセル体積を減少でき、該浮遊ゲートをトンネル絶縁層の上に配置し、該浮遊ゲートは該ソース領域の辺縁および該ドレイン領域の辺縁に揃って、且つ該ソース領域辺縁および該ドレイン領域辺縁の幅に画定される幅を備え、該浮遊ゲートと該制御ゲートは50%より小さい相対的に小さなカップリング係数を備えて、該不揮発メモリセルを縮小できるようにし、該不揮発メモリセルのプログラムはチャネル熱電子方式で達成し、消去は高電圧でFNトンネル方式で達成する。

(もっと読む)

不揮発性記憶装置およびその制御方法

【課題】ツインセルを備えた不揮発性記憶装置において、ベリファイセンスアンプを設けることなく、イニシャル状態におけるツインセルデータの読み出しを可能とすること。

【解決手段】外部から入力されたデータを相補データとして格納する第1のメモリセルおよび第2のメモリセルと、第1のメモリセルおよび第2のメモリセルのコントロールゲートにそれぞれ接続された第1のワード線および第2のワード線とを備え、第2のワード線に第1のワード線に供給された電圧よりも高い電圧を供給する場合と、第2のワード線に第1のワード線に供給された電圧よりも低い電圧を供給する場合との間で、第1のメモリセルから読み出されたセル電流と第2のメモリセルから読み出されたセル電流の大小関係が反転するか否かに基づいて、第1のメモリセルおよび第2のメモリセルに同一の値が格納されているか否かを判別する。

(もっと読む)

不揮発性半導体記憶装置および記憶方法

【課題】メモリユニットの過消去/過書込を回避するとともに書込時間を短縮する。

【解決手段】メモリ制御回路は、メモリユニット(MU11)に格納されたデータ値を読み出すリード動作を実行し、リード動作によって読み出されたデータ値の反転値(XRD1)がメモリユニット(MU11)に書き込まれるようにメモリユニット(MU11)の第1および第2のフローティングゲートの電荷量を制御する反転書込動作を開始し、メモリユニット(MU11)への反転値(XRD1)の書き込みが完了する前に反転書込動作を終了し、メモリユニット(MU11)に書き込むべき書き込みデータ値(WD1)がメモリユニット(MU11)に書き込まれるようにメモリユニット(MU11)の第1および第2のフローティングゲートの電荷量を制御する通常書込動作を実行する。

(もっと読む)

不揮発性半導体記憶装置

【課題】面積の縮小を図る。

【解決手段】不揮発性半導体記憶装置は、複数のメモリストリング200を具備し、各メモリストリングは、一対の柱状部A、および一対の柱状部の下端を連結させるように形成された連結部Bを有する半導体層SPと、柱状部に直交したコントロールゲートCGと、一対の柱状部の一方と直交し、コントロールゲートの上方に形成された第1選択ゲートSGSと、一対の柱状部の他方と直交し、コントロールゲートの上方に形成され、第1選択ゲートと同一レベルでかつ一体である第2選択ゲートSGDと、柱状部とコントロールゲートとの各交差部に形成されたメモリセルトランジスタMTrと、柱状部と第1選択ゲートとの交差部に形成された第1選択トランジスタSSTrと、柱状部と第2選択ゲートとの交差部に形成された第2選択トランジスタSDTrと、を含む。

(もっと読む)

記憶装置、半導体装置

【課題】データの書き込み不良を抑えつつ、面積を小さく抑えることができる不揮発性の記憶装置、または当該不揮発性の記憶装置を用いた半導体装置の提供を目的の一とする。

【解決手段】不揮発性の記憶素子を有する第1の記憶部と、上記第1の記憶部へのデータの書き込みが正確に行われたかどうかを検証するベリファイ動作において、上記データを一時的に保存するための第2の記憶部(データバッファ)とを有する。そして、第2の記憶部が、記憶素子と、当該記憶素子における電荷の保持を制御するための、オフ電流またはリーク電流が極めて小さい絶縁ゲート電界効果型トランジスタとを有する。

(もっと読む)

不揮発性半導体記憶装置

【課題】ホットキャリア注入によって書き換えを行うスプリットゲート型MONOSメモリにおいて、リテンション特性を向上させる。

【解決手段】メモリセルM00の選択ゲート電極は選択ゲート線SG0に接続され、メモリゲート電極はメモリゲート線MG0に接続される。また、ドレイン領域はビット線BL0に接続され、ソース領域はソース線SL0に接続される。さらに、メモリセルM00が形成されたp型ウエル領域にはウエル線WL0が接続される。メモリセルM00に書き込みを行うときは、ウエル線WL0を通じてp型ウエル領域に負電圧を印加しながら、ソースサイド注入方式による書込みを行う。

(もっと読む)

チャネル熱電子注入プログラミング方法及び関連する装置

【課題】 本発明は、チャネル熱電子注入プログラミング方法及び関連する装置を提供する。

【解決手段】 プログラミング電流を低減し、信頼性を向上させる不揮発性メモリ素子は、メモリ・セル・アレイ、書き込み回路、及び検証回路を有する。メモリ・セル・アレイは、メモリ・セル・アレイのビット線とワード線のマトリックスの交点に配置されたメモリ・セルを有する。書き込み回路は、プログラミングのために各ワード線に複数の可変パルスを提供する。複数の可変パルスは、プログラミング動作中の伝導電流を低減しながら、ゲート注入電流をほぼ最大値に維持するため所定の大きさを有している。検証回路は、プログラミング動作中の伝導電流の変化を検知し、該検知されたプログラミング動作中の伝導電流が所定値に達した場合に、前記プログラミング動作を停止する。

(もっと読む)

半導体メモリおよびシステム

【課題】 プログラム動作時にソース線の電圧を低下させるリーク電流を遮断し、プログラム動作時間を短縮する。

【解決手段】 半導体メモリは、マトリックス上に配置され、制御ゲート線、選択ゲート線、ビット線およびソース線に接続された複数の不揮発性のメモリセルおよびソース線制御部を有する。制御ゲート線、選択ゲート線およびソース線は、第1方向に並ぶメモリセルの列にそれぞれ接続されている。ビット線は、第2方向に並ぶ選択トランジスタの列にそれぞれ接続されている。ソース線制御部は、プログラム動作時に、データがプログラムされるメモリセルを含むメモリセルの列に接続されたソース線を高レベル電圧に設定するとともに、データがプログラムされないメモリセルの列に接続されたソース線を選択ゲート線の低レベル電圧より高く、かつ非選択のビット線の高レベル電圧より低く設定する。

(もっと読む)

半導体装置

【課題】トランジスタの劣化を抑制することが可能で、レイアウト面積が小さな半導体装置を提供する。

【解決手段】この不揮発性半導体記憶装置では、選択されたメモリゲート線MG0に対応するメモリゲートドライブ回路MGD0のPチャネルMOSトランジスタ44のゲートに書込電圧(10V)と基準電圧(0V)の間の制御電圧(4V)を印加するとともにNチャネルMOSトランジスタ46のゲートに基準電圧(0V)を印加して、そのメモリゲート線MG0に書込電圧を印加する。したがって、従来よりも低いゲート−ソース間電圧でトランジスタ44,46を導通させるので、トランジスタ44,46の劣化を抑制できる。

(もっと読む)

半導体記憶装置

【課題】スプリットゲート型のMONOSメモリセルを有する半導体記憶装置において、SSI方式による書込み時のディスターブ耐性を向上させる。また、非選択メモリセルのディスターブ耐性が向上することにより、メモリモジュールの面積を低減させる。

【解決手段】メモリゲート電極12の側面において、電荷蓄積膜9と絶縁膜11との間に絶縁膜10を形成し、メモリゲート電極12側面の絶縁膜10および11の合計の厚さを、メモリゲート電極12下部の絶縁膜11の厚さよりも厚く形成する。

(もっと読む)

フラッシュメモリ

【課題】不揮発性メモリセルに複数の閾値電圧を記憶し、前記閾値電圧をワード線に印加した複数のワード線選択レベル電圧を用いて読み出すフラッシュメモリの温度補償回路を単純化する。

【解決手段】基準電圧を発生する電源回路を有し、前記複数のワード線選択レベル電圧を発生する複数の電圧発生回路を、比較器と、チャージポンプ回路と、複数の拡散抵抗素子を直列に接続した分圧回路で構成し、前記基準電圧を前記比較器の負側入力端子に接続し、前記比較器の出力端子を前記チャージポンプ回路の入力端子に接続し、前記チャージポンプで昇圧した出力電圧を前記ワード線と前記分圧回路に接続し、前記分圧回路から引き出した分圧電圧を前記比較器の正側入力端子に接続し、前記複数の電圧発生回路の前記分圧電圧の温度による電圧変化率(温度勾配)を等しくし、前記電源回路が前記温度勾配を有する前記基準電圧を発生する。

(もっと読む)

不揮発性半導体記憶装置

【課題】プログラム時、プログラム条件やばらつき要因に関わらず、精度のよいプログラム電圧を供給することが可能な不揮発性半導体記憶装置を提供すること

【解決手段】メモリセルのソース端子が接続されるソース線を選択して書換え電圧を供給する第1スイッチと、ソース線に供給される書換え電圧を検出する電圧検出線と、第1スイッチにより選択されるソース線を電圧検出線に接続する第2スイッチと、を備えている。書き換え時に第1スイッチを介して流れる書換え電流による電圧降下の影響を考慮することなく、ソース線に供給されている書換え電圧を検出することができる。検出される電圧は、メモリセルのソース端子に印加される電圧であり、書き換え時にメモリセルに印加される書換え電圧を精度良く検出することができる。

(もっと読む)

半導体記憶装置

【課題】不揮発性半導体記憶装置を安定に動作させるための動作方式を提供する。

【解決手段】スプリットゲート構造の不揮発性半導体記憶装置において、ホットホール注入を行う場合、時間変化しない交点を用いて、ホットホール注入動作のベリファイを行う。これにより、経時変化を考えずに消去状態の検証をすることができる。

また、複数回のパルス電圧または多段ステップ電圧をゲート部に印加することにより書き込みまたは書き込み/消去を行う。

(もっと読む)

半導体装置の駆動方法

【課題】電荷蓄積層での電子の蓄積または放出が十分でない場合に、不揮発性メモリ素子に保持された記憶状態の正誤を判定し、誤ったデータを読み出すことによる不良を低減する。

【解決手段】メモリセル領域104と、テスト領域105と、を含む半導体記憶回路103と、制御回路と、を有し、制御回路は、メモリセルへのデータの書き込み、第1の領域105Aへの第1の記憶状態の書き込み、または第2の領域105Bへの第2の記憶状態の書き込みを行うための第1の動作を行い、第1の領域及び第2の領域からの第1の記憶状態または第2の記憶状態の読み出しを行うための第2の動作を行い、メモリセルからのデータの読み出しを行うための第3の動作を行い、第2の動作において、第1の領域からの読み出しが第1の記憶状態であるか、または第2の領域からの読み出しが第2の記憶状態であるかに応じて、第3の動作の正誤を判定する。

(もっと読む)

不揮発性半導体記憶装置及びその書き込み方法

【課題】書き込み速度の遅れや書き込み不良等を招くことなく、更なる微細化を実現し得る不揮発性半導体記憶装置及びその書き込み方法を提供する。

【解決手段】選択トランジスタとメモリセルトランジスタとを有する複数のメモリセルと、選択トランジスタのドレインに接続されたビット線と、メモリセルトランジスタのコントロールゲートに接続された第1のワード線と、選択トランジスタのセレクトゲートに接続された第2のワード線と、メモリセルトランジスタのソースに接続されたソース線とを有し、第1の電圧Vstep(1)を第1のワード線に印加しながら、ソース線に第2の電圧Vpulse(1)をパルス状に印加する第1のステップと、第1の電圧より高い第3の電圧Vstep(2)を第1のワード線に印加しながら、ソース線に第2の電圧より低い第4の電圧Vpulse(2)をパルス状に印加する第2のステップとを少なくとも実行することにより、メモリセルに情報を書き込む。

(もっと読む)

1 - 20 / 139

[ Back to top ]